本文主要是介绍【头歌·计组·自己动手画CPU】五、单总线CPU设计(理论版) 【计算机硬件系统设计】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

🕺作者: 主页

我的专栏 C语言从0到1 探秘C++ 数据结构从0到1 探秘Linux 😘欢迎 ❤️关注 👍点赞 🙌收藏 ✍️留言

文章目录

- 一、课程设计目的

- 二、课程设计内容

- 三、课程设计步骤

- 四、课程设计总结

一、课程设计目的

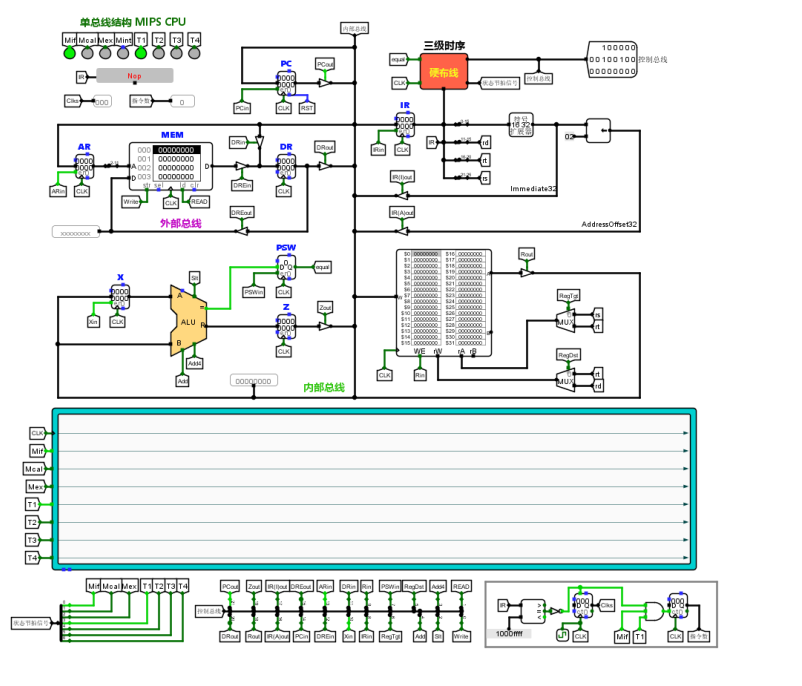

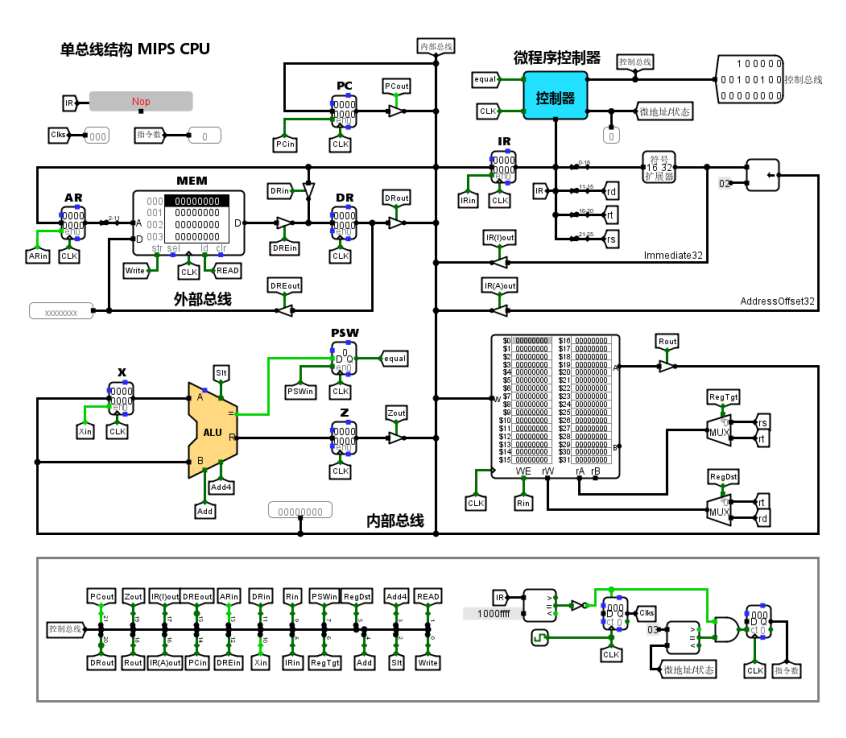

利用经典的单总线结构运行MIPS程序,可以设计传统三级时序硬布线控制器,也可以设计现代时序硬布线控制器和微程序控制器,可以为不同的时序系统增加中断处理机制。

二、课程设计内容

- 单总线CPU设计(定长指令周期3级时序)(HUST)

- MIPS指令译码器设计

1.1.实验目的

理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号。

- 定长指令周期—时序发生器FSM设计

2.1.实验目的

理解传统三级时序系统中时序发生器的基本原理,能设计定长指令周期的时序发生器状态机以及输出函数。

- 定长指令周期–时序发生器输出

3.1.实验目的

理解传统三级时序系统中时序发生器的基本原理,能设计定长指令周期的时序发生器状态机以及输出函数。

- 硬布线控制器组合逻辑单元

4.1. 实验目的

理解传统三级时序系统中硬布线控制器的设计原理,能设计硬布线控制器组合逻辑单元。

- 定长指令周期-硬布线控制器设计

5.1.实验目的

理解传统三级时序系统中硬布线控制器的设计原理。

- 定长指令周期–单总线CPU设计

6.1. 实验目的

理解单总线结构CPU基本原理,能设计定长指令周期的三级时序系统,是的MIPS程序能在单总线结构上运行,最终能运行简单的排序程序sort-5.hex。

- 单总线CPU设计(变长指令周期3级时序(HUST)

- MIPS指令译码器设计

- 实验目的

理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号。

- 变长指令周期–时序发生器FSM设计

- 实验目的

理解传统三级时序系统中时序发生器的基本原理,能设计变长指令周期的时序发生器状态机以及输出函数。

- 变长指令周期–时序发生器输出函数设计

- 实验目的

理解传统三级时序系统中时序发生器的基本原理,能设计变长指令周期的时序发生器状态机以及输出函数。

- 硬布线控制器组合逻辑单元

- 实验目的

理解传统三级时序系统中硬布线控制器的设计原理,能设计硬布线控制器组合逻辑单元。

- 变长指令周期-硬布线控制器设计

- 实验目的

理解传统三级时序系统中硬布线控制器的设计原理。

- 变长指令周期—单总线CPU设计

- 实验目的

理解单总线结构CPU基本原理,能设计定长指令周期的三级时序系统,使得MIPS程序能在单总线结构上运行,最终能运行简单的排序程序sort-5.hex。

- 单总线CPU设计(现代时序)HUST)

- MIPS指令译码器设计

- 实验目的

理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号

- 单总线CPU微程序入口查找逻辑

- 实验目的

理解传统三级时序系统中时序发生器的基本原理,学生能设计定长指令周期的时序发生器状态机以及输出函数

- 单总线CPU微程序条件判别测试逻辑

- 实验目的

理解传统三级时序系统中时序发生器的基本原理,学生能设计定长指令周期的时序发生器状态机以及输出函数

- 单总线CPU微程序控制器设计

- 实验目的

理解传统三级时序系统中硬布线控制器的设计原理,学生能设计硬布线控制器组合逻辑单元

- 采用微程序的单总线CPU设计

- 实验目的

理解传统三级时序系统中硬布线控制器的设计原理

- 现代时序硬布线控制器状态机设计

- 实验目的

理解单总线结构CPU基本原理,能设计定长指令周期的三级时序系统,是的MIPS程序能在单总线结构上运行,最终能运行简单的排序程序sort-5.hex

- 现代时序硬布线控制器设计

- 实验目的

理解现代时序系统中硬布线控制器的设计原理。

三、课程设计步骤

- 单总线CPU设计(定长指令周期3级时序)(HUST)

- MIPS指令译码器设计

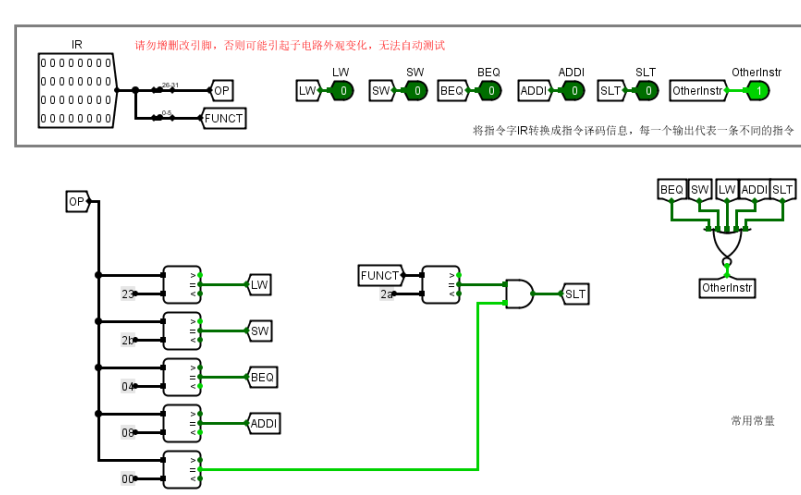

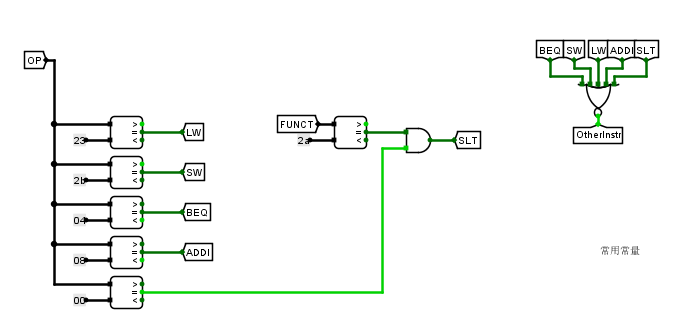

- 原理

MIPS指令译码器的设计可以分为以下几个步骤:

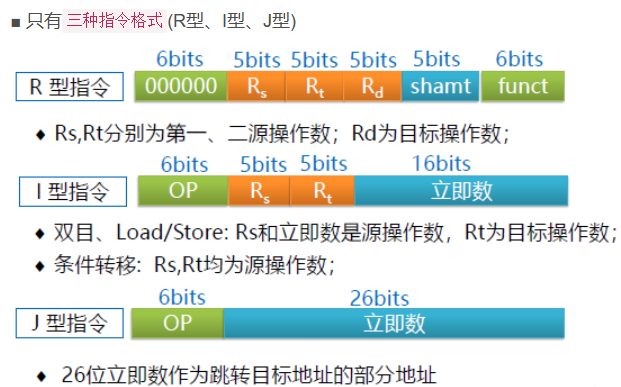

确定指令格式:MIPS指令有三种格式,分别是R型、I型和J型,每种格式有不同的字段和位数,因此需要先确定指令的格式。

分析指令字段:根据指令格式,确定各个字段的含义和作用。例如,R型指令中包含操作码、源操作数寄存器编号、目的操作数寄存器编号、移位量等字段,需要分析这些字段的位数和作用。

实现指令译码逻辑:根据指令格式和字段信息,设计指令译码逻辑。这一步通常需要使用逻辑门、多路选择器、寄存器等组件来实现。

测试和验证:设计完指令译码器后,需要进行测试和验证,确保它能够正确地解析各种指令,并将指令字段正确地传递到后续的执行阶段。

格式如下:

此实验需要mips知道操作码op对应的值,下面给出实验中用到的mips指令的op码的值

| Mips指令 | Op码 |

|---|---|

| LW | 100011(23) |

| SW | 101011(2b) |

| ADDI | 001000(08) |

| BEQ | 000100(04) |

| [SLT](https://so.csdn.net/so/search?q=SLT&spm=1001.2101.3001.7020" \t "https://blog.csdn.net/qq_62325622/article/details/_blank) | 000000(00) |

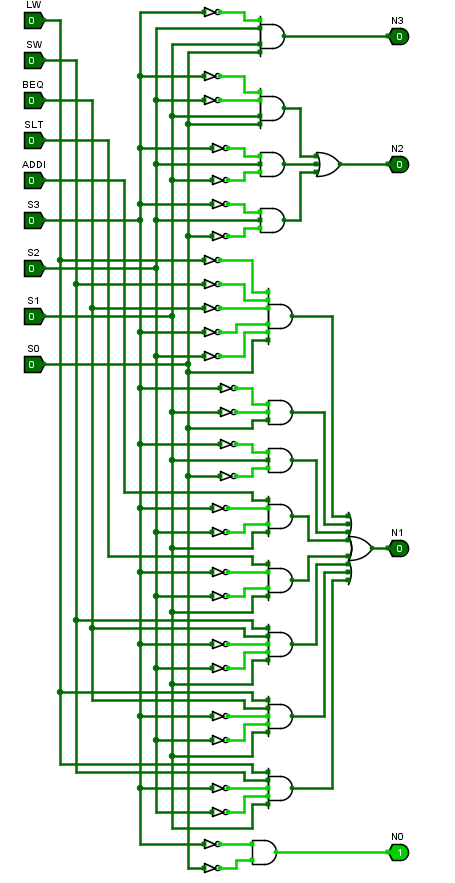

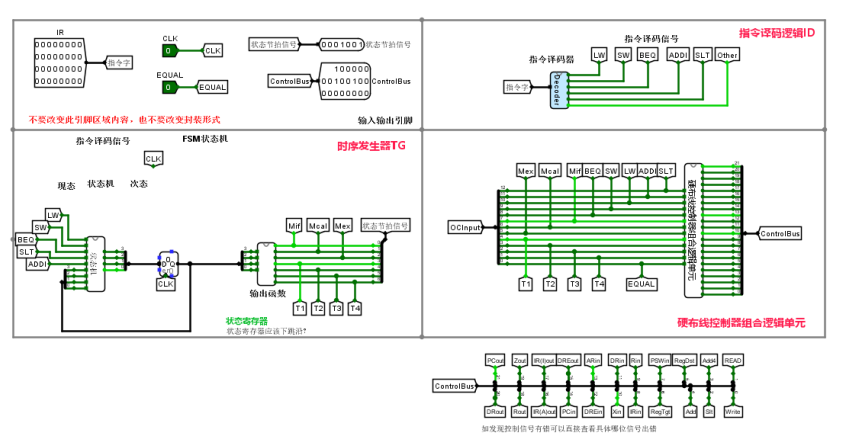

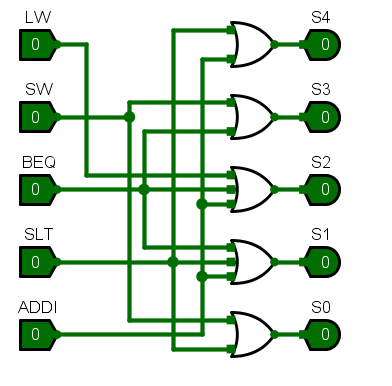

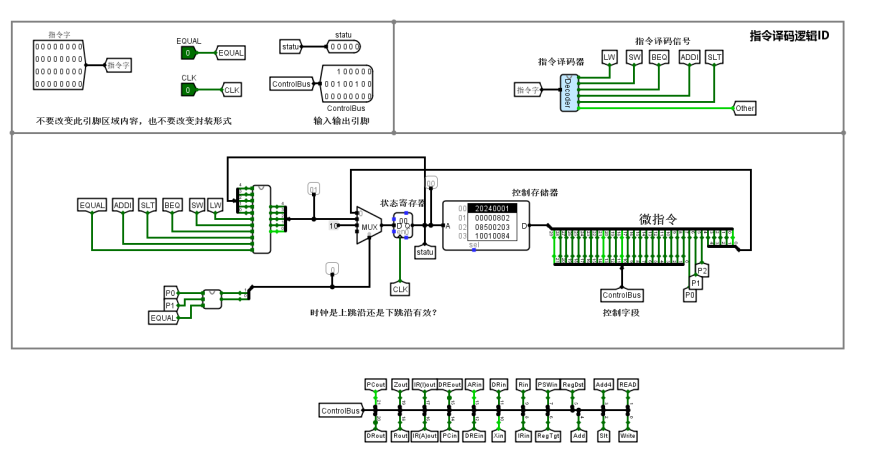

- 接线图

- 定长指令周期—时序发生器FSM设计

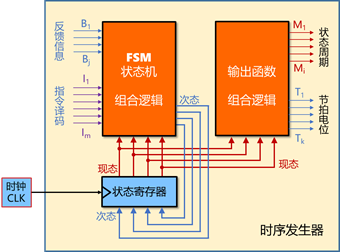

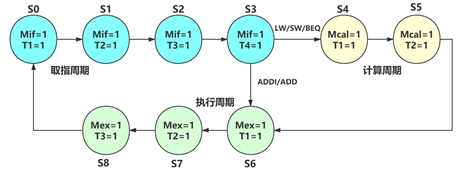

2.1.原理

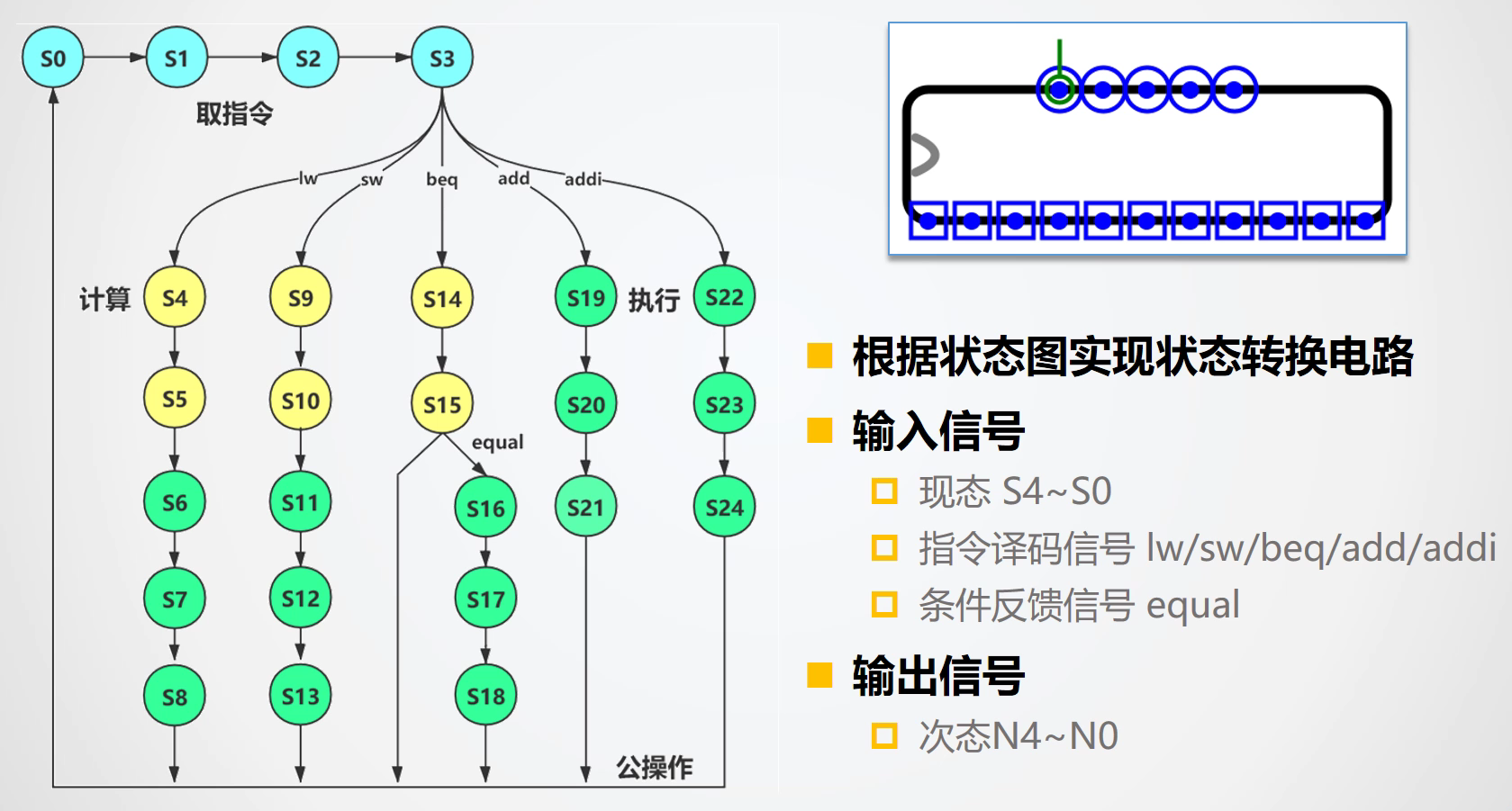

状态机负责现态与次态的转换,输出函数根据当前状态生成状态周期电位和节拍周期电位。

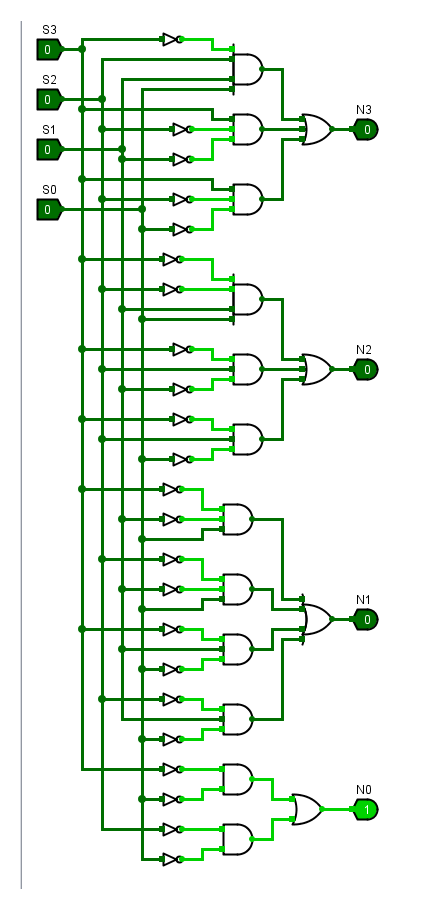

单总线结构中如果采用定长指令周期,所有MIPS指令都需要3个机器周期,每个机器周期4个时钟节拍,一共需要12个状态,状态图如下:

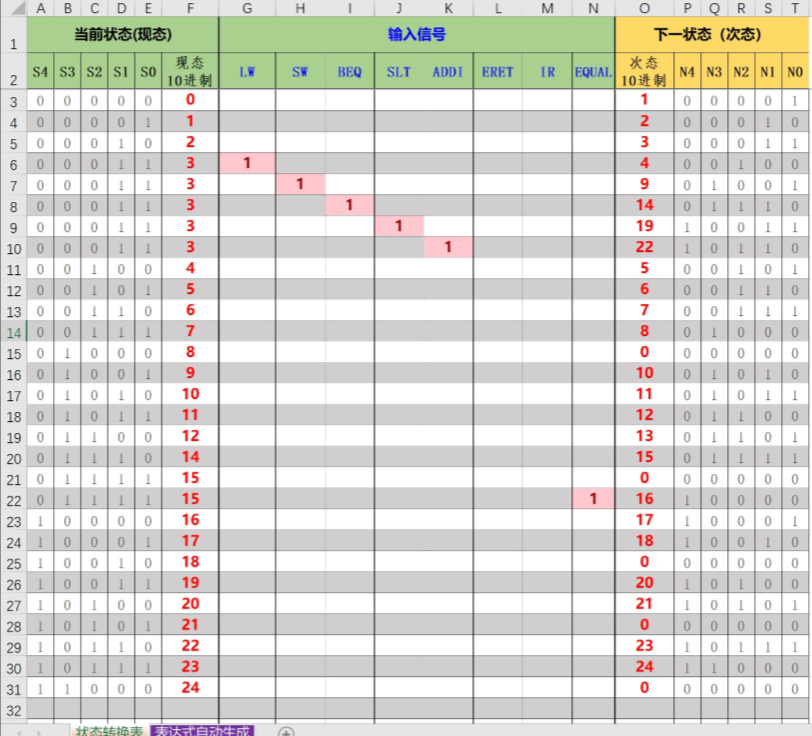

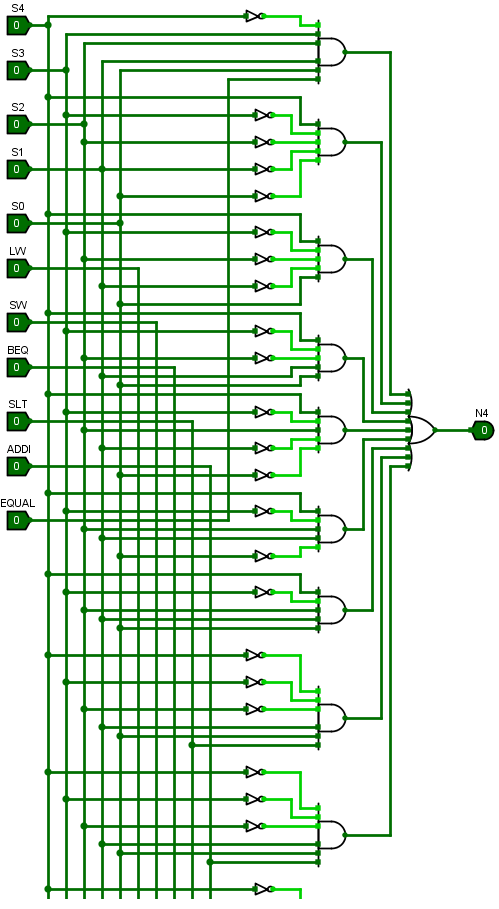

按状态图填写相应的excel表,自动生成次态逻辑表达式后,即可在logisim中自动生成该电路。

2.2. 接线图

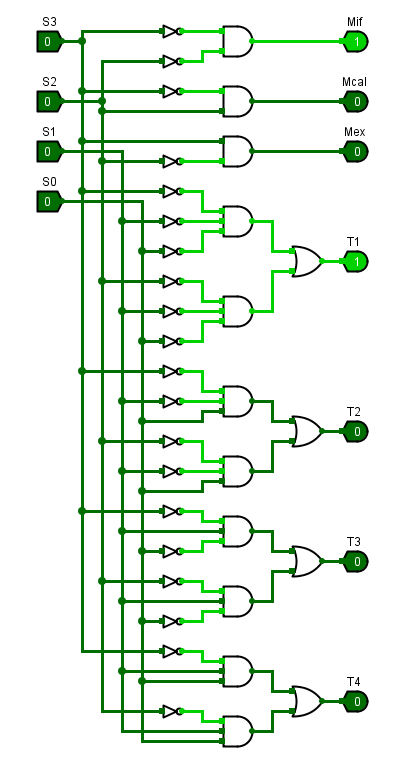

- 定长指令周期–时序发生器输出

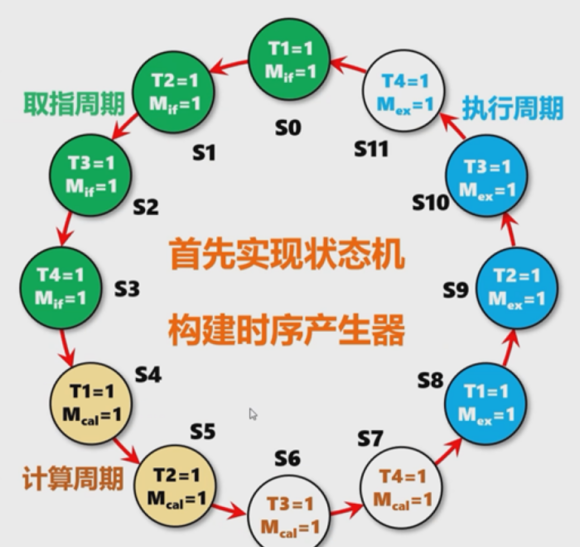

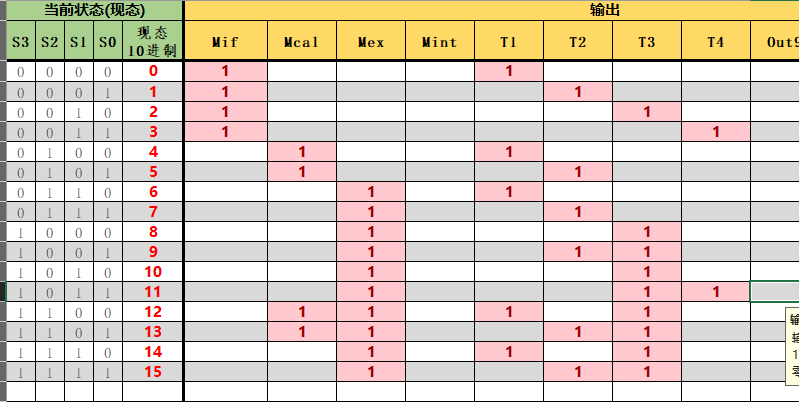

3.1.原理

根据状态转化图我们可以容易的填写输出函数的真值表,得到生成函数自动生成输出函数的逻辑电路。

3.2.接线图

- 硬布线控制器组合逻辑单元

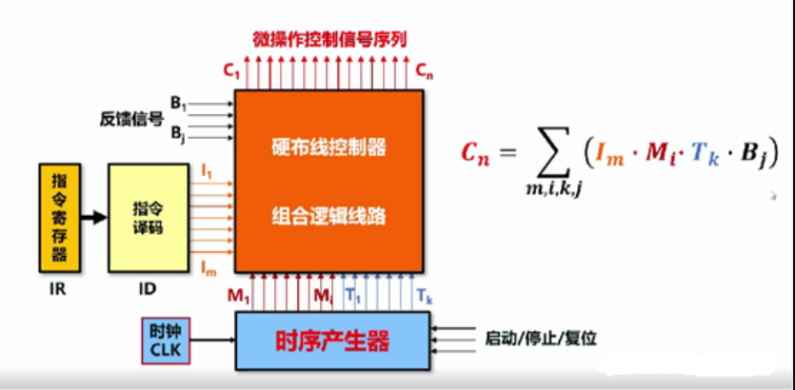

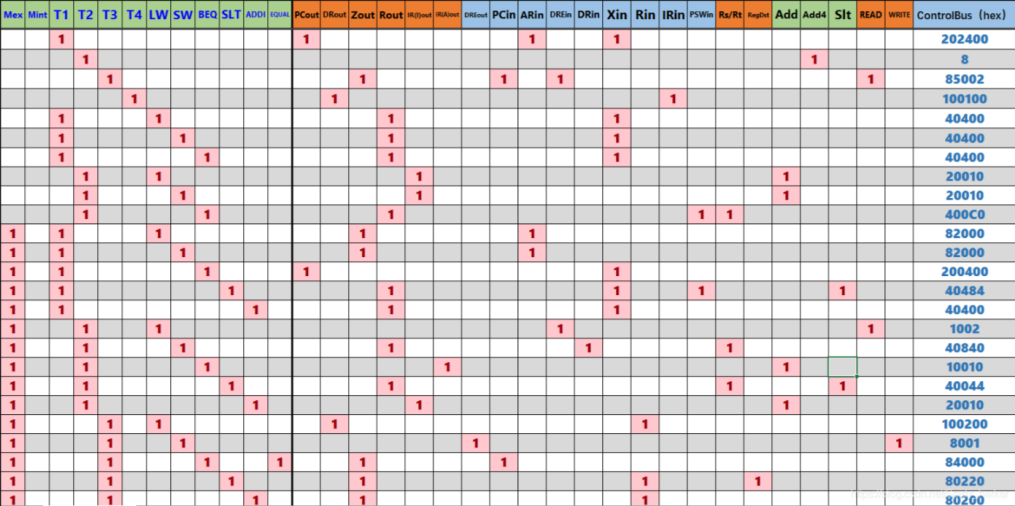

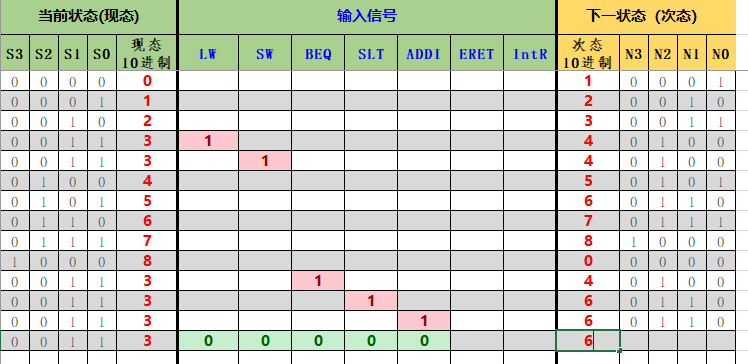

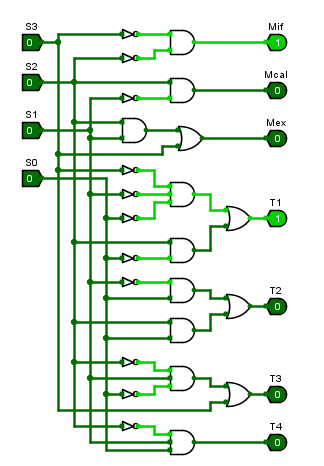

4.1. 原理

在硬布线控制器中,每个控制信号c都对应一个指令,并且硬布线控制器可以看作是存储组件和逻辑电路的结合体。因此,我们只需要了解每个操作控制信号所产生的调节作用,就能够得到它们的逻辑表达式。

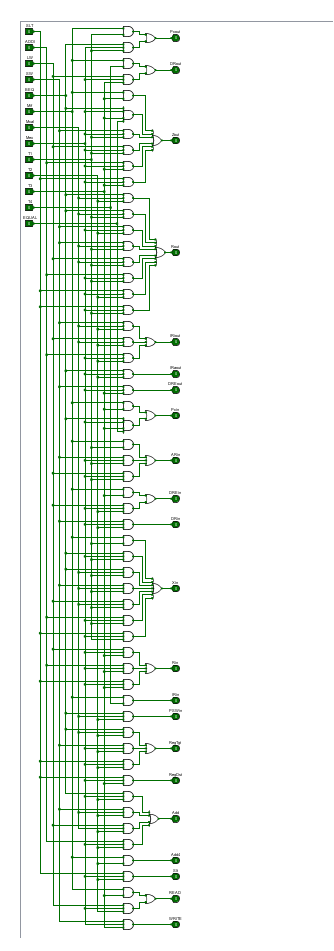

通过对数据通路进行分析,我们可以得到五条不同的指令,并且在取指令周期、计算周期和执行周期的不同阶段,会产生不同的控制信号。这些控制信号的产生条件需要综合考虑下面两个图表。对于所有的控制信号,需要推导出其逻辑表达式,同时在设计 CPU 电路时对控制点的逻辑表达式进行化简。

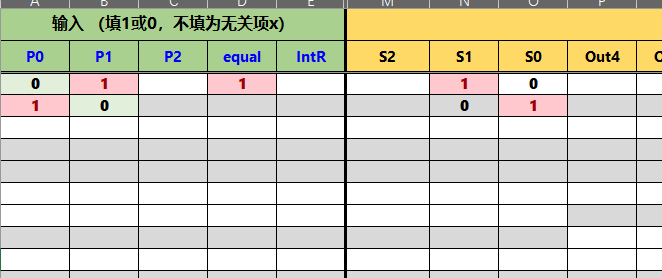

可以列出所有微操作信号的产生条件,填写下面的excel表格,自动生成逻辑表达式,然后再Logisim中自动生成电路。

4.2. 接线图

- 定长指令周期-硬布线控制器设计

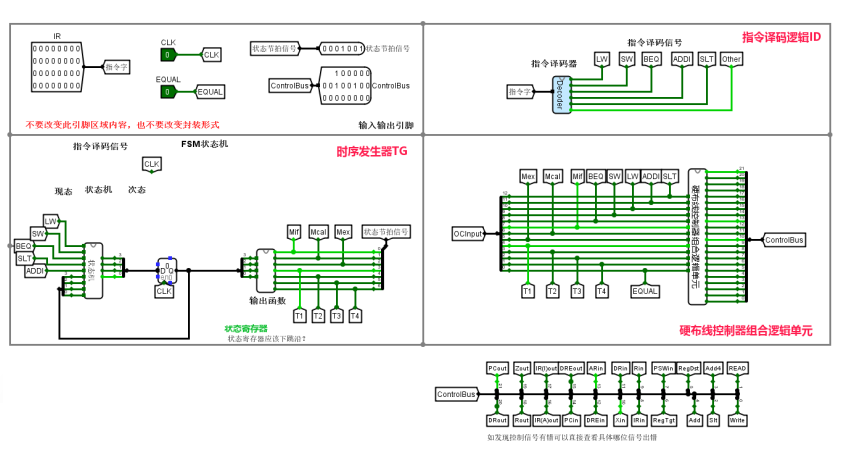

5.1. 原理

该实验是对前面的组装

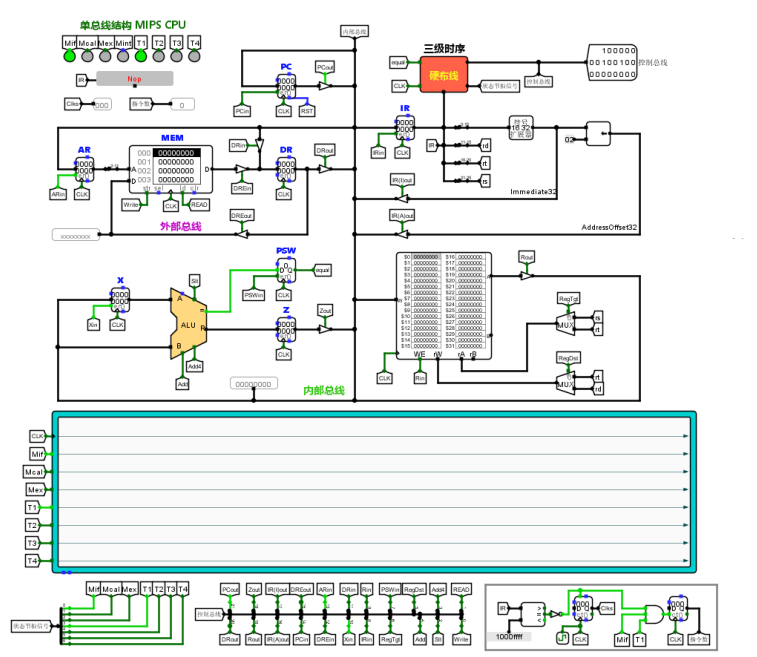

5.2. 接线图

- 定长指令周期–单总线CPU设计

6.1. 原理

该实验是对前面实验的全部封装

6.2. 接线图

- 单总线CPU设计(变长指令周期3级时序(HUST))

- MIPS指令译码器设计

- 原理

MIPS指令译码器设计和定长是一样的。

- 接线图

- 变长指令周期–时序发生器FSM设计

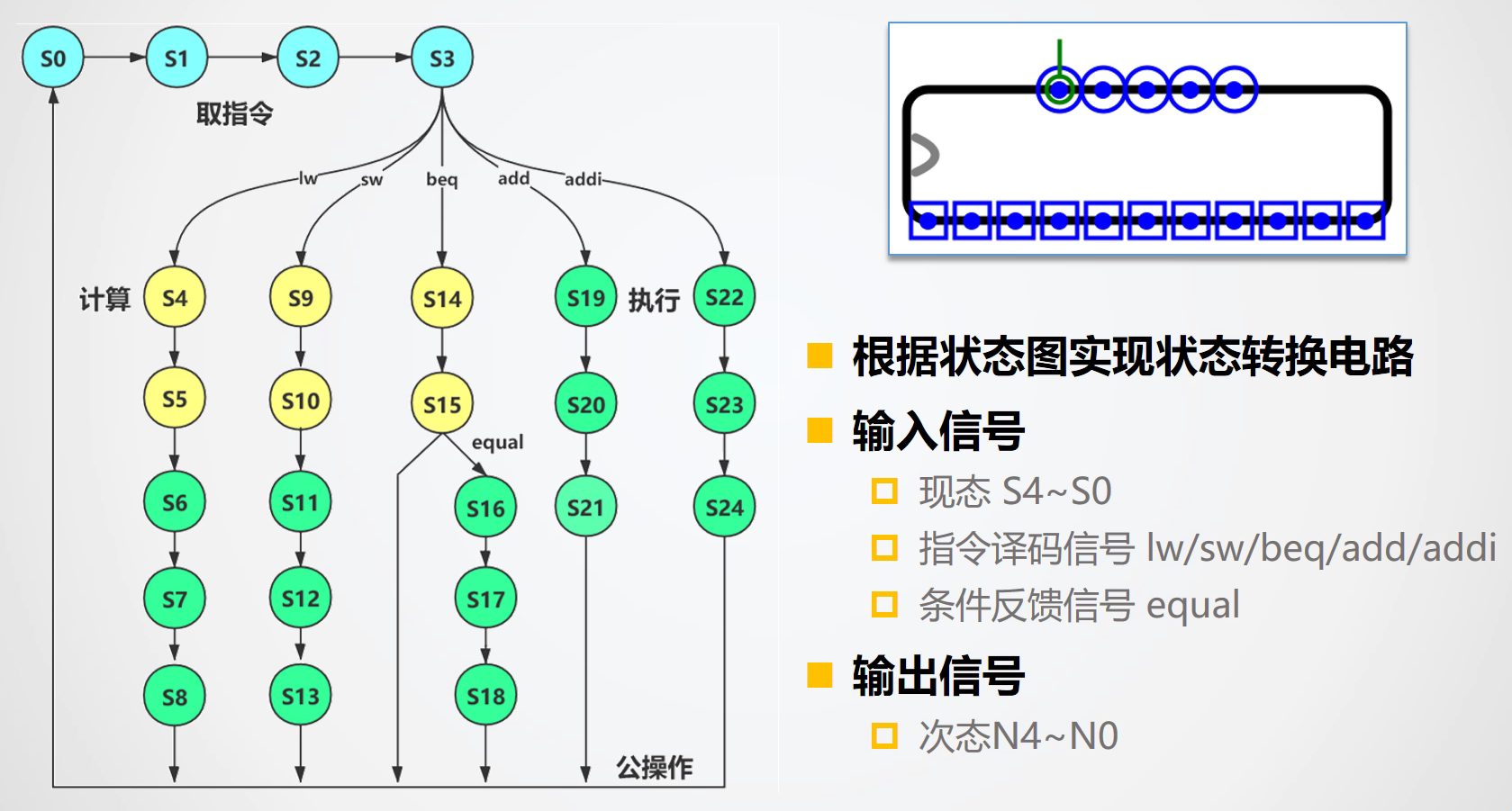

- 原理

变长的状态机和定长的状态机有区别,要根据变长的状态机的状态转化图,填写execl表格自动生成电路。

-

接线图

-

变长指令周期–时序发生器输出函数

- 原理

根据上面实验的状态转化图我们可以填写出execl表格。

- 接线图

- 硬布线控制器组合逻辑单元

- 原理

变长的控制器和变长的控制器是一样的,因此可以使用定长的硬布线控制器组合逻辑单元的execl表直接来生成函数,然后自动生成电路图。

- 接线图

- 变长指令周期-硬布线控制器设计

- 原理

对前面实验的组装

- 接线图

- 变长指令周期—单总线CPU设计

- 原理

对前面实验的封装与测试。

- 接线图

- 单总线CPU设计(现代时序)HUST)

- MIPS指令译码器设计

和前面的实验一样不再赘述。

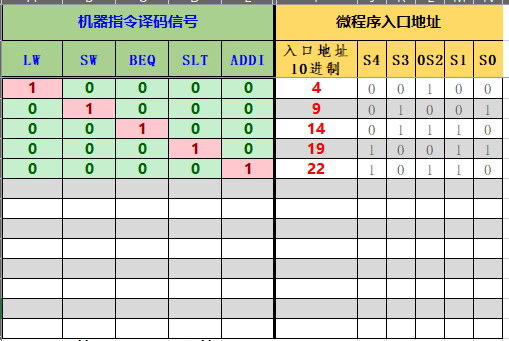

- 单总线CPU微程序入口查找逻辑

- 原理

微程序的入口需要通过状态转化图来知道,并且需要我们把微程序入口的值填写到execl表中,采用自动生成逻辑表达式自动生成电路。

- 接线图

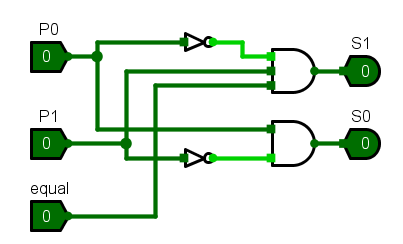

- 单总线CPU微程序条件判别测试逻辑

- 原理

和前面类似,使用EXCEL自动生成即可。

- 接线图

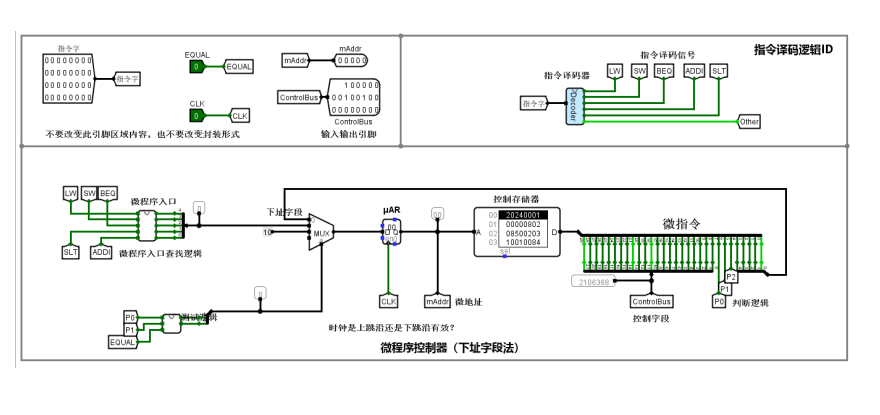

- 单总线CPU微程序控制器设计

- 原理

和前面类似,使用EXCEL自动生成即可。

- 接线图

- 采用微程序的单总线CPU设计

- 原理

对前面实验的测试

- 接线图

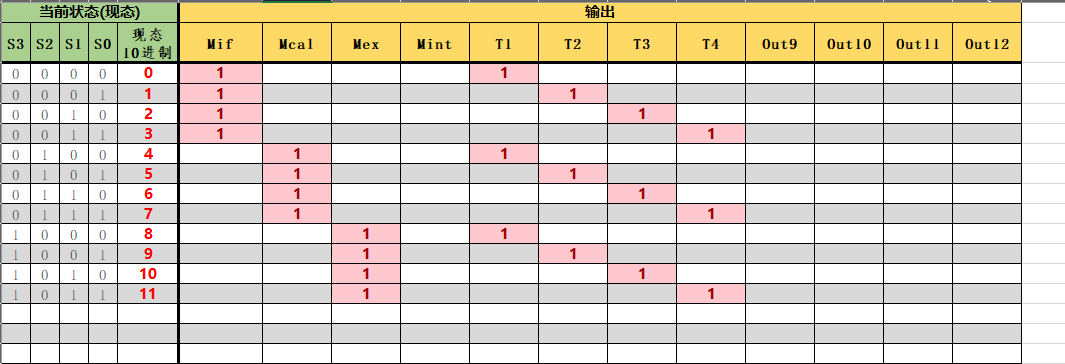

- 现代时序硬布线控制器状态机设计

- 原理

根据状态转换图填写EXCEL表

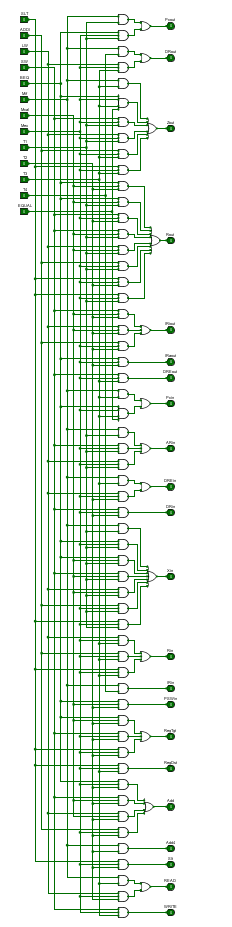

- 接线图(部分)

- 现代时序硬布线控制器设计

- 原理

依据前一个实验进行逻辑连接。

- 接线图

四、课程设计总结

通过本课程设计,我们深入了解了单总线结构运行MIPS程序的原理和设计过程,包括传统三级时序系统、变长指令周期系统以及现代时序系统。具体内容包括MIPS指令译码器设计、定长/变长指令周期的时序发生器设计、硬布线控制器的组合逻辑单元设计、单总线CPU的设计等。

在定长指令周期3级时序系统方面,我们学会了设计MIPS指令译码器、时序发生器FSM和输出函数、硬布线控制器组合逻辑单元等,最终实现了单总线CPU能在定长指令周期内运行MIPS程序的目标。

在变长指令周期3级时序系统方面,我们针对变长指令周期的特点,设计了相应的时序发生器和硬布线控制器,使得单总线CPU能够适应不同长度的指令周期。

在现代时序系统方面,我们学习了微程序控制器的设计原理,并将其应用在单总线CPU设计中,实现了采用微程序的单总线CPU设计以及现代时序硬布线控制器的状态机设计和硬布线控制器的设计。

通过这些实验,我们对计算机体系结构的实际设计有了更深入的理解,同时也提高了我们的设计能力和实践能力。这些知识和技能对我们今后在计算机体系结构领域的学习和工作都将大有裨益。

这篇关于【头歌·计组·自己动手画CPU】五、单总线CPU设计(理论版) 【计算机硬件系统设计】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!