本文主要是介绍用于先进封装技术的Si蚀刻,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在本文中讲述了HARSE的工艺条件,其产生超过3微米/分钟的蚀刻速率和控制良好的、高度各向异性的蚀刻轮廓,还将成为展示先进封装技术的潜在应用示例。

在用作阳极硅衬底的 “光学工作台”示意图中显示,混合技术集成和封装使用第二光刻步骤,可以在硅中蚀刻出相对于激光器的精确深度和位置的沟槽,以便被动对准光纤,此外可以蚀刻晶片通孔,用作正面控制和/或驱动电路的光学或电学互连。

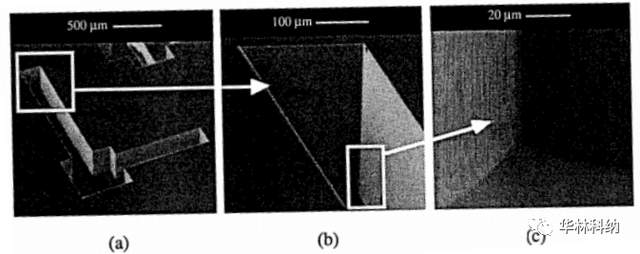

图1

图1展示了其中的几个概念,其中一张扫描电镜照片显示了同时蚀刻到约250微米深度的硅特征,在图1a中,中心正方形或器件定位器”可用于精确定位混合结构,而沟槽特征可用于电互连或延伸到光纤的晶片边缘,在图1b和1c中,高倍扫描电镜显微照片显示了侧壁和场的高各向异性和平滑蚀刻形态。

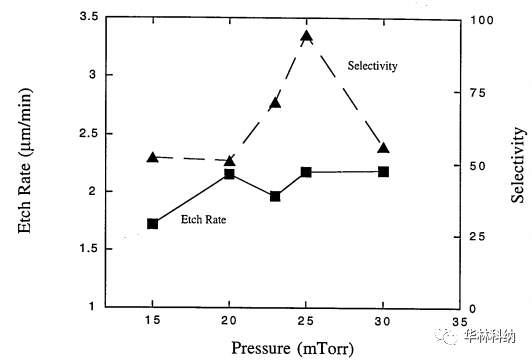

图2

为了实现被动自对准、蚀刻研究了作为室压、阴极射频功率和ICP源功率的函数的参数,在图2中,当阴极射频功率、等离子体源功率和气体流量保持不变时,硅蚀刻速率和硅对光刻胶的蚀刻选择性显示为压力的函数,通常导致离子能量和等离子体密度的变化,这强烈影响蚀刻性能,随着压力增加,表明在较低压力下反应物受限,这种相对于抗蚀剂的高蚀刻选择性使得能够以高纵横比进行深硅蚀刻(通常> 600 微米)。

蚀刻特性通常表现出对离子能量和等离子体的强烈依赖密度&#x

这篇关于用于先进封装技术的Si蚀刻的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!