本文主要是介绍【头歌·计组·自己动手画CPU】三、存储系统设计(HUST)(理论版) 【计算机硬件系统设计】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

🕺作者: 主页

我的专栏 C语言从0到1 探秘C++ 数据结构从0到1 探秘Linux 😘欢迎 ❤️关注 👍点赞 🙌收藏 ✍️留言

文章目录

- 一、课程设计目的

- 二、课程设计内容

- 三、课程设计步骤

- 四、课程设计总结

一、课程设计目的

理解计算机中重要部件—存储器,要求掌握存储扩展的基本方法,能设计 MIPS 寄存器堆、MIPS RAM 存储器。能够利用所学习的 cache 的基本原理设计直接相联、全相联,组相联映射的硬件cache。

二、课程设计内容

- 汉字字库存储芯片扩展实验

- 实验目的

理解存储系统进行位扩展、字扩展的基本原理,能利用相关原理解决实验中汉字字库的存储扩展问题,并能够使用正确的字库数据填充

- MIPS寄存器文件设计

- 实验目的

了解 MIPS 寄存器文件基本概念,进一步熟悉多路选择器、译码器、解复用器等 Logisim 组件的使用,并利用相关组件构建 MIPS 寄存器文件

- MIPS RAM设计

- 实验目的

理解主存地址基本概念,理解存储位扩展基本思想,并能利用相关原理构建能同时支持字节、半字、字访问的存储子系统

- 全相联cache设计

- 实验目的

掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制

- 直接相联cache设计

- 实验目的

掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制

- 4路组相连cache设计

- 实验目的

掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制

- 2路组相联cache设计

- 实验目的

掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制

三、课程设计步骤

- 汉字字库存储芯片扩展实验

- 原理

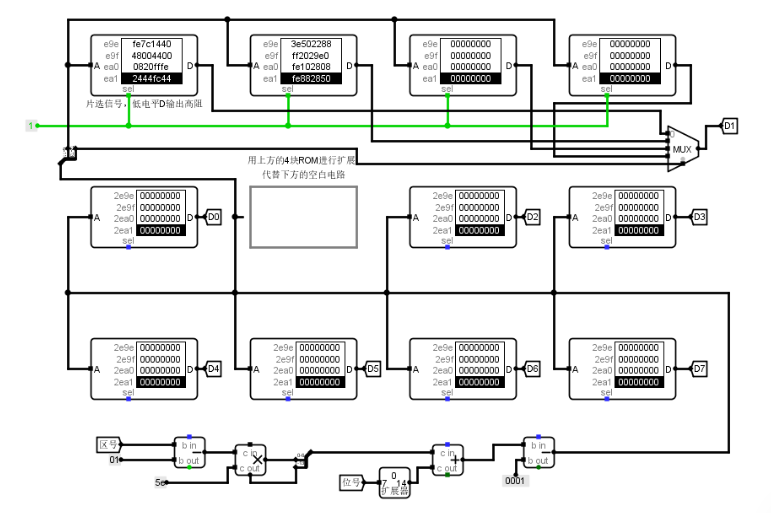

汉字点阵为1616位。需要8片16K32位ROM来存储点阵信息。我们需要用4片4K32位ROM代替其中一片16K32位ROM。4K需要12根地址线,16K需要14根地址线。所以高位多余的两位作为片选信号。我们需要一个数据选择器,来进行选择输出那一片ROM中的数据。再根据数据进行分析,数据的最后两位是选片区的。所以将最后两位直接输入到选择器选择短。最后将数据对应连接,即可得到电路。

- 接线图

- MIPS寄存器文件设计

- 原理

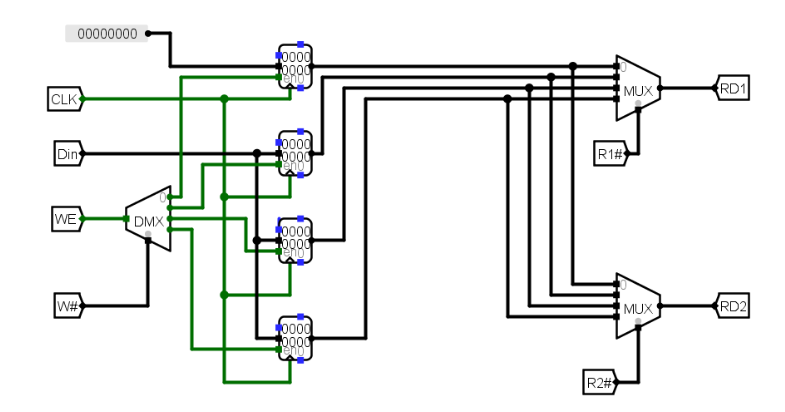

首先需要实现读取逻辑。假设R1#和R2#分别为两位宽的信号,并且设置数据选择器的位宽也为两位。这样,我们可以通过R1#和R2#来确定RD1和RD2,从而获取指定编号寄存器中的数值。

举例来说,当R1#为10时,表示选择2号寄存器。每个寄存器的输出都需要连接到相应的数据选择器的数据输入端。

接下来,我们要实现写入逻辑。系统总共有4个寄存器,因此我们可以使用译码器将W#转换为4个片选信号,分别表示0-3号寄存器。

当WE为1时,表示可以进行数据写入。因此,我们可以将片选信号和WE信号通过与门进行连接。

最后,将数据输入连接到相应的寄存器即可得到完整的电路。

另外,需要注意的是,0号寄存器需要保持为零,所以数据输入也需要设置为零。

- 接线图

-

MIPS RAM设计

- 原理

-

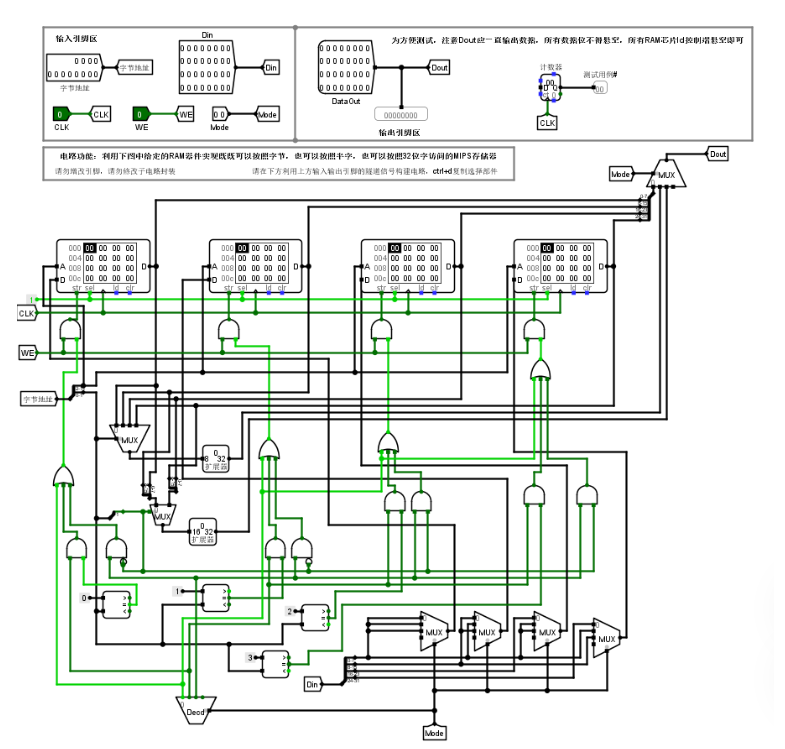

寄存器部分:使用4片8位寄存器,字节地址的低两位用于片选信号,其余位作为地址信号输入到寄存器中。

-

模式选择:使用模式选择信号Mode[1:0],通过译码器将模式信号转换为1位宽的信号,以便进行逻辑判断。

-

读取逻辑:

- 字读取:当模式为字读取时,直接输出全部数据。

- 半字读取:通过字节地址的第二低位确定输出哪个半字。

- 字节读取:通过字节地址的低两位确定输出哪个字节。

- 写入逻辑:

- 字写入:根据模式为字写入(00)

- 字节写入:根据模式为字节写入(01)

- 半字写入:根据模式为半字写入(10),字节地址的倒数第二位决定选择哪两个片选信号。

-

片选信号和存储器的写入信号进行连接,决定是否执行写入操作。

- 接线图

- 接线图

-

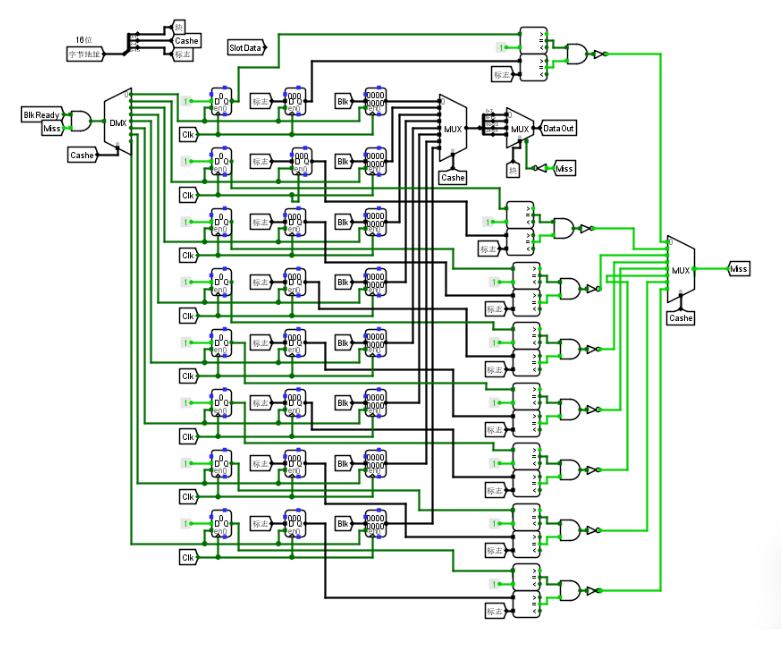

全相联cache设计

- 原理

全相联映射是一种Cache存储方式,其中主存中的任意一块可以存在于Cache中的任意位置。这种映射方式可以提高命中率,但也增加了硬件开销。

当CPU访问Cache中的某一字节时,它会给出一个9位地址。其中低5位表示该字节在Cache块的32个字节中的位置,高4位表示该字节属于主存16个块中的哪一个块。

由于Block在Cache中的位置是不确定的,CPU在查找数据时首先使用9位地址中的块序号的高4位与Cache中块的序号进行比对。因此,在Cache中存储数据时需要额外的空间来存储块的序号,即Tag位。有时还需要一些空间来表示Cache的有效位,以标记Cache中的内容是否有效。在初始化时,这些有效位可以被置为0,表示无效状态。

-

接线图

-

直接相联cache设计

- 原理

-

将主存地址拆分为标记(tag)、行索引(index)和字地址(offset)。

- 标记位长度为11位,用于表示主存块在Cache中的唯一标识。

- 行索引位长度为3位,用于选择Cache中的行。

- 字地址位长度为2位,用于选择Cache块中的字节。

- 读取逻辑:

- 使用行索引作为译码信号,获取对应行的选择信号。

- 每个Cache槽需要包含三个寄存器:valid(有效位)、tag(标记位)和data(数据位)。

- 使用三态门和行选择信号,将输入和输出数据分别与对应的寄存器连接。

- 当数据有效且标记位与主存地址的标记位相同时,表示命中。

- 写入逻辑:

- 当写入信号为真且未命中(即数据失效),需要将主存中的数据加载到Cache中。

- 首先使用行索引选择对应的行,然后更新标记位、数据位和有效位。

通过上述逻辑实现直接相联映射关系的Cache,可以进行读取和写入操作,并根据标记位和有效位判断是否命中。

- 接线图

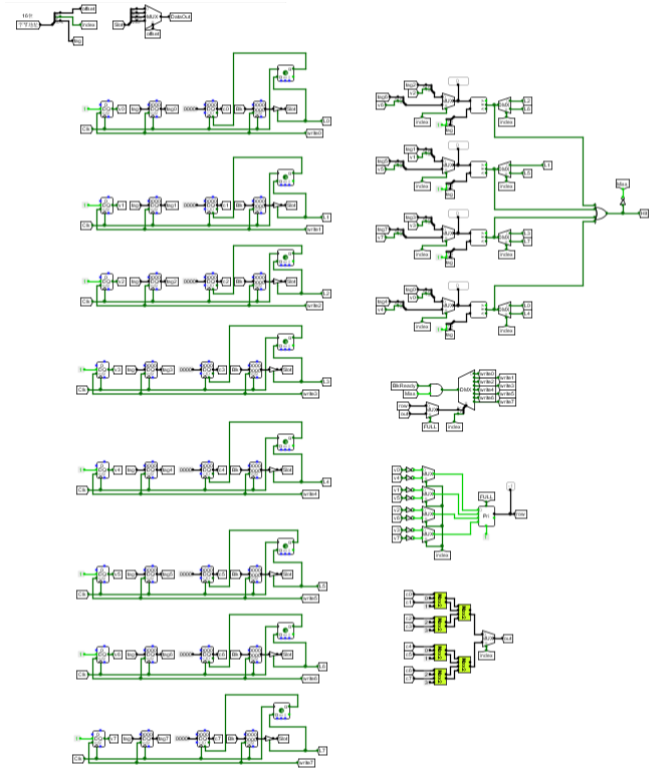

- 4路组相连cache设计

- 原理

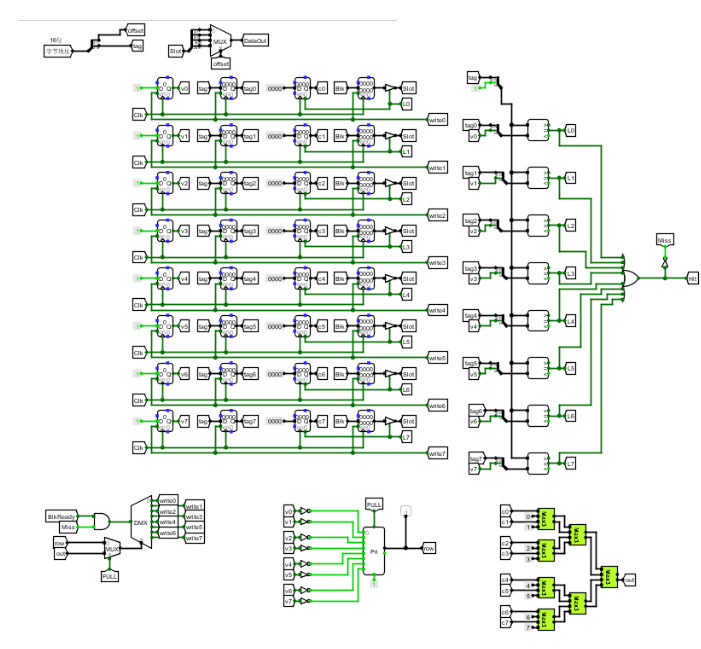

假设cache块大小为4W,共8行。字节地址为16位,分为tag、index和offset三个部分。由于块大小为4W,故offset为2位;cache共8行,一组有4行,因此index为1位;tag则为13位。

-

组索引译码器:组索引index字段经过组索引译码器生成若干组索引译码信号,这些信号用于选择对应的cache组。

-

数据输出控制:所有行数据输出采用三态门控制输出至系统数据总线。行译码信号L0-L7连接至对应的三态门控制端,只有组译码信号有效的组才会进行输出。这样可以确保同一时刻只有一行输出。

-

数据命中:当选中行的有效位为1且标记位与字节地址中的tag相同时,表示数据命中。命中信号hit控制最终的字选择多路选择器的使能端,确定具体输出选中行中哪一个字,从而实现数据的查找和访问。

-

数据未命中处理:Miss信号为1时表示数据未命中。当Miss信号和BlkReady信号同时为1时,结合组索引译码信号,通过淘汰计数器和LRU算法,决定替换组中的哪一行。然后对cache中相应行的valid信号、tag和data进行修改,最后取出正确数据。

- 接线图

- 接线图

-

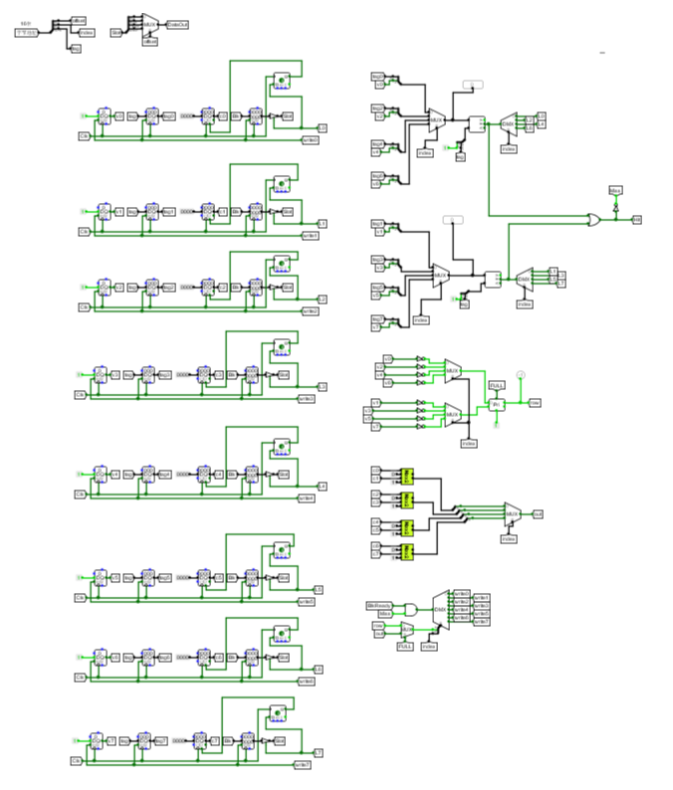

2路组相联cache设计

- 原理

原理和4路组相联cache相同

- 接线图

四、课程设计总结

通过这次课程设计,我深入理解了计算机中重要部件——存储器,并掌握了存储扩展的基本方法。我学会了设计MIPS寄存器堆和MIPS RAM存储器,并能利用所学的基本原理设计直接相联、全相联和组相联映射的硬件cache。

在汉字字库存储芯片扩展实验中,我理解了存储系统进行位扩展和字扩展的基本原理,并成功解决了汉字字库的存储扩展问题。我学会了使用正确的字库数据填充,并将数据选择器与ROM进行连接,以实现对应数据的输出。

在MIPS寄存器文件设计中,我进一步熟悉了多路选择器、译码器和解复用器等Logisim组件的使用。我成功构建了MIPS寄存器文件,并实现了读取逻辑和写入逻辑。我了解到0号寄存器需要保持为零,因此在数据输入时也需要设置为零。

在MIPS RAM设计中,我理解了主存地址的基本概念和存储位扩展的基本思想。我成功构建了能同时支持字节、半字和字访问的存储子系统。我学会了使用模式选择信号和译码器进行逻辑判断,并根据不同的模式进行读取和写入操作。

在全相联cache设计中,我掌握了cache实现的三个关键技术:数据查找、地址映射和替换算法。我熟悉了译码器、多路选择器和寄存器的使用,并能根据不同的映射策略在Logisim平台中用数字逻辑电路实现cache机制。我学会了使用标记位、行索引和字地址来确定数据的位置和命中情况。

在直接相联cache设计中,我进一步加深了对cache实现的三个关键技术的理解。我学会了将主存地址拆分为标记、行索引和字地址,并通过译码器和有效位对数据进行选择和输出。我了解到需要设置有效位、标记位和数据位,并根据标记位和有效位判断是否命中。

在4路组相联cache设计和2路组相联cache设计中,我进一步加深了对cache实现的三个关键技术的掌握。我熟悉了组索引译码器和数据输出控制的使用,并了解到数据命中和数据未命中处理的过程。我学会了使用替换算法和LRU算法,以确定替换组中的哪一行,并对cache中的相关信号进行修改和取出正确数据。

通过这次课程设计,我不仅提高了对存储器的理解和设计能力,还加深了对数字逻辑电路的认识。我将继续努力学习,提高自己在计算机硬件方面的知识和技能。

这篇关于【头歌·计组·自己动手画CPU】三、存储系统设计(HUST)(理论版) 【计算机硬件系统设计】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!