本文主要是介绍FPGA 检测0101序列 修正罗杰主编教材中5.2.3二段式报错,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

基于 源代码书上

module Detector2 (

input Sin, CP, nCR, //声明输入

output reg Out //声明输出

);

reg [1:0] Current_state, Next_state; //声明状态触发器变量

parameter S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11;

//时序逻辑: 描述状态转换

always @(pose<e CP, nege<e nCR)

begin

if (~nCR) Current_state<=S0; //异步清零

else

Current_state<=Next_state; //在CP上升沿触发器状态翻转

end

//组合逻辑:描述下一状态和输出

always @(Current_state, Sin)

begin

Next_state=2'bxx;

Out=1'b 0;

case(Current_state) //根据当前状态和状态转换条件进彳

S0: begin Out=1'b0; Next_state=(Sin==1)? S0 : S1; end

S1: begin Out=1'b0; Next_state=(Sin==1)? S2 : S1;end

S2: begin Out=1'b0; Next_state=(Sin==1)? S0 : S3; end

S3: if (Sin==1)

begin Out=1'b1; Next_state=S2; end

else

begin Out =1'b0; Next_state=S1; end

endcase

end

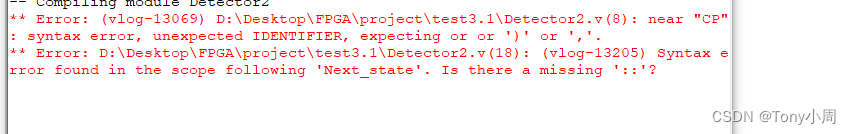

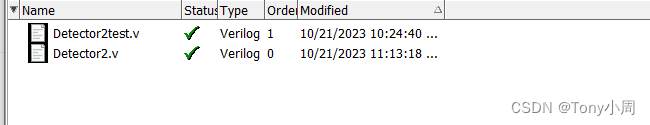

endmodule出现两个报错,

开始以为是编码问题,使用vs code 打开后取出非法字符

编译还是出现错误,教材未对always @(pose<e CP, nege<e nCR)

begin改行代码做出解释,所以应该是何=和第一种编写方式一样才对。

修改后

module Detector2 (Sin,nCR,CP,Out);

input Sin,nCR,CP;//声明输入

output reg Out;//声明输出reg [1:0] Current_state, Next_state;//声明状态触发器变量

parameter S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11;

//时序逻辑: 描述状态转换

always @(posedge CP, negedge nCR)

begin

if (~nCR) Current_state<=S0;

else

Current_state<=Next_state;//在CP上升沿触发器状态翻转

end

//组合逻辑:描述下一状态和输出

always @(Current_state, Sin)

begin

Next_state=2'bxx;

Out=1'b 0;

case(Current_state)

S0: begin Out=1'b0; Next_state=(Sin==1)? S0 : S1; end

S1: begin Out=1'b0; Next_state=(Sin==1)? S2 : S1; end

S2: begin Out=1'b0; Next_state=(Sin==1)? S0 : S3; end

S3: if (Sin==1)

begin Out=1'b1; Next_state=S2; end

else

begin Out =1'b0; Next_state=S1; end

endcase

end

endmodule,果然,

这篇关于FPGA 检测0101序列 修正罗杰主编教材中5.2.3二段式报错的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!