本文主要是介绍FPGA的配置方式PS——Passive serial,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

FPGA的配置方式PS——Passive serial

FPGA的配置方式,很多种,前一段时间主要用了一下PS——Passive serial,被动串行的加载方式。在这个模式下,FPGA被动的等待配置起始信号,然后接受配置文件,完成配置。即每次在FPGA上电时,由外部器件完成FPGA的配置。

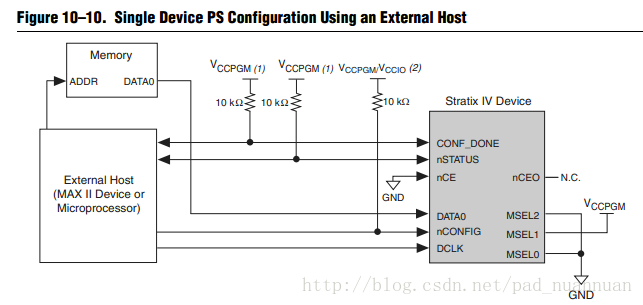

这个方式的实现(或者说选择),是由FPGA的硬件连接来完成的,硬件连接如下图:

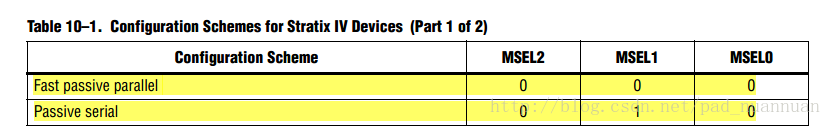

MSEL这组信号决定了FPGA的配置方式:

(根据官方文档的说明,这两个管脚不要连接在微控制器上或者其他的器件上来做下载方式的选择,也不要使用电阻上拉或下拉,最好直接连载在VCC或者GND上)

可以看到上图选择了Passive serial的配置方式,除了MSEL这组信号,其他的信的如下:

nCEo:这个可以理解为nCE out用于给多片FPGA配置时使用;

CONF_DONE:这个信号信号是一个开路输出,也就是上面为甚都是上拉,一句话就是这个信号就是当FPGA配置完成后,告诉主控,我配置结束了。

nSTATUS:一样,开路输出,需上拉,这个信号反应FPGA的配置过程状态的信号,一会儿看时序图。

nCE:chip select,用来选择当前的FPGA,如果有多片,这个就有用了;

DATA0,DCLK:俩个配置过程正真干活的信号,数据和时钟,DCLK上升沿,FPGA采集DATA0的信号,至于放哪里,FPGA内部自己搞定了;多说一句,FPGA中,除了LE,PLL等用户可用的逻辑,其实还是有一些他的控制逻辑的,就比如这个控制PS,还有控制AS;

nCONFIG:这个信号很重要,由主控告诉FPGA,要开始配置了,即产生起始信号。

上图就完成了整个PS配置的硬件连接,其中External Host选择MAX II系列的CPLD,memory选择一片flash;

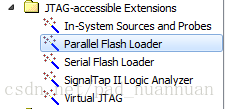

CPLD作为配置FPGA的Host,需要一段代码逻辑来完成这个功能,例如需要读取flash、需要给flash加载FPGA的配置文件、需要配置FPGA。那这不是苦大仇深了,还要研究flash的读写时序和FPGA的配置时序?统统不用,Altera提供了这个方案,肯定是有相关的IP,在Altera的IP核生成工具里面选择Parallel Flash Loader这个IP,然后对IP做一些简答的配置,如下图:

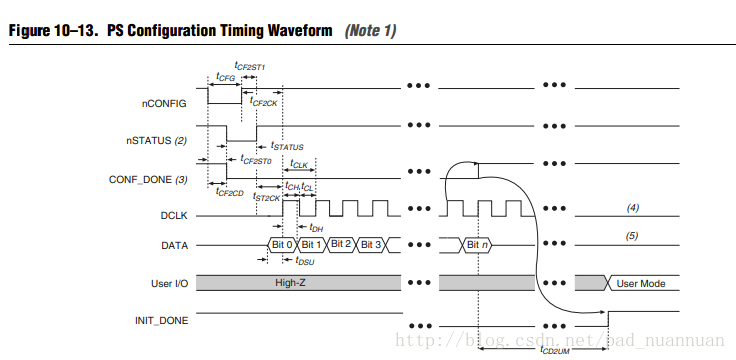

虽然都由IP核完成,但是最少得明白IP核干了些神马工作,IP对FPGA的配置时序如下,至于关键的时序是多少,我们并不去实现这个IP,所以不用了解,但是他们在相应的器件手册中都有:

从上图中,我们可以看到整个配置过程如下:

1、 nCONFIG在被CPLD配置为低电平后,一个上升沿表示要开始配置FPGA;

2、 上升沿结束后,FPGA的nSTATUS由低电平被FPGA释放,有外部的电阻上拉为高电平,告诉CPLD,FPGA已经接受到其实信号,开始接受数据;

3、 接下来,DCLK和DATA开始传输信号;

4、 当传输完成之后,FPGA将CONF_DONE释放,并有外部电阻上拉,表示配置结束;

5、 FPGA内部完成初始化,进如user mode ,开始执行用户的逻辑。

这篇关于FPGA的配置方式PS——Passive serial的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!