本文主要是介绍task2:Verilog编写的设计模块在模块内部直接调用task,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Verilog编写的设计模块在模块内部直接调用task

- 1,概念

- 2,模块设计

- 2.1,RTL设计

- 2.2,tb测试代码

- 2.3,sim仿真输出

参考文献:

1,练习七-在Verilog中使用任务task

1,概念

在模块设计中,直接在内部模块使用调用

task任务,然后通过task任务中的变量(包括:输入和输出)来调用task任务的工作。

2,模块设计

2.1,RTL设计

//

// 针对一个 task 来写一个模块调用

module mod_use_task( // 加法器

input i_rst,

input i_clk,

input [1:0] a,

input [1:0] b,output reg [2:0] out

);reg [1:0] cnt;

reg [7:0] d;always@(posedge i_clk or negedge i_rst) beginif(!i_rst) beginout <= 2'd0;cnt <= 2'd0;endelse begin // adder.out <= a + b;cnt <= cnt + 1'd1;endend// output results.

always@(cnt) beginif(cnt == 2'd3)rest(cnt, d);else stop_work(cnt, d);

endtask rest;

input [1:0] cnt1; // task 从 mod 模块 中 输入.

output [7:0] d1; d1 = 8'd100;

endtasktask stop_work;

input cnt2;

output [7:0] d2;d2 = 8'b0;

endtaskendmodule

2.2,tb测试代码

// 测试信号

module tb_mod_use_task;

reg i_rst;

reg i_clk;

reg [1:0] a;

reg [1:0] b;wire [2:0] out;always #10 i_clk = ~i_clk; // T = 20.initial begin

i_clk = 1'b1;

i_rst = 1'b0;#40;

i_rst = 1'b1;

endinitial begin

a = 2'd0;

b = 2'd0;#20

a = 2'd1;

b = 2'd2;#10

a = 2'd2;

b = 2'd3;#40

a = 2'd3;

b = 2'd3;// repeat(10) begin

// a = {$random}%2;

// b = {$random}%2;

// endendmod_use_task u1_mod_use_task(

.i_clk (i_clk ),

.i_rst (i_rst ),

.a (a ),

.b (b ),.out (out )

);endmodule

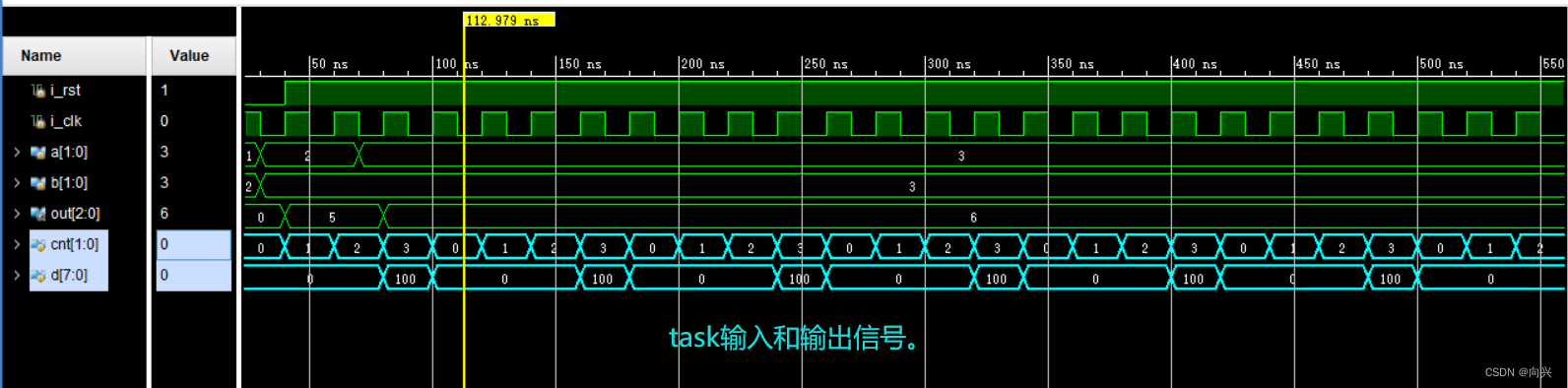

2.3,sim仿真输出

这篇关于task2:Verilog编写的设计模块在模块内部直接调用task的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!