本文主要是介绍【总结】蒙特卡洛仿真-Vos,dc失调电压的影响。(CMRR),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

比较器参数之Offset voltage(Vos)

概念

1、失调电压

运放的输入失调电压包含两部分:系统失调和随机失调。

前者来自于电路设计,即使电路中所有匹配器件都相同也会存在;为系统失调。(如电路钳位带来的。)

后者来自于应匹配器件的失配。

失调参数的计算:

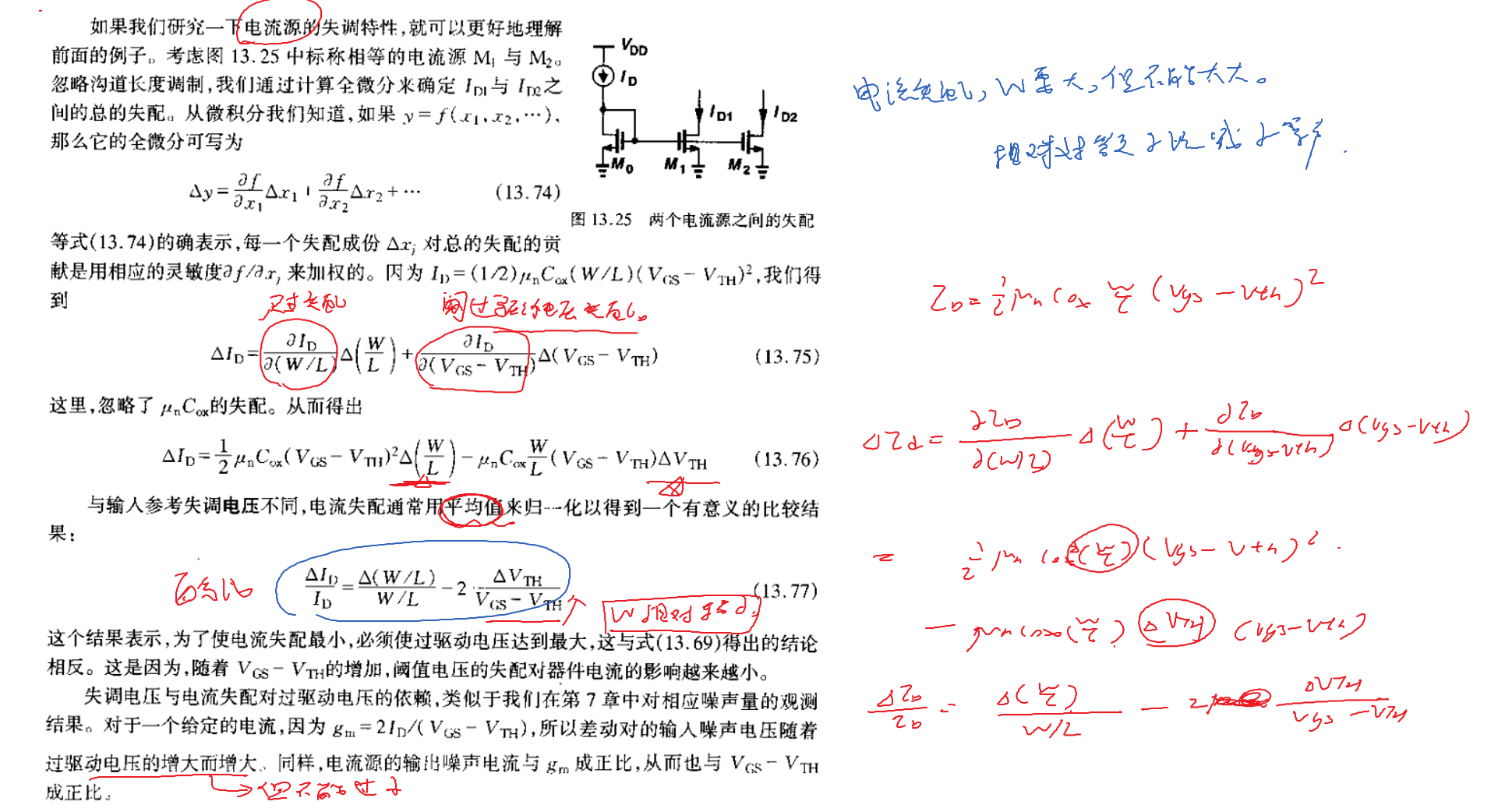

差动对的失调电压的计算:

电流镜失配的计算:

指标:共模抑制比

1、当不匹配发生时,共模输出会造成差模干扰,影响输出!失配造成的共模干扰。

2、有限尾电流源的抑制效果,可能在高频时共模的干扰不再受到抑制,会产生大的变化进而影响输出电压摆幅。因此共模干扰在高频时不能过大。或者低于一定值。

比较器的时延仿真

仿真

2、蒙特卡洛仿真

根据蒙特卡洛仿真来分析由于器件失配引起的系统输出的影响。工艺偏差造成电路的失配。

没有仿蒙特卡洛,是看不到失调的,因为我们搭的理想电路是没有失配。你说MC仿出来的失调均值是300uV左右,sigma在几mV,这是正常的。我们理想状态下,就是要失调的均值接近0啊。至于simga,是一个置信区间的概念,就是mean +/- 3sigma的这个值,才是真实的失调电压会出现的范围,必须要保证这个范围是你可以接受的才行。比如你接受的失调范围是2mV,若仿出来的3sigma范围超过了2mV,那你就必须调电路把失调降下来。

3、仿真流程

①一开始与直流仿真类似,即添加直流仿真类型并加入仿真项(Vref) ,之后添加仿真模型文件,在 setup 的 Model Library 中添加 mc_lib 文件,打上勾点击“ok”即可。

②在添加完仿真文件后,回到仿真界面开始设置蒙特卡洛仿真标准,

“statistical Variation”为需要仿真的类型如:工艺(process)、失配(Mismatch)以及全部(All);

仿真次数(Numbers of Points):一般做基准源仿真的次数设置为“100 到 300 次”;

将“Save Process Data”、“Save Mismatch Data”、“Save Data to Allow Family Plots”勾选好。

Starting Run #默认为1即可。如果勾选Append to Previous ScalarData以集合几次Monte carlo仿真数据,则该数据不能和己仿真的次数重叠,例如第一次分析设置Starting Run #为1,仿真次数为100,则第二次仿真分析该值至少为101。

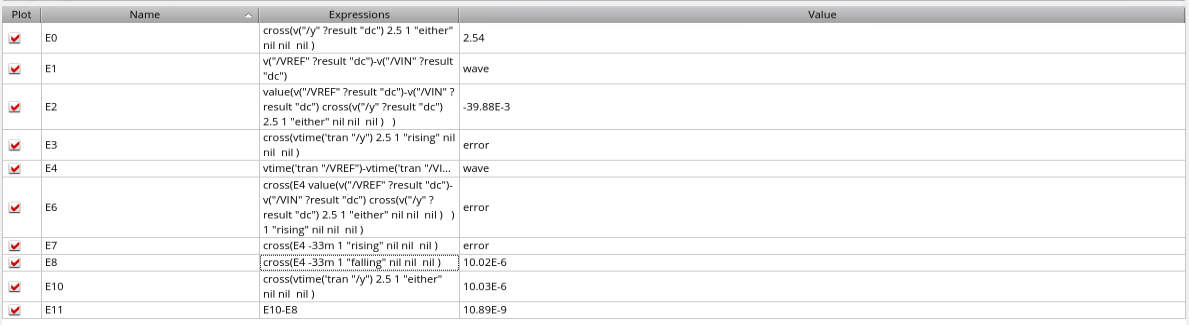

Output可从菜单Output->Retrieve Outputs获取ADE界面的输出,也可以自己输入添加。

4、可应用范围。

====================================================

直流失调概念

失配是器件之间的关系。

1、 运放的输入失调电压包含两部分:系统失调和随机失调。

前者来自于电路设计,即使电路中所有匹配器件都相同也会存在;为系统失调。(如电路钳位带来的。)

后者来自于应匹配器件的失配。对于untrimmed的单片运放, MOS输入管的典型失调值为1-20mV。(包含工艺以及)

在实际的匹配器件中,沟道长度选取为相等,沟道宽度选取为成比例,因为沟道宽度较大从而对工艺偏差的灵敏度较小些。

注:输入输出失调是一种直流静态工作点偏移,但是CMRR关注的是变化,是一个交流指标。

2、失调电压仿真 -蒙特卡洛仿真

首先你要明白失调电压的来历,失调电压是由内部电路的失配造成的。输出失调,是输入为0,但是因为内部管子的失配,会在输出端产生一个压差。为了消除这个失调,要在输入端加上一个电压,使输出信号变成0,这样才是补偿了失调。同样的,等效的输入失调你可以理解为是输出的失调电压,除以了电路本身的增益,才得到了输入失调。所以增益大一些是好的。

如果你没有仿蒙特卡洛,是看不到失调的,因为我们搭的理想电路是没有失配。你说MC仿出来的失调均值是300uV左右,sigma在几mV,这是正常的。我们理想状态下,就是要失调的均值接近0啊。至于simga,是一个置信区间的概念,就是mean +/- 3sigma的这个值,才是真实的失调电压会出现的范围,必须要保证这个范围是你可以接受的才行。比如你接受的失调范围是2mV,若仿出来的3sigma范围超过了2mV,那你就必须调电路把失调降下来。

理解mc的那个标准差的含义了,我还有个疑问就是,我们仿真运放失调时接成单位增益运放去仿真是吗?那么我们要在输入端给一个合适的共模电平,然后看输出变化了多少?是这么仿的吗,共模电平不能取 0吧,取0时pmos输入对管线性区了

参考:动态比较器失调仿真

概念

总结:

工艺偏差造成电路的失配。

根据蒙特卡洛仿真来分析由于器件失配引起的系统输出的影响。

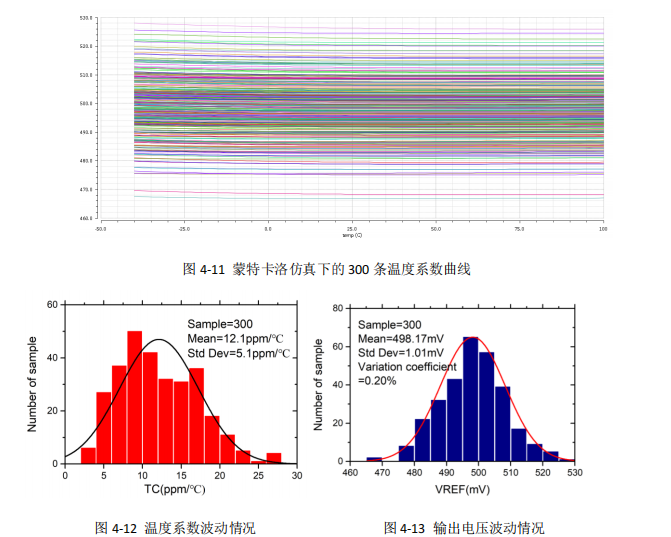

由于每一个晶体管的制作都存在尺寸之间的偏差,从而影响了电流镜的镜像电流精准度,即产生了失配电流,此外工艺的偏差也会造成每个晶体管的阈值电压的大小不一,进而影响了输出电压的大小,为此需要进行蒙特卡洛仿真来观测电路受工艺及失配的影响,对结果分析并进行进一步优化。

一开始与直流仿真类似,即添加直流仿真类型并加入仿真项(Vref) ,之后添加仿真模型文件,在 setup 的 Model Library 中添加 mc_lib 文件,打上勾点击“ok”即可。

在添加完仿真文件后,回到仿真界面开始设置蒙特卡洛仿真标准,“statistical Variation”为需要仿真的类型如工艺(process)、失配(Mismatch)以及全部(All);其次设计仿真次数(Numbers of Points),一般做基准源仿真的次数设置为“100 到 300 次”;

之后将“Save Process Data”、“Save Mismatch Data”、“Save Data to Allow Family Plots”勾选好。

按“ok”保存设置。再点击“Run simulation”

由上述设计可知:

整个设计得到的温度系数达到 10.0ppm/℃,而功耗接近 356nw,PSRR 为 6dB 且启动失败;

由于此设计是牺牲了功耗和电源抑制比而实现了电路的温度稳定性,然而我们仍需对各个性能参数进行折衷考虑,为此需要对设计做进一步修改:

1.线性调整率: LR 为469.7mV/V,输出电压受电源电压变化的影响很大,为此需要进一步优化,将 LR 降至 5mV/V 以内。

2.电源抑制比:仿真得到的电路的电源抑制比仅有 6dB,说明此电路对电源噪声的抗干扰能力特别的差,一般来说,电路的 PSRR 要达到 35dB 才算稳定,为此我们需要对电路结构做出改进从而来提高由于电路结构折中引起的低 PSRR 的情况;

3.启动情况:电路启动失败,需要设计启动电路使得当电路上电时,基准源电路中的电流镜能快速稳定到正常工作点,使得后续输出电压保持稳定。

蒙特卡洛仿真的3σ准则

[求助] 蒙特卡洛里的3倍sigma是什么意思

在仿真完电路后,除了需要跑PVT外,还需要跑一下蒙特卡洛仿真。

对于PVT,一般是有 ff,ss,tt,fnsp,snfp这些corner(ff Vth小,ss Vth大,fnsp则是fast nmos slow,pmos的意思,即nmos的vth小,pmos的Vth大)。而蒙特卡洛仿真就是跑的管子加入process和mismatch然后跑MC仿真。

如果PVT跑完没有什么问题的话,蒙卡仿真也没什么问题。

对于蒙特卡洛仿真,就是对管子进行随机误差仿真,这里通常会看一个叫3σ准则,即输出结果的误差范围。

3σ准则又叫拉依达准则,是指先假设一组检测数据只含有随机误差,对其进行计算处理得到标准偏差,按一定概率确定一个区间,认为凡超过这个区间的误差,就不属于随机误差而是粗大误差,含有该误差的数据应予以剔除。这种判别处理原理及方法仅局限于对正态或近似正态分布的样本数据处理,它是以测量次数充分大为前提的,当测量次数少的情形用准则剔除粗大误差是不够可靠的。因此,在测量次数较少的情况下,最好不要选用该准则。(源百度)

教程

我上传到网盘了http://pan.baidu.com/s/1nt3dSaX,这个是5141的仿真指导,基本步骤一样,

但是610的是你在ADE XL中,添加完test后,右键单击test那里,然后选择mentor carlo 分析进行相应的设置就行了,ic616是在ADE XL最上面仿真类型那里可以直接选择的,由于没开软件,没办法贴图,你实在摸不到门路,再回复我,给你贴图上去,记得其中输出的设置按照那个浙江大学的PPT设置就可以了,点型还是线型输出要选择好,点型出来就是直方图,线型出来就是很多条线。

1、环境配置

总:

①一开始与直流仿真类似,即添加直流仿真类型并加入仿真项(Vref) ,之后添加仿真模型文件,在 setup 的 Model Library 中添加 mc_lib 文件,打上勾点击“ok”即可。

确认工艺支持之后,就可以按照工艺库文档中所说的方法将蒙特卡洛仿真的相关文件添加进ADE L的Model Labraries 中去了,如下图。(大部分工艺库的添加方法为将原来所选的工艺角改为mc,有些也需要将一个新文件添加进去)

②在添加完仿真文件后,回到仿真界面开始设置蒙特卡洛仿真标准,

“statistical Variation”为需要仿真的类型如:工艺(process)、失配(Mismatch)以及全部(All);

③其次设计仿真次数(Numbers of Points):

一般做基准源仿真的次数设置为“100 到 300 次”;

④之后将“Save Process Data”、“Save Mismatch Data”、“Save Data to Allow Family Plots”勾选好。

按“ok”保存设置。再点击“Run simulation”

实例

1、单端运放的失调电压

使用 Cadence IC617 的蒙特卡洛仿真器仿真单端运放的失调电压

将运放置于单位反馈的状态,同时给运放一个满足其输入共模电压范围的合适的输入电压,并在输出接上一个负载电容,就搭建好了一个可以用来进行运放失调电压仿真的仿真电路了,如下图。此时运放输出电压与输入电压的差值就是运放的等效输入失调电压值。(如果运放的增益足够大的话)

2、二级运放的对称与失配

3、FLL的失调与失配对器件的影响

(1)只考虑了失配-mismatch

注:相当于只考虑了器件失配,

工艺角与失配

第六届集创赛——圣邦杯:高精度RC振荡器设计

1普通蒙特卡洛前仿真

电源电压范围:2.5V至5.5V

2附加

2附加

-

通过工艺角(TT,SS,FF,SF,FS)和只考虑器件失配(忽略工艺角)的蒙特卡洛仿真(计算4.5个Sigma偏差)得到输出时钟的频率范围,设计频率校准功能,进行单点频率校准,确保初始频率精度。

-

在工艺角(TT,SS,FF,SF,FS)和只考虑器件失配(忽略工艺角)的100次蒙特卡洛仿真下得到单点频率校准后的振荡器,启动时间、时钟信号占空比、频率随电源的变化,频率随温度的变化仍满足设计指标。

(2)工艺

process 为不同die之间偏差,mismatch为一个die中不同器件偏差,所以同样参数当然是process偏差大于mismatch。

4、带隙基准的失调电压对于基准电压的影响

可以明显看到,由于失调量的引入,使得输出量变化。

5、比较器的蒙特卡洛仿真失调电压仿真

[求助] 比较器的蒙特卡洛仿真失调电压

下面第一个文档是我针对传统的CML动态比较器 写的MC仿真总结剩下三个是我看过的一些关于动态比较器器失调仿真的相关paper 希望对大家有帮助。

做了一个比较器,想放输入失调电压,然后按照论坛里大佬的方法搭建的测试电路(【动态比较器 失调 offset 蒙特卡洛仿真】http://bbs.eetop.cn/thread-441803-1-3.html?_dsign=04d751c1),但是蒙特卡洛仿真的标准差几乎为零,对图像放大看也是有随机现象的。

库用的是smic018的,工艺角选用了mos_mc,具体设置见图。希望大佬能帮忙看看出了什么问题。

6、动态比较器失调电压仿真

参考:【M】eetop.cn_CML比较器失调仿真总结

## 7、死区充放电匹配性

## 7、死区充放电匹配性

由于鉴频鉴相器的工作特性, UP端或者DN端会产生一个极短的脉冲,理论上来说,这个脉冲应当越短越好。但是由于后级电荷泵中的开关工作速度有限,如果这个脉宽很短,开关不能完全打开就马上被关闭,在这一过程中泄露的电荷是很难被精确的控制的,解决这一问题的方法是适当延长这个脉宽,使得后级的开关能够同时打开,同时保证充放电两端完全匹配,以保证没有电荷泄露,这就是死区控制。在保证电荷泵能够完全打开的同时,应当使死区时间最小,这样可以减小电荷泵输出的电流噪声。

对死区电流充放电过程的仿真结果如图4.14,当电路工作于死区状态时,充放电电流可以保持严格的对称,利用仿真软件提供的积分工具,可以严格计算泄露到积分电容上的电荷。

对于理想电荷泵,死区时间内充放电支路应当完全匹配。如果充放电支路不能匹配,控制电压会产生波动,从而在输出端产生噪声。为了衡量死区内电流的影响,在死区时间内对电流进行平均,再用平均值差值衡量NP两端的匹配性能。

计算结果表明,本设计中,死区的引入相当于在全周期内引入1.2μA左右的充放电电流,而差分两端的平均失配电流为13.54nA,失配率为 1.125%,这样的失配是可以接受的。

7、失调电流

失配

这篇关于【总结】蒙特卡洛仿真-Vos,dc失调电压的影响。(CMRR)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!