本文主要是介绍详细解读QLC SSD无效编程问题-3,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

数据块大小Block Size对无效编程(Invalid Programming)比率的影响。研究范围内Block Size大小从128 Pages到2048 Pages不等。实验结果显示,随着块大小的增加,无效比率也呈现上升趋势,但增长速率较小。

这种现象的原因在于,每个Open Block的最后一部分页面可以立即进行精调编程而无需等待,因为这些页面在第一步粗调编程操作中没有后续页面。当缓存大小和Open Block数量固定时,单个Block中的Pages数量增多将会降低“无需等待”进行精调编程的Page数量,从而导致无效比率增加。然而,能够立即精调编程的页面仅占块内总页面的一小部分,因此即使块大小增大,无效比率也不会有显著变化。

在NAND闪存阵列中,同时等待精调编程的最大页面数量取决于可以并行写入Block(即Open Block)的数量。一般来说,等待第二步精调编程的同时进行的页面数量越多,无效比率就越高。

实验结果显示,在不同Open Block数量(从4个到64个)下,各种工作负载的无效比率表现各异。对于诸如Mds_0和Prxy_0这样的工作负载,随着Open Block数量的增加,无效比率显著上升。这是因为更多Open Block数量意味着在相同时间内写入单个开放块的数据量减少。然而,在其他一些工作负载上,当开放块数量从4个增加到16个时,无效比率也可能下降。

在NAND闪存系统中,LRU列表用于区分热数据和冷数据,从而决定数据应被放置到SLC还是QLC存储区域。相比于热数据,写入QLC的冷数据更新频率更低,对无效编程问题的敏感度也较低。

通过延长LRU列表的长度,更多的数据将被分类为热数据并随后写入SLC,这会导致无效比率显著下降。实验结果显示,在不同LRU长度(从32到512)下,对于大多数工作负载,随着LRU长度的增加,无效比率会降低。

值得注意的是,对于Proj_0工作负载,其无效比率略有上升。这是因为随着LRU长度的扩展,粗调编程页面所需的平均时间也会延长,这使得这些页面更有可能提前失效。

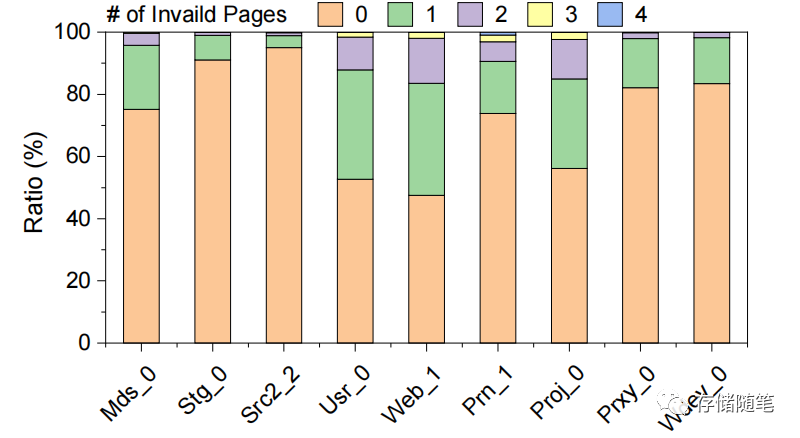

在3D QLC NAND闪存中,采用两步编程策略,一次会对四个页面同时进行编程。因此,在第二次编程步骤中,无效页面的数量可能从0到4不等。

实验结果显示,不同工作负载表现出不同的行为特征,但对于所有的工作负载来说,在第二次编程步骤中有相当大比例的WL存在无效页面。例如,在Web_1工作负载中,少于50%的WL在第二次编程时其四个页面都是有效的。而在遭受无效编程的WL中,大多数WL有一到两个页面在精细编程之前就被无效化了。然而,也有一些WL的情况是所有四个页面都被无效化。

这篇关于详细解读QLC SSD无效编程问题-3的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!