本文主要是介绍AXI总线协议---关键信号波形图分析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

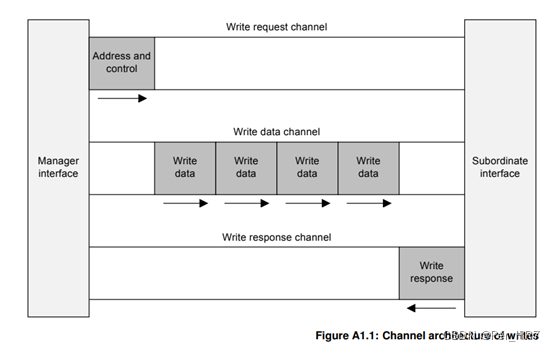

写过程协议图

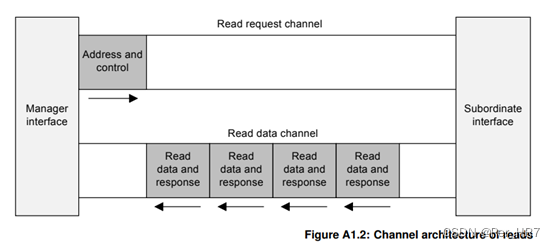

读过程协议图

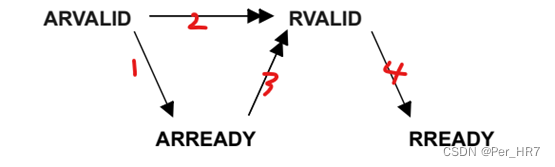

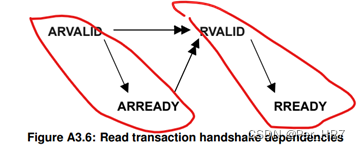

读协议执行顺序图

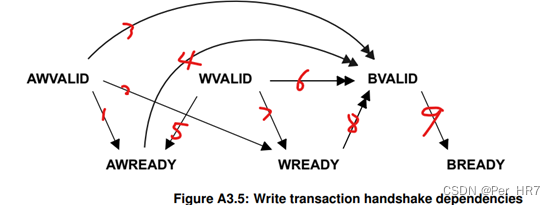

写协议顺序图

单箭头表示两个信号谁先有效无所谓,双箭头表示必须要等到前一个信号有效才能将后面的信号有效

如何体现协议图中的通道理解

- 声明:以上图均采用AMBA总线文档图

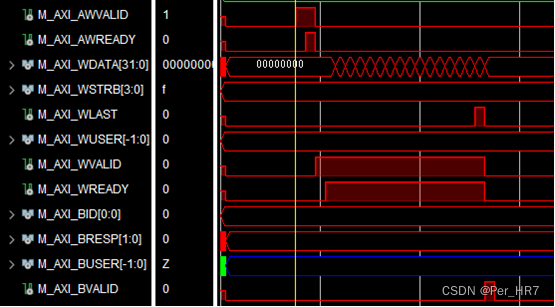

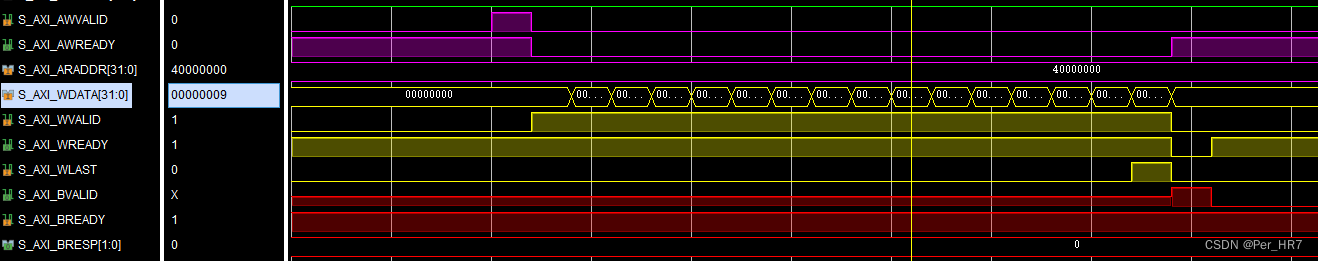

写过程关键信号

-

主机

- 写地址—M_AXI_AWVALID (output)和M_AXI_AWREADY (input)同时有效

- 紧接着写数据—M_AXI_WVALID (output)和M_AXI_WREADY (input)同时有效

- 具体传输多少取决于突发长度AWBURST(output)

- 为了保证从机知道主机是否准备好需要M_AXI_BREADY(output)

-

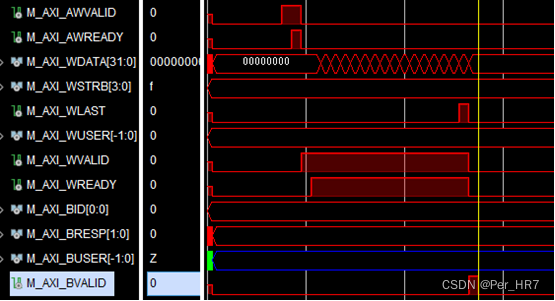

从机

- S_AXI_AWVALID (input)和S_AXI_AWREADY (output)同时有效,此时地址有效(与主机地址会有区别,主机地址更多位的原因是需要保证器件选择(高位进行器件选择功能))

- 紧接着写数据—S_AXI_WVALID (input)和S_AXI_WREADY (output)同时有效

- 写到最后一位S_AXI_WLAST(input)信号存在一个脉冲

- 完成后反馈一个有效信号—S_AXI_BVALID(output)和S_AXI_BREADY(input)

- 响应通道是00表示OK—S_AXI_BRESP(output) 00

读过程关键信号

-

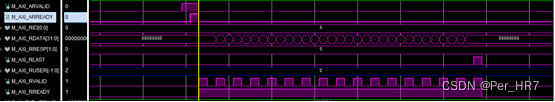

主机

- M_AXI_ARVALID(output)和M_AXI_ARREADY(input)同时有效

- M_AXI_RVALID(input)和M_AXI_RREADY(output)同时有效时候,表示读数据有效

-

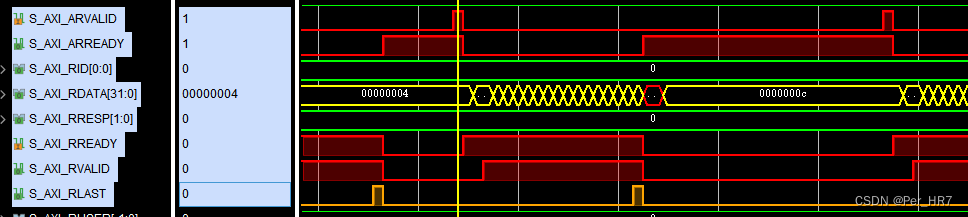

从机

- S_AXI_ARVALID(input)和S_AXI_ARREADY(output)同时有效

- S_AXI_RVALID(output)和S_AXI_RREADY(input)同时有效

- 发送完毕后一个S_AXI_RLAST(output)更新

这篇关于AXI总线协议---关键信号波形图分析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!