本文主要是介绍Xilinx FIFO Generator 需注意非对称位宽,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Xilinx FIFO Generator 需注意非对称位宽

系列文章推荐

- Xilinx FIFO Generator 需要注意RST复位

- Xilinx FIFO Generator 需要注意Actual Depth

- Xilinx FIFO Generator 需注意非对称位宽

- Xilinx FIFO Generator 需要注意BRAMs的资源消耗

在FIFO的使用中,经常会涉及到非对称位宽的情况,比如输入位宽为32 bit,输出位宽为64 bit;

Xilinx 的FIFO IP支持类似的操作(Altera的也支持)。

但是有些条件受限制,在没有仔细查看手册之前,不能想当然的认为什么样的比率都支持。

从pg057-fifo-generator.pdf,Page114中,能获取到以下信息。

是否支持

非对称的比率是否支持受不同的RAM类型影响,如下表:

由表中可以看出Block RAM和Built-in类型的RAM在独立时钟和共同时钟的条件下都是支持非对称位宽的, 其他的则不行;

比率可选

非对称比率值得是允许输入和输出FIFO的深度不同,支持的写入和读出比率为:

1:8,1:4,1:2,1:1,2:1,4:1,8:1;

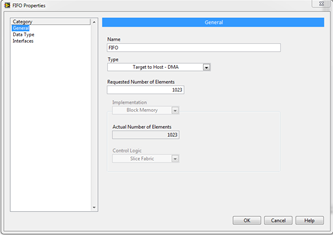

比率可以在生成FIFO的Vivado IP Catalog的GUI界面,通过特殊选项进行选择(默认状态下是1:1);

从1:8到8:1的比率都是可以选择的,而且输出的深度是根据输入的深度,位宽以及读出的位宽自动计算的。

读写操作

对于非对称比率的FIFO来说,FULL信号和EMPTY信号仅当一个完整的字(理解为较长的位宽)可以被写入或读取的时候才有效。

FIFO不允许部分字进行存取。

比如,假设一个FULL状态下的FIFO,如果写入的width为8 bits,读出的width为2 bits,应该完成4次有效的读操作,FULL信号才能解除断言,从而写操作才能够继续进行。

写操作计数根据写端口的比率来显示FIFO中的字数(以写入位宽为一个字的个数),读操作计数根据读端口的比率来显示FIFO中的字数(以读出位宽为一个字的个数);

1:4比率数据顺序

下图用例为1:4比率的FIFO(写入width为2,读出width为8)。

图例中,在读操作之前有4次连续的写操作被执行。第一个写操作为01,接着为00,11,最后一个为10。

内存填充为从左至右(MSB到LSB)。当一个读操作执行过后,接收数据为01_00_11_10;

下图展示了1:4比率FIFO的din,dout和一些握手信号的波形。在4个字被写入FIFO之后,EMPTY信号取消断言。而后一个读操作,EMPTY信号恢复断言。

4:1比率数据顺序

下图用例为4:1比率的FIFO(写入width为8,读出width为2)。

图例中,依次写操作执行后,有4次读操作执行。

写操作的数据为11_00_01_11。当读操作执行后,从左至右(MSB到LSB)的数据将被读数据接收。如下图展示,第一个读出的记过为11,接着是00,01,最后为11。

下图展示了4:1比率FIFO的din,dout和一些握手信号的波形。一个时钟的写操作之后,FIFO取消断言EMPTY信号。因为没有其他的写操作执行,FIFO在4次读操作之后恢复断言。

总结

在使用非对称位宽比率FIFO的时候,需要注意以下两点:

- 比率是否支持,仅支持1,2,4,8这几种倍率关系;

- 数据读写的顺序,需要判断数据的MSB和LSB是否与预期一致;

推荐例化IP之后,先做推荐的modelsim仿真,熟悉FIFO IP的数据传输方式,握手信号,再进行设计;

这篇关于Xilinx FIFO Generator 需注意非对称位宽的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!