本文主要是介绍vivado 约束范围界定,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

约束范围界定

来自特定XDC文件的约束可以选择性地作用于特定模块,以您设计的特定单元格,或者两者都有,如果需要的话。这便于创建和应用约束到设计的子级别,而没有任何关于顶层的信息。这个块级约束必须独立于顶层约束进行开发,并且必须尽可能通用,以便在各种上下文中使用。他们也不能影响超出块边界的任何逻辑。默认情况下,Vivado的所有IP核心Vivado Design Suite项目中生成的IP目录使用此机制加载其内存中的约束。

XDC文件作用域属性

通过在上指定以下属性来激活约束作用域机制XDC文件:

•SCOPED_TO_REF:此属性采用模块(或实体)的名称。限制条件是仅应用于指定模块(或实体)的所有实例。

•SCOPED_TO_CELLS:此属性采用分层单元格名称列表。限制条件是作用域并单独应用于每个分层单元。

•SCOPED_TO_REF+SCOPED_TO_CELLS:如果同时指定了这两个属性,约束应用于位于模块内部的SCOPED_to_CELLS列表的每个单元(或实体)由SCOPED_TO_REF指定。这些属性由Vivado Design Suite为添加到RTL的IP核自动设置项目通过IP目录。

设置XDC文件作用域属性示例

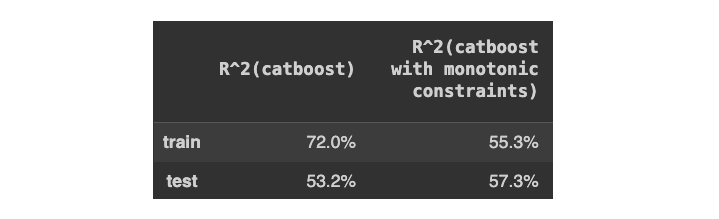

下图显示了uart_tx_i0单元格,它是uart_tx模块的一个实例,包括两个分层单元uart_tx_ctl_i0和uart_baud_gen_tx_i0。该项目包括一个XDC文件uart_tx_ctl.XDC,用于约束uart_tx-ctl模块。

以下是使用作用域属性的三个等效Tcl示例uart_tx_ctl.xdc。可以在中的xdc文件的“属性”窗口中设置相同的值Vivado IDE。

在非项目模式下使用Vivado Design Suite时,可以使用read_xdc命令带有-ref和-cells操作

当一个模块在设计中被实例化多次时,该模块在合成合成后,RTL模块的每个实例都指向不同的模块名称为了将一些XDC约束应用于原始RTL模块的所有实例应使用属性ORIG_REF_NAME而不是属性REF_NAME。例如:

XDC范围界定机制

除了端口之外,约束作用域依赖于current_instance机制,该机制是Synopsys设计约束(SDC)标准的一部分。将范围设置为较低级别时在带有current_instance命令的设计层次结构中,只有包含在中的对象对象查询命令可以返回该级别或更低级别。唯一的例外是定时时钟对象和网表端口:

•定时时钟由create_clock或create_generated_clock定义。它们是无论当前实例设置如何,在整个设计中都可见。get_clocks命令可以查询当前实例中不存在的或传播的时钟超出当前实例。AMD不建议在时钟上定义定时异常创建作用域约束时,除非它们完全包含在当前实例中。对于时钟要在XDC中可供参考,则该时钟必须已经定义。这可能需要更改顺序

•当作用域设置为较低时,get_ports命令会返回顶级端口使用current_instance命令级别实例。但是在读取XDC文件作用域时使用readxdc-ref/-cells命令或在加载设置SCOPED_TO_REF/SCOPED_TO_CELLS文件属性后的设计get_ports命令行为不同:

○要与get_ports一起使用的端口名是作用域实例的端口名接口,而不是顶级端口名。

○如果作用域实例端口通过的层次结构直接连接到顶级端口在设计中,顶级端口由getports命令和约束返回应用于顶级端口。

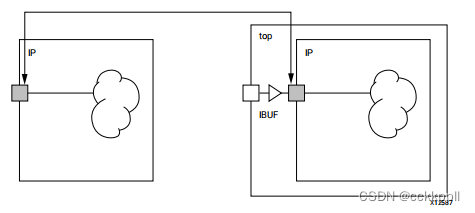

○如果作用域实例端口之间有任何叶单元,包括IO和时钟缓冲区和顶级端口,get_ports命令变为get_pins命令,并且返回层次结构范围的实例pin。XDC作用域机制用于读取所有Vivado Design Suite IP约束文件。图形47和图48显示了当使用这种方法在IP级XDC中读取。在图47中,I/O缓冲区在IP内实例化,IP接口引脚直接连接到顶级端口(无论层次结构如何)。当应用用于IP的XDC时,用顶级端口替换的getports的参数。这允许将物理属性(如LOC或IOSTANDARD)设置为

下图中,IP不包含I/O缓冲区,因此合成引擎推断出一个在IP接口引脚和顶级端口之间。因此,get_ports被转换为当应用XDC时IP接口引脚(例如分层引脚)的get_pins。

此功能对于在IP或子级别的接口上创建约束非常有用模块,而不知道顶层设计的名称。如果作用域XDC文件包含只能应用于顶级端口但不能应用于IP的约束实例没有直接连接到顶级端口,Vivado Design Suite XDC读取器将返回错误。例如,以下约束只能应用于顶级端口,以及而不是您设计的分层引脚:

这篇关于vivado 约束范围界定的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!