本文主要是介绍加速计算卡学习资料第412篇:基于单XCVU9P+双DSP C6678的双FMC接口 100G光纤传输加速计算卡,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

| 基于单XCVU9P+双DSP C6678的双FMC接口 100G光纤传输加速计算卡 |

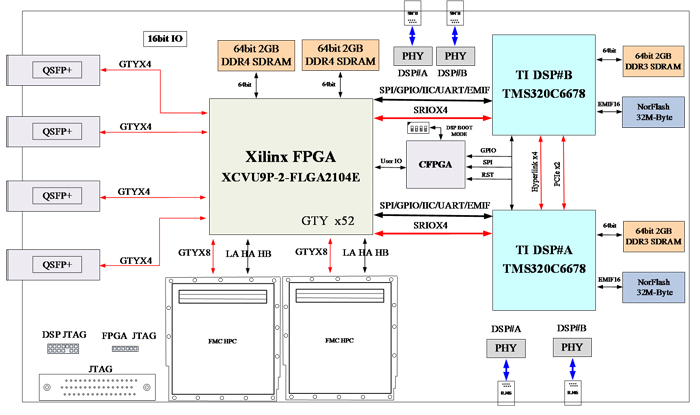

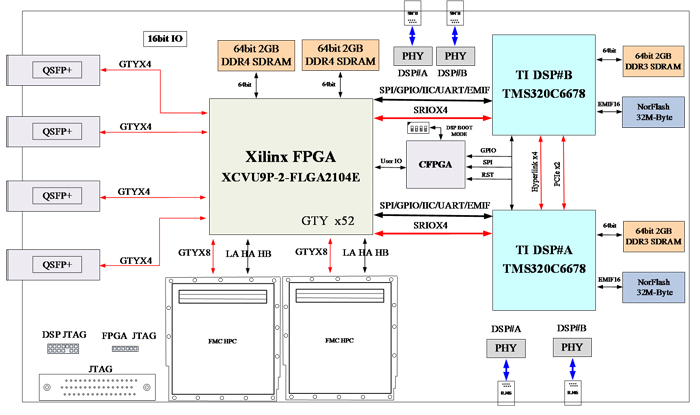

| | | | | 一、板卡概述 板卡包括一片Xilinx FPGA XCVU9P,两片 TI 多核DSP TMS320C6678及其控制管理芯片CFPGA.设计芯片满足工业级要求。 FPGA VU9P 需要外接4路QSFP+(100Gbps)及其两个FMC HPC接口。DSP需要外接两路千兆以太网。如下图所示:

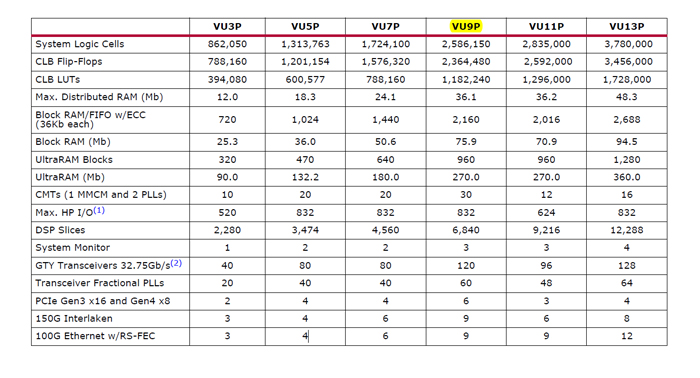

图 1:原理框图 二、主要功能及性能指标 - FPGA处理器采用Xilinx Virtex UltralSCALE+ 系列芯片 XCVU9P。

- FPGA 外挂2组FMC HPC 连接器。

- FPGA 外挂两簇DDR4

- FPGA 每簇DDR4位宽64bit,容量2GB,数据速率2400Mb/s。

- FPGA 连接4路QSPF+,每路QSFP+数据速率100Gb/s。

- FPGA 预留GPIO ,TTL3V3电平。

- 光模块的参考时钟可以切换至外部时钟源,频率245.76MHz。

- DSP处理器采用两颗TI 8核处理器TMS320C6678。

- 每片DSP 外挂一组64bit DDR3颗粒,总容量2GB,数据速率1333Mb/s。

- DSP 采用EMIF16 NorFlash加载模式,NorFlash容量32MB。

- 每片DSP 外挂两路千兆以太网1000BASE-T,分别放置在板卡的上边沿和下边沿。

- DSP 和FPGA 之间通过SRIO x4互联@5Gbps。

- DSP间通过Hyperlink x4 互联。

- DSP,FPGA,CFPGA 仿真器接口连接到J30J-66ZKWP7-J连接器,且板卡预留仿真器接口。

- CFPGA 外接拨码开关控制DSP boot模式的切换。

- 板卡单电源输入12v。

- 板卡配套散热和加固设计。

三、FMC配套子卡说明 | 子卡编号 | 说明 | | FMC147 | 1.25 GSPS / 2.5 GSPS / 5.0 GSPS 10位ADC | | FMC228 | 四路16位1.2Gsps DAC | | FMC303 | 两路14位2.5Gsps DA |

四、板卡结构 板卡结构为非标结构,长x宽:360mm x 217mm,光口的位置在板卡的左侧,电源供电在板卡的上边沿,具体板卡形态如下图所示:  图 2:板卡外形 五、FPGA资源介绍

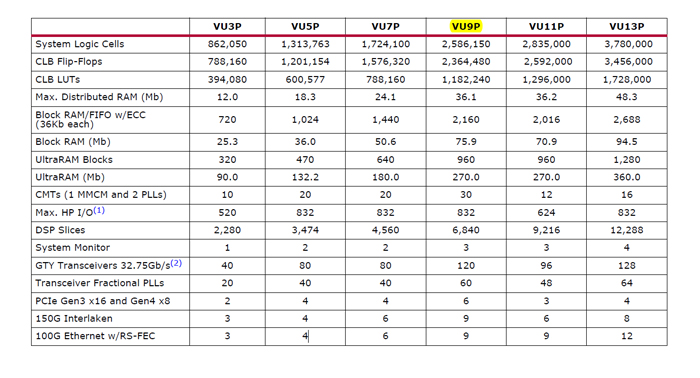

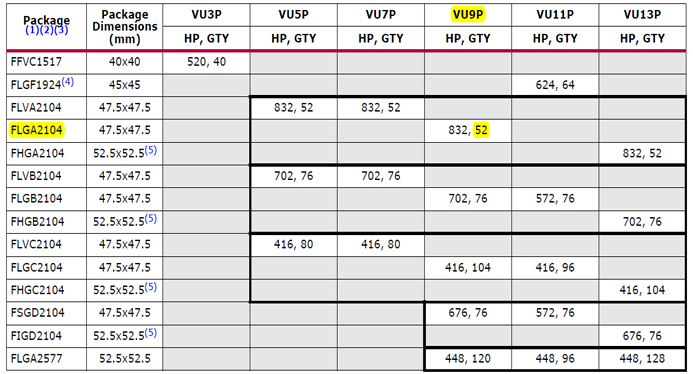

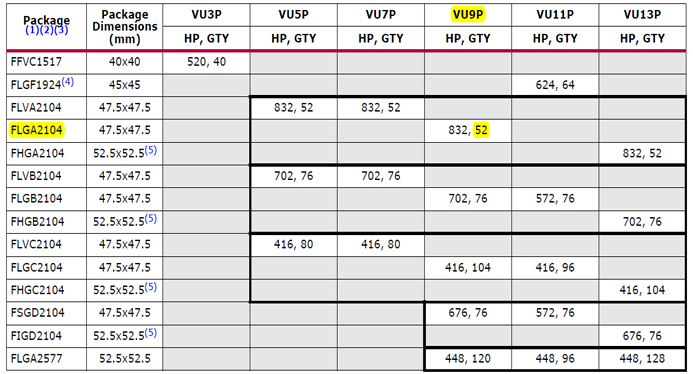

GTY分配 VU9P有52对GTY,其 高速率32.75Gb/s。由下表可知目前的设计只占用了12GTY。 高速率32.75Gb/s。由下表可知目前的设计只占用了12GTY。 | 接口描述 | 接口个数 | GTH数量 | | QSFP+ | 4 | 16 | | SRIO | 1 | 4 | | FMC | 2 | 16 | | 总计 | | 36 |

GPIO分配

VU9P共有HP管脚832个,16个bank。BPI Flash 占用1个,和DSP 互联占用1个。 | 接口描述 | 接口数量 | 占用管脚个数 | 占用BANK数量 | 备注 | | BPI Flash | 1 | | 1 | | | FMC | 2 | | 8 | | DDR4 | 2 | | 6 | | DSP | 2 | | 1 |

六、接口测试 表 1:DSP接口测试项 | 序号 | 接口 | 备注 | | 1 | DDR3 接口测试 | | | 2 | 千兆以太网测试 | | | 3 | SRIO 接口测试 | | | 4 | 程序加载测试 | | | 5 | | |

FPGA接口 表 2:FPGA接口测试项 | 序号 | 接口 | 备注 | | 1 | QSFP+接口测试 | | | 2 | SRIO 接口测试 | | | 3 | 程序加载测试 | | | 4 | DDR4接口测试 | | | 5 | FMC 参考测试 | | | 6 | | |

|

文章来源 北京太速科 |

这篇关于加速计算卡学习资料第412篇:基于单XCVU9P+双DSP C6678的双FMC接口 100G光纤传输加速计算卡的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

高速率32.75Gb/s。由下表可知目前的设计只占用了12GTY。

高速率32.75Gb/s。由下表可知目前的设计只占用了12GTY。