本文主要是介绍AMBA协议AXI-Lite(AXI-Lite从机代码设计),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 一、设计思路

- 1、什么时候发生写数据操作?

- 2.什么时候发生数据读操作?

- 3.如何根据AXI_WSTRB信号完成数据的写入?

- 二、源码设计

- 2.1 写通道源码设计

- 2.2 读通道源码设计

- 2.3 模板代码

- 三、仿真

- 总结

一、设计思路

在设计开始之前,我们需要弄清楚以下几个问题:

- 什么时候发生写数据操作?

- 什么时候发生数据写操作?

- 如何根据AXI_WSTRB信号完成数据的写入?

1、什么时候发生写数据操作?

我们在第4-1节对AXI-Lite协议介绍后,分析了写数据发生的条件,那就是当 写数据和写地址 同时有效时,立即完成传输;

我们将上面的条件翻译一下,就是当AXI_AWVALID、AXI_AWREADY、AXI_WVALID、AXI_WREADY同时有效时,完成数据写入;

在此之上,我们还需考虑一个问题,就是完成数据写入后的写响应阶段,在写响应传输的过程中,应该忽略总线上的数据,故引入一个arwen信号来指示当前时刻是否允许地址数据的写入,当BVALID与BREADY信号为高时,arwen有效;

所以我们对写入条件进行修正,当AXI_AWVALID、AXI_AWREADY、AXI_WVALID、AXI_WREADY、arwen信号同时有效时,完成数据写入;

2.什么时候发生数据读操作?

数据读操作发生在读地址写入之后,从机将对应寄存器的数据放到读数据通道上;

上述条件翻译后,就是当AXI_ARREADY、AXI_ARVALID有效时发生传输;

3.如何根据AXI_WSTRB信号完成数据的写入?

我们的数据写入也可不通过AXI_WSTRB指示,但为了接口设计的灵活性,我们通常会根据该信号对寄存器进行写入;

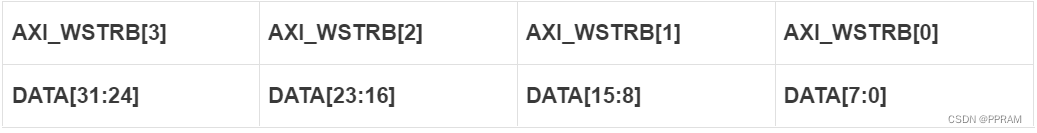

我们只需查询对应位是否为1,将对应的位数写入寄存器即可;其对应关系如下:

我们只需查询对应位是否为1,将对应的位数写入寄存器即可;我们只需查询对应位是否为1,将对应的位数写入寄存器即可;

我们只需查询对应位是否为1,将对应的位数写入寄存器即可;我们只需查询对应位是否为1,将对应的位数写入寄存器即可;

二、源码设计

2.1 写通道源码设计

1.写地址逻辑

//---------------------------write address input logic--------------------------------////transmit finish whe s_axi_awvalid=1 axi_awready = 1 s_axi_wvalid = 1always @(posedge s_axi_aclk) begin : address_input_proc_if(~s_axi_aresentn) beginaxi_awaddr <= 'b0;axi_awready <= 1'b0;aw_en <= 1'b1;end else beginif(aw_en && s_axi_awvalid && (~axi_awready) && (s_axi_wvalid))beginaw_en <= 1'b0;axi_awaddr <= s_axi_awaddr;axi_awready <= 1'b1; endelse if(axi_bvalid && s_axi_bready)beginaw_en <= 1'b1;endelsebeginaxi_awready <= 1'b0;endendend

寄存地址的条件为: aw_en为高电平、s_axi_awvalid地址有效且axi_awready和s_axi_wvalid有效;

aw_en用来指示当前阶段是否完成一次读响应的发送;

2.写数据Ready逻辑

//-------------------------write data logic------------------------------------//always @(posedge s_axi_aclk) begin : write_data_signal_proc_if(~s_axi_aresentn) beginaxi_wready <= 1'b0;end else beginif(aw_en && s_axi_awvalid && s_axi_wvalid && ~axi_wready)beginaxi_wready <= 1'b1;endelsebeginaxi_wready <= 1'b0;endendend

当aw_en、s_axi_awvalid以及s_axi_wvalid有效时,将axi_wready拉高一个时钟周期后拉低,告诉主机从机已经完成接收;

3.写响应逻辑

//------------------------write back response logic--------------------------//always @(posedge s_axi_aclk) begin : wr_back_logic_proc_if(~s_axi_aresentn) beginaxi_bresp <= 'b0;axi_bvalid <= 1'b0;end else beginif(s_axi_awvalid & axi_awready & s_axi_wvalid & axi_wready & (~axi_bvalid))beginaxi_bresp <= 'b0;axi_bvalid <= 1'b1;endelsebeginaxi_bresp <= 'b0;axi_bvalid <= 1'b0;endendend

写响应发生在一次数据写入后,而当一次数据传输完成时,s_axi_awvalid、axi_awready、s_axi_wvalid和axi_wready均为高(握手协议在ready和valid信号为高时立即完成传输),此时将axi_bvalid信号拉高一个时钟周期;

4.寄存器写入逻辑

integer byte_index;integer reg_index;always @(posedge s_axi_aclk) begin : register_write_proc_if(~s_axi_aresentn) beginfor(reg_index = 0;reg_index<C_AXI_SLV_REG_NUM;reg_index=reg_index+1)beginslv_reg[reg_index] <= 'b0;endend else beginif(register_wr_en)beginfor(reg_index = 0;reg_index<C_AXI_SLV_REG_NUM;reg_index=reg_index+1)beginif(reg_index == (axi_awaddr >> ADDR_SHIFT))beginfor(byte_index = 0;byte_index <= (C_AXI_DATA_WIDTH/8)-1;byte_index = byte_index + 1)beginif(s_axi_wstrb[byte_index] == 1'b1)beginslv_reg[reg_index][(byte_index*8)+:8] <= s_axi_wdata[(byte_index*8)+:8];endendendendendendend

其中,ADDR_SHIFT的定义为:

localparam integer ADDR_SHIFT = C_AXI_DATA_WIDTH/16;

其为地址转换为ID号所需要右移的位数;用数据位宽除以16即可;

如地址为0x08 右移两位为 0x02,为ID=2的寄存器;

第13行起,首先通过一个for循环找到需要赋值的寄存器;

然后再通过一个for循环,根据第一节中AXI_WSTRB指示的数据来对寄存器对应位数进行赋值,赋值逻辑为:

for(byte_index = 0;byte_index <= (C_AXI_DATA_WIDTH/8)-1;byte_index = byte_index + 1)

beginif(s_axi_wstrb[byte_index] == 1'b1)beginslv_reg[reg_index][(byte_index*8)+:8] <= s_axi_wdata[(byte_index*8)+:8];end

end

其中AXI_WSTRB的第0位对应是否对寄存器的低0-7位赋值;

AXI_WSTRB的第1位对应是否对寄存器的低8-15位赋值;

AXI_WSTRB的第2位对应是否对寄存器的低16-23位赋值;

AXI_WSTRB的第2位对应是否对寄存器的低23-31位赋值;

2.2 读通道源码设计

1.读地址逻辑:

//-----------------------read address logic---------------------------------//always @(posedge s_axi_aclk) begin : read_address_proc_if(~s_axi_aresentn) beginaxi_araddr <= 'b0;axi_arready <= 1'b0;end else beginif(~axi_arready & s_axi_arvalid)beginaxi_araddr <= s_axi_araddr;axi_arready <= 1'b1;endelsebeginaxi_arready <= 1'b0;endendend

读地址只需判断主机发来的读地址数据是否有效即可,即s_axi_arvalid是否有效;

若有效就将读地址放入读地址寄存器axi_araddr中,并拉高一个时钟周期的axi_arready信号通知主机完成接收;

2.读数据逻辑

//------------------------read data logic--------------------------------//always @(posedge s_axi_aclk) begin : read_data_proc_if(~s_axi_aresentn) beginaxi_rdata <= 'b0;axi_rvalid <= 1'b0;end else beginif(axi_arready & s_axi_arvalid & ~axi_rvalid)beginaxi_rvalid <= 1'b1;axi_rdata <= reg_data_out;endelsebeginaxi_rvalid <= 1'b0;endendend

读数据逻辑发生在读地址传输结束之后,即axi_arready 和 s_axi_arvalid均为有效时;

此时将寄存器读出数据打入读数据输出寄存器axi_rdata;并拉高一个时钟的axi_rvalid告诉主机当前读数据有效;

3.读寄存器逻辑

//------------------------read register logic-------------------------------//always @(*) begin : register_read_proc_if(~s_axi_aresentn) beginreg_data_out <= 'b0;end else begincase(axi_araddr >> ADDR_SHIFT)'d0: reg_data_out <= slv_reg[0];'d1: reg_data_out <= slv_reg[1];'d2: reg_data_out <= slv_reg[2];'d3: reg_data_out <= slv_reg[3];'d4: reg_data_out <= slv_reg[4];'d5: reg_data_out <= slv_reg[5];'d6: reg_data_out <= slv_reg[6];'d7: reg_data_out <= slv_reg[7];endcaseendend

读寄存器逻辑采用组合逻辑,将地址映射的寄存器中内容读出;

2.3 模板代码

接下来给出整个设计的模板代码:

1.逻辑部分

//AXI Slave interface

module axi_lite_logic#(//axi-lite parameter definition start here//data width / address widthparameter integer C_AXI_SLV_REG_NUM = 8,parameter integer C_AXI_DATA_WIDTH = 32,parameter integer C_AXI_ADDR_WIDTH = $clog2(C_AXI_SLV_REG_NUM*4)+1)

(//system signals definitioninput wire s_axi_aclk,input wire s_axi_aresentn, //write address signals definition input wire [C_AXI_ADDR_WIDTH - 1:0] s_axi_awaddr,input wire s_axi_awvalid,output wire s_axi_awready,//write data signals definitioninput wire [C_AXI_DATA_WIDTH - 1:0] s_axi_wdata,input wire s_axi_wvalid,output wire s_axi_wready, input wire [(C_AXI_DATA_WIDTH/8) - 1:0] s_axi_wstrb,//write response signals definitionoutput wire [1:0] s_axi_bresp,output wire s_axi_bvalid,input wire s_axi_bready,//read address signals definitioninput wire [C_AXI_ADDR_WIDTH - 1:0] s_axi_araddr,input wire s_axi_arvalid,output wire s_axi_arready,//read data signals definitionoutput wire [C_AXI_DATA_WIDTH - 1:0] s_axi_rdata,output wire s_axi_rvalid,input wire s_axi_rready,//read response signals definitionoutput wire s_axi_rresp,//protect signals definitioninput wire s_axi_arprot

);localparam integer ADDR_SHIFT = C_AXI_DATA_WIDTH/16;reg [C_AXI_ADDR_WIDTH - 1:0] axi_awaddr;reg axi_awready;reg axi_wready;reg [1:0] axi_bresp;reg axi_bvalid;reg aw_en;reg [C_AXI_ADDR_WIDTH - 1:0] axi_araddr;reg axi_arready;reg axi_rvalid;reg [C_AXI_DATA_WIDTH - 1:0] axi_rdata;reg [C_AXI_DATA_WIDTH - 1:0] reg_data_out;wire register_wr_en;//register definitionreg [(C_AXI_DATA_WIDTH - 1) : 0] slv_reg[0:(C_AXI_SLV_REG_NUM-1)];//inner logic definitionassign register_wr_en = axi_wready & s_axi_wvalid & axi_awready & s_axi_awvalid; //inner signal connectassign s_axi_awready = axi_awready;assign s_axi_wready = axi_wready;assign s_axi_bresp = axi_bresp;assign s_axi_bvalid = axi_bvalid;assign s_axi_arready = axi_arready;assign s_axi_rdata = axi_rdata;assign s_axi_rvalid = axi_rvalid;assign s_axi_rresp = 2'b00;//---------------------------write address input logic--------------------------------////transmit finish whe s_axi_awvalid=1 axi_awready = 1 s_axi_wvalid = 1always @(posedge s_axi_aclk) begin : address_input_proc_if(~s_axi_aresentn) beginaxi_awaddr <= 'b0;axi_awready <= 1'b0;aw_en <= 1'b1;end else beginif(aw_en && s_axi_awvalid && (~axi_awready) && (s_axi_wvalid))beginaw_en <= 1'b0;axi_awaddr <= s_axi_awaddr;axi_awready <= 1'b1; endelse if(axi_bvalid && s_axi_bready)beginaw_en <= 1'b1;endelsebeginaxi_awready <= 1'b0;endendend//-------------------------write data logic------------------------------------//always @(posedge s_axi_aclk) begin : write_data_signal_proc_if(~s_axi_aresentn) beginaxi_wready <= 1'b0;end else beginif(aw_en && s_axi_awvalid && s_axi_wvalid && ~axi_wready)beginaxi_wready <= 1'b1;endelsebeginaxi_wready <= 1'b0;endendend//------------------------write back response logic--------------------------//always @(posedge s_axi_aclk) begin : wr_back_logic_proc_if(~s_axi_aresentn) beginaxi_bresp <= 'b0;axi_bvalid <= 1'b0;end else beginif(s_axi_awvalid & axi_awready & s_axi_wvalid & axi_wready & (~axi_bvalid))beginaxi_bresp <= 'b0;axi_bvalid <= 1'b1;endelsebeginaxi_bresp <= 'b0;axi_bvalid <= 1'b0;endendend//-----------------------read address logic---------------------------------//always @(posedge s_axi_aclk) begin : read_address_proc_if(~s_axi_aresentn) beginaxi_araddr <= 'b0;axi_arready <= 1'b0;end else beginif(~axi_arready & s_axi_arvalid)beginaxi_araddr <= s_axi_araddr;axi_arready <= 1'b1;endelsebeginaxi_arready <= 1'b0;endendend//------------------------read data logic--------------------------------//always @(posedge s_axi_aclk) begin : read_data_proc_if(~s_axi_aresentn) beginaxi_rdata <= 'b0;axi_rvalid <= 1'b0;end else beginif(axi_arready & s_axi_arvalid & ~axi_rvalid)beginaxi_rvalid <= 1'b1;axi_rdata <= reg_data_out;endelsebeginaxi_rvalid <= 1'b0;endendend//------------------------write register logic-------------------------------//integer byte_index;integer reg_index;always @(posedge s_axi_aclk) begin : register_write_proc_if(~s_axi_aresentn) beginfor(reg_index = 0;reg_index<C_AXI_SLV_REG_NUM;reg_index=reg_index+1)beginslv_reg[reg_index] <= 'b0;endend else beginif(register_wr_en)beginfor(reg_index = 0;reg_index<C_AXI_SLV_REG_NUM;reg_index=reg_index+1)beginif(reg_index == (axi_awaddr >> ADDR_SHIFT))beginfor(byte_index = 0;byte_index <= (C_AXI_DATA_WIDTH/8)-1;byte_index = byte_index + 1)beginif(s_axi_wstrb[byte_index] == 1'b1)beginslv_reg[reg_index][(byte_index*8)+:8] <= s_axi_wdata[(byte_index*8)+:8];endendendendendendend//------------------------read register logic-------------------------------//always @(*) begin : register_read_proc_if(~s_axi_aresentn) beginreg_data_out <= 'b0;end else begincase(axi_araddr >> ADDR_SHIFT)'d0: reg_data_out <= slv_reg[0];'d1: reg_data_out <= slv_reg[1];'d2: reg_data_out <= slv_reg[2];'d3: reg_data_out <= slv_reg[3];'d4: reg_data_out <= slv_reg[4];'d5: reg_data_out <= slv_reg[5];'d6: reg_data_out <= slv_reg[6];'d7: reg_data_out <= slv_reg[7];endcaseendend

endmodule

2.顶层

module axi_lite_logic_top#(parameter integer C_AXI_SLV_REG_NUM = 8,parameter integer C_AXI_DATA_WIDTH = 32,parameter integer C_AXI_ADDR_WIDTH = $clog2(C_AXI_SLV_REG_NUM*4)+1) (//system signals definitioninput wire S_AXI_ACLK,input wire S_AXI_ARESENTN, //write address signals definition input wire [C_AXI_ADDR_WIDTH - 1:0] S_AXI_AWADDR,input wire S_AXI_AWVALID,output wire S_AXI_AWREADY,//write data signals definitioninput wire [C_AXI_DATA_WIDTH - 1:0] S_AXI_WDATA,input wire S_AXI_WVALID,output wire S_AXI_WREADY, input wire [(C_AXI_DATA_WIDTH/8) - 1:0] S_AXI_WSTRB,//write response signals definitionoutput wire [1:0] S_AXI_BRESP,output wire S_AXI_BVALID,input wire S_AXI_BREADY,//read address signals definitioninput wire [C_AXI_ADDR_WIDTH - 1:0] S_AXI_ARADDR,input wire S_AXI_ARVALID,output wire S_AXI_ARREADY,//read data signals definitionoutput wire [C_AXI_DATA_WIDTH - 1:0] S_AXI_RDATA,output wire S_AXI_RVALID,input wire S_AXI_RREADY,//read response signals definitionoutput wire S_AXI_RRESP,//protect signals definitioninput wire S_AXI_ARPROT

);axi_lite_logic#(//axi-lite parameter definition start here//data width / address width.C_AXI_SLV_REG_NUM (C_AXI_SLV_REG_NUM),.C_AXI_DATA_WIDTH(C_AXI_DATA_WIDTH),.C_AXI_ADDR_WIDTH(C_AXI_ADDR_WIDTH))axi_lite_logic_inist0

(//system signals definition.s_axi_aclk(S_AXI_ACLK),.s_axi_aresentn(S_AXI_ARESENTN), //write address signals definition .s_axi_awaddr(S_AXI_AWADDR),.s_axi_awvalid(S_AXI_AWVALID),.s_axi_awready(S_AXI_AWREADY),//write data signals definition.s_axi_wdata(S_AXI_WDATA),.s_axi_wvalid(S_AXI_WVALID),.s_axi_wready(S_AXI_WREADY), .s_axi_wstrb(S_AXI_WSTRB),//write response signals definition.s_axi_bresp(S_AXI_BRESP),.s_axi_bvalid(S_AXI_BVALID),.s_axi_bready(S_AXI_BREADY),//read address signals definition.s_axi_araddr(S_AXI_ARADDR),.s_axi_arvalid(S_AXI_ARVALID),.s_axi_arready(S_AXI_ARREADY),//read data signals definition.s_axi_rdata(S_AXI_RDATA),.s_axi_rvalid(S_AXI_RVALID),.s_axi_rready(S_AXI_RREADY),//read response signals definition.s_axi_rresp(S_AXI_RRESP),//protect signals definition.s_axi_arprot(S_AXI_ARPROT)

);module axi_lite_logic_top#(parameter integer C_AXI_SLV_REG_NUM = 8,parameter integer C_AXI_DATA_WIDTH = 32,parameter integer C_AXI_ADDR_WIDTH = $clog2(C_AXI_SLV_REG_NUM*4)+1) (//system signals definitioninput wire S_AXI_ACLK,input wire S_AXI_ARESENTN, //write address signals definition input wire [C_AXI_ADDR_WIDTH - 1:0] S_AXI_AWADDR,input wire S_AXI_AWVALID,output wire S_AXI_AWREADY,//write data signals definitioninput wire [C_AXI_DATA_WIDTH - 1:0] S_AXI_WDATA,input wire S_AXI_WVALID,output wire S_AXI_WREADY, input wire [(C_AXI_DATA_WIDTH/8) - 1:0] S_AXI_WSTRB,//write response signals definitionoutput wire [1:0] S_AXI_BRESP,output wire S_AXI_BVALID,input wire S_AXI_BREADY,//read address signals definitioninput wire [C_AXI_ADDR_WIDTH - 1:0] S_AXI_ARADDR,input wire S_AXI_ARVALID,output wire S_AXI_ARREADY,//read data signals definitionoutput wire [C_AXI_DATA_WIDTH - 1:0] S_AXI_RDATA,output wire S_AXI_RVALID,input wire S_AXI_RREADY,//read response signals definitionoutput wire S_AXI_RRESP,//protect signals definitioninput wire S_AXI_ARPROT

);axi_lite_logic#(//axi-lite parameter definition start here//data width / address width.C_AXI_SLV_REG_NUM (C_AXI_SLV_REG_NUM),.C_AXI_DATA_WIDTH(C_AXI_DATA_WIDTH),.C_AXI_ADDR_WIDTH(C_AXI_ADDR_WIDTH))axi_lite_logic_inist0

(//system signals definition.s_axi_aclk(S_AXI_ACLK),.s_axi_aresentn(S_AXI_ARESENTN), //write address signals definition .s_axi_awaddr(S_AXI_AWADDR),.s_axi_awvalid(S_AXI_AWVALID),.s_axi_awready(S_AXI_AWREADY),//write data signals definition.s_axi_wdata(S_AXI_WDATA),.s_axi_wvalid(S_AXI_WVALID),.s_axi_wready(S_AXI_WREADY), .s_axi_wstrb(S_AXI_WSTRB),//write response signals definition.s_axi_bresp(S_AXI_BRESP),.s_axi_bvalid(S_AXI_BVALID),.s_axi_bready(S_AXI_BREADY),//read address signals definition.s_axi_araddr(S_AXI_ARADDR),.s_axi_arvalid(S_AXI_ARVALID),.s_axi_arready(S_AXI_ARREADY),//read data signals definition.s_axi_rdata(S_AXI_RDATA),.s_axi_rvalid(S_AXI_RVALID),.s_axi_rready(S_AXI_RREADY),//read response signals definition.s_axi_rresp(S_AXI_RRESP),//protect signals definition.s_axi_arprot(S_AXI_ARPROT)

);endmodule这里为了后面方便在Vivado上对测试模块进行封装,顶层端口的定义需要按一定的格式来进行;

这样在进行IP封装时,工具会自动将这些端口划分为AXI总线,否则需要自己手动封装AXI接口;

参数定义:

- C_AXI_SLV_REG_NUM:表示寄存器的数目;

- C_AXI_DATA_WIDTH:数据位宽;

- C_AXI_ADDR_WIDTH:地址位宽,根据寄存器数自动计算;

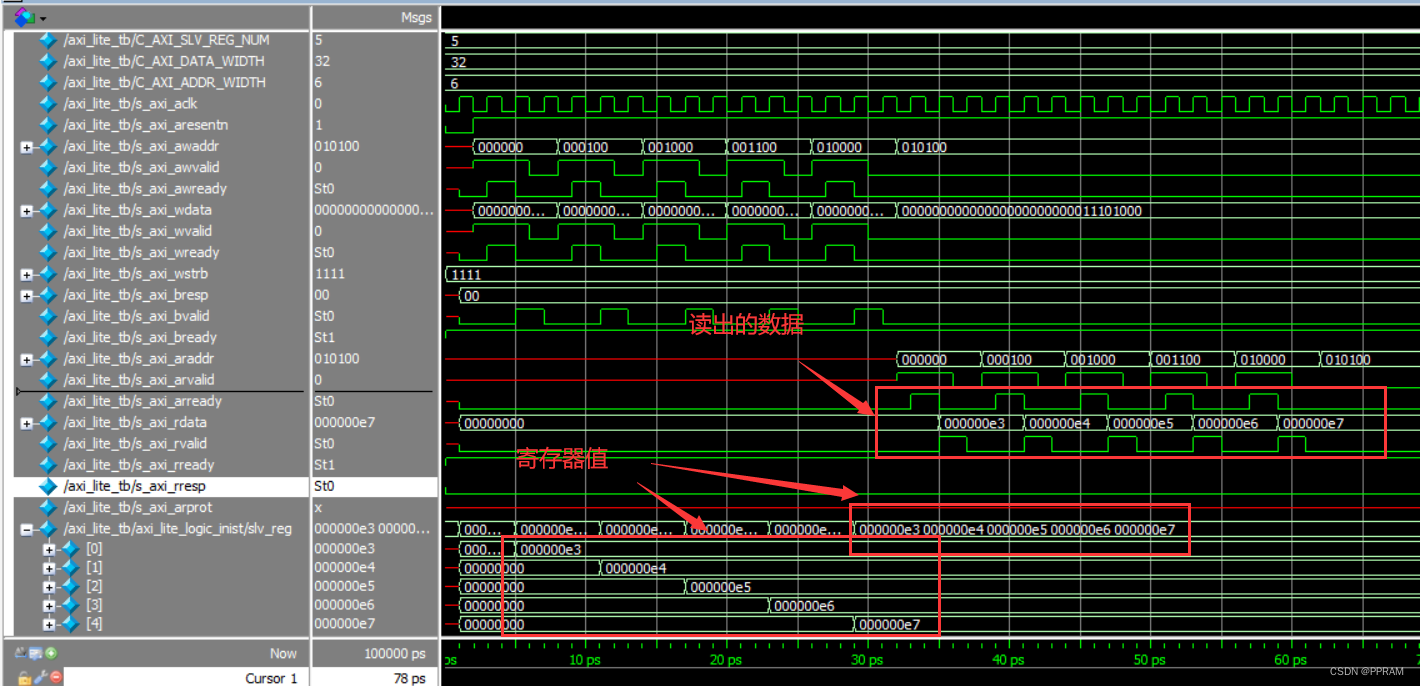

三、仿真

- 仿真软件:modelsim

- 仿真文件:逻辑文件

仿真源码:

module axi_lite_tb ();parameter integer C_AXI_SLV_REG_NUM = 5;parameter integer C_AXI_DATA_WIDTH = 32;parameter integer C_AXI_ADDR_WIDTH = $clog2(C_AXI_SLV_REG_NUM*4)+1;reg s_axi_aclk;reg s_axi_aresentn; reg [C_AXI_ADDR_WIDTH - 1:0] s_axi_awaddr;reg s_axi_awvalid;wire s_axi_awready;reg [C_AXI_DATA_WIDTH - 1:0] s_axi_wdata;reg s_axi_wvalid;wire s_axi_wready; wire [(C_AXI_DATA_WIDTH/8) - 1:0] s_axi_wstrb;wire [1:0] s_axi_bresp;wire s_axi_bvalid;wire s_axi_bready;reg [C_AXI_ADDR_WIDTH - 1:0] s_axi_araddr;reg s_axi_arvalid;wire s_axi_arready;wire [C_AXI_DATA_WIDTH - 1:0] s_axi_rdata;wire s_axi_rvalid;wire s_axi_rready;wire s_axi_rresp;reg s_axi_arprot;assign s_axi_wstrb = 4'b1111;assign s_axi_bready = 1'b1;assign s_axi_rready = 1'b1;initial begins_axi_aclk = 0;forever begin#1 s_axi_aclk = ~s_axi_aclk;endendinitial begins_axi_aresentn = 0;#2 s_axi_aresentn = 1;s_axi_awaddr = 5'h00;s_axi_wdata = 32'he3;//test write logicwhile(s_axi_awaddr <= 5'h10)begins_axi_awvalid = 1'b1;s_axi_wvalid = 1'b1;#4s_axi_awvalid = 1'b0;s_axi_wvalid = 1'b0;#2s_axi_awaddr = s_axi_awaddr+5'h4;s_axi_wdata = s_axi_wdata+1;end//test read logics_axi_araddr = 5'h00;while(s_axi_araddr <= 5'h10)begins_axi_arvalid = 1'b1;#4s_axi_arvalid = 1'b0;#2s_axi_araddr = s_axi_araddr+5'h4;endendaxi_lite_logic#(.C_AXI_SLV_REG_NUM(C_AXI_SLV_REG_NUM),.C_AXI_DATA_WIDTH(C_AXI_DATA_WIDTH),.C_AXI_ADDR_WIDTH(C_AXI_ADDR_WIDTH))axi_lite_logic_inist

(.s_axi_aclk(s_axi_aclk),.s_axi_aresentn(s_axi_aresentn), .s_axi_awaddr(s_axi_awaddr),.s_axi_awvalid(s_axi_awvalid),.s_axi_awready(s_axi_awready),.s_axi_wdata(s_axi_wdata),.s_axi_wvalid(s_axi_wvalid),.s_axi_wready(s_axi_wready), .s_axi_wstrb(s_axi_wstrb),.s_axi_bresp(s_axi_bresp),.s_axi_bvalid(s_axi_bvalid),.s_axi_bready(s_axi_bready),.s_axi_araddr(s_axi_araddr),.s_axi_arvalid(s_axi_arvalid),.s_axi_arready(s_axi_arready),.s_axi_rdata(s_axi_rdata),.s_axi_rvalid(s_axi_rvalid),.s_axi_rready(s_axi_rready),.s_axi_rresp(s_axi_rresp),.s_axi_arprot(s_axi_arprot)

);

endmodule

首先测试写入逻辑,对寄存器0-7写入e3,e4,e5,e6,e7

然后依次读出寄存器的值

仿真结果:

总结

在本篇中给出了AXI_Lite从机接口的模板文件设计,在下一篇中将基于模板文件设计一SOC系统,进行软硬件协同仿真,完成板级验证;

这篇关于AMBA协议AXI-Lite(AXI-Lite从机代码设计)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!