amba专题

AMBA-CHI协议详解(八)

AMBA-CHI协议详解(一) AMBA-CHI协议详解(二) AMBA-CHI协议详解(三) AMBA-CHI协议详解(四) AMBA-CHI协议详解(五) AMBA-CHI协议详解(六) AMBA-CHI协议详解(七) AMBA-CHI协议详解(八) 文章目录 2.7 Address, Control, and Data2.7.1 Address2.7.2 Physical Add

【AMBA Bus ACE 总线11 -- ACE DVM(Distributed Virtual Memory)使用介绍】

文章目录 ACE DVM 使用背景DVM Transactions 类型和作用DVM 消息使用场景DVM 示例Sumamry ACE DVM 使用背景 当 Cache maintenance 指令操作完以后,落实到总线上的时候,它会有一组 cache maintenance transaction 出来,这组 cache maintenance transaction 主要是

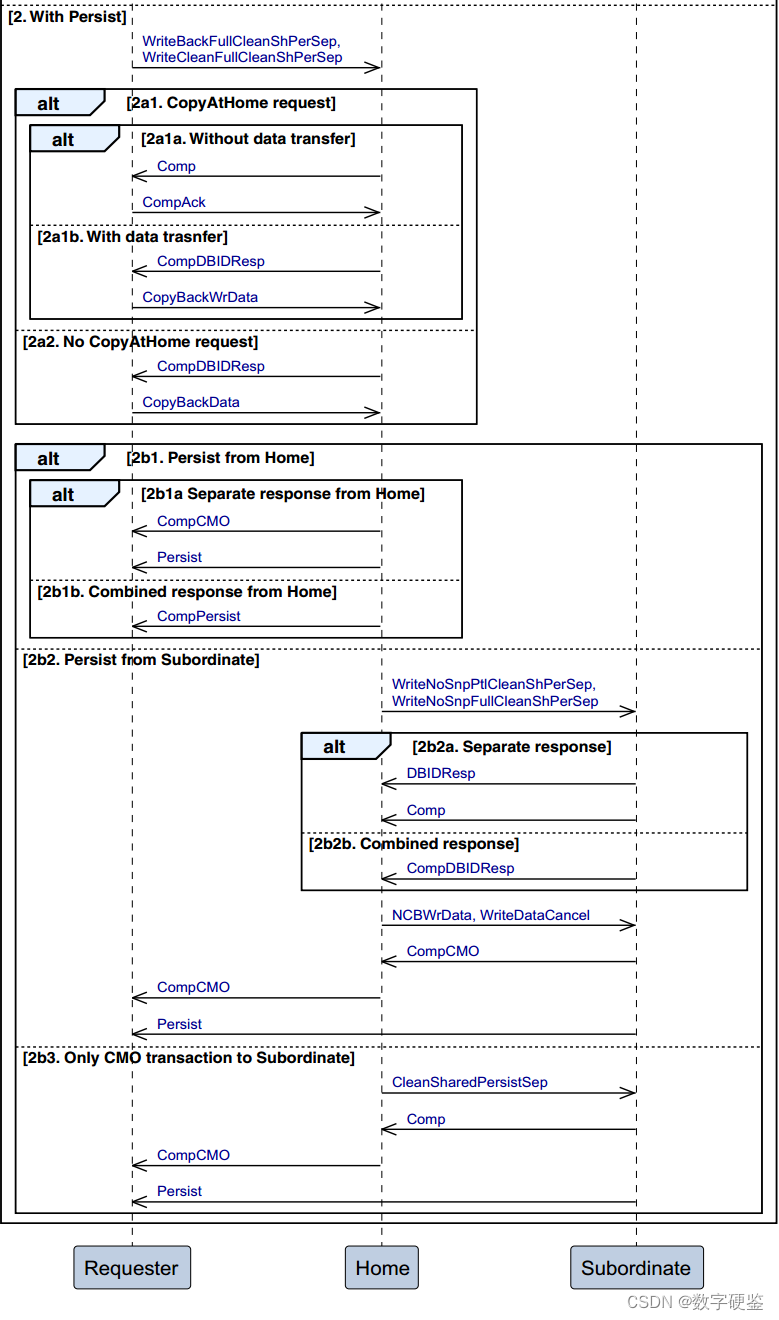

AMBA-CHI协议详解(三)

《AMBA 5 CHI Architecture Specification》 AMBA-CHI协议详解(一) AMBA-CHI协议详解(二) AMBA-CHI协议详解(三) AMBA-CHI协议详解(四) 文章目录 2.3.2 Write transactions2.3.2.1 Immediate Write2.3.2.2 Write Zero2.3.2.3 CopyBack Wr

stm32中AMBA、AHB、APB总系介绍

AMBA(advanced microcontroller bus architecture )片上总线是由ARM公司推出的。 AMBA规范主要包括了:AHB(Advanced High- performance Bus)系统总线和 APB(Advanced Peripheral Bus) 外围总线。其中,AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模

【AMBA Bus ACE 总线 9.1 -- Non-cache Master 写操作 详细介绍】

请阅读【AMBA Bus ACE 总线与Cache 专栏 】 欢迎学习:【嵌入式开发学习必备专栏】 文章目录 Non-cache MasterACE 和系统级缓存一致性ACE 非缓存主控(Non-cacheable Master) Non-cache Master ARM的ACE(AXI Coherency Extension)是一种用于增强系统级缓存一致性的接口规范

【AMBA Bus ACE 总线 7.1 -- ACE Domains 介绍 2】

请阅读【AMBA Bus ACE 总线与Cache 专栏 】 欢迎学习:【嵌入式开发学习必备专栏】 文章目录 AxDOMAINAxDOMAIN[1:0]的值及含义 AxDOMAIN 在ARM的AXI Coherency Extensions (ACE) 协议中,AxDOMAIN[1:0]是一个重要的信号字段,用于指示传输的域类型。这个字段影响了传输对系统中其他组件(如

【AMBA Bus ACE 总线10 -- ACE Barrier transaction 详细介绍】

请阅读【AMBA Bus ACE 总线与Cache 专栏 】 欢迎学习:【嵌入式开发学习必备专栏】 文章目录 ACE AxBARAxBAR[1:0]的值及含义屏障的用途和重要性 ACE AxBAR 用于表明是否是一个barrier 的transaction,对于它我们只需要有个简单的了解即可,现在已经不建议在transaction的层面上还把 barrier 的

【AMBA Bus ACE 总线 8 -- ICache maintenance】

请阅读【AMBA Bus ACE 总线与Cache 专栏 】 欢迎学习:【嵌入式开发学习必备专栏】 文章目录 ACE ICache maintenance ACE ICache maintenance 图 1-1 当一个OS run 多个cpu的时候,根据调度算法的不同,OS 可以根据调度算法的不同分别 run 在某个具体的CPU上,因此,它们会有一个mi

【AMBA Bus ACE 总线 5 -- Non-cached master】

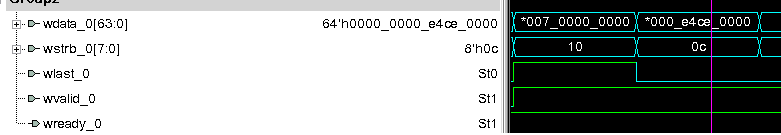

文章目录 Non-cached master Non-cached master 图 1-1 Non-cached master 意思就是,比如对于master0,它想写的时候,就直接发起transaction,它不是对自己的local cache进行操作,比如以non-shareable write 为例,master0在写的时候分别在AW,和 W channel

【AMBA Bus ACE 总线 2 -- ACE Snoop transaction】

文章目录 Snoop Transaction 简介主要类型的snoop transactionsnoop transaction的目的 ACE Snoop transaction Snoop Transaction 简介 ARM ACE (AXI Coherency Extensions) 协议中的snoop transaction是一种机制,旨在维持多核处理器系统中缓存之间的

【AMBA Bus ACE 总线 4 -- ACE Cache invalidate 操作】

文章目录 Cache Invalidate1. 数据更新2. 同步操作 ACE Cache invalidate Cache Invalidate 在ARM的AXI Coherency Extensions (ACE) 协议中,“cache invalidate” 事务用于标记一个或多个缓存行为无效,这意味着缓存中的数据不再被认为是最新的或是有效的。这种事务在多种场景中非常有用

AMBA基础知识3:AMBA-AXI总线协议详解

来自:http://blog.sina.com.cn/s/blog_13f7886010102x2iz.html AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的

AMBA基础知识2:AMBA AHB总线

来自:https://blog.csdn.net/ivy_reny/article/details/56274412 一、AMBA概述 AMBA (Advanced Microcontroller Bus Architecture) 高级处理器总线架构 AHB (Advanced High-performance Bus) 高级高性能总线 ASB (Adva

AMBA基础知识0:AMBA APB总线

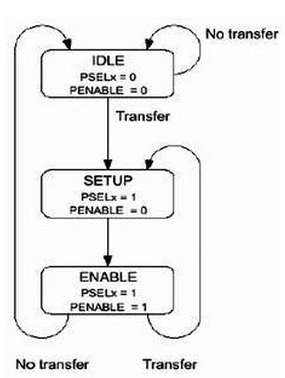

原文地址:https://www.cnblogs.com/lyuyangly/p/4853921.html (一) APB总线接口: PCLK APB总线时钟。 PRESETn APB总线复位。低有效。 PADDR 地址总线。 PSELx 从设备选择。 PENABLE APB传输选通。 PWRITE 高为写传输,低为读。 PRDATA 读数据总线

AMBA、AHB、APB、ASB总线简介

AMBA简介 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主

[转]AMBA、AHB、APB、ASB总线简介

[转]http://www.cnblogs.com/zhaozhong1989/articles/3092140.html 1.前言 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司

AMBA AHB APB ASB,处理器总线[zz]

上一张图:来自 <<AMBA总线规范>>_中文. 文章转载地址:http://www.cnblogs.com/mr-raptor/archive/2011/06/21/2347667.html The Advanced Microcontroller Bus Architecture (AMBA) specification defines an on- chip commu

1906_ AMBA_高级MCU总线架构

1906_ AMBA_高级MCU总线架构 全部学习汇总: g_arm_cores: ARM内核的学习笔记 (gitee.com) 在看内核相关的文件的时候看到了AMBA这个缩写,查了一下具体的概念。这个其实是一个总线架构,应该是ARM设计的。我找到了相关的介绍网页: AMBA – Arm® AMBA的意思是高级MCU总线架构,这个算是一个标准。这个架构不局限于处理器架构,适合开发多控制

AMBA Specification (Rev 2.0)简介

一、配置时钟时,经常看到APB、AHB,一直也没仔细关注过,抽空先粗略了解一下。 二、AMBA Specification (Rev 2.0)定义了三个总线,分别是AHB、ASB和APB。 1、AHB:Advanced High-performance Bus。 AHB is a new generation of AMBA bus which is intended to address th

【Codecs系列】AMBA CV22芯片编码流程

DATE: 2019-9-1 AMBA CV22编码流程: 建立netlink通信:目的是开启idsp,vdsp及其与arm之间的通信;打开IAV和ucode设备;系统初始化:IAV进入IDLE状态,进行Buffer,canvas和stream配置,IAV进入Preview状态。设置编码参数:在启动编码配置静态编码参数(编码器类型设置,码率控制参数初始化,GOP初始化),编码启动之后设置动

AMBA-APB协议

目录 简介传输时序Signal DescriptionsTransfersWrite transfer with no wait statesWrite transfer with wait statesRead transfer with no wait statesRead transfer with wait statesExample failing write transferEx

AMBA协议王者归来:揭秘AHBAPB设计奥秘

AMBA协议已经成为业界的事实标准,因此在市场上有大量可重用的AMBA兼容IP核。IC工程师掌握这些总线,可以更容易地集成来自不同供应商的IP核,降低开发成本,缩短产品上市时间。 AMBA 高级微处理器总线架构,定义了高性能嵌入式微控制器的通信标准,可以将RISC处理器(精简指令集处理器)集成在其他IP芯核和外设中,它是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件;它不是芯片与外设

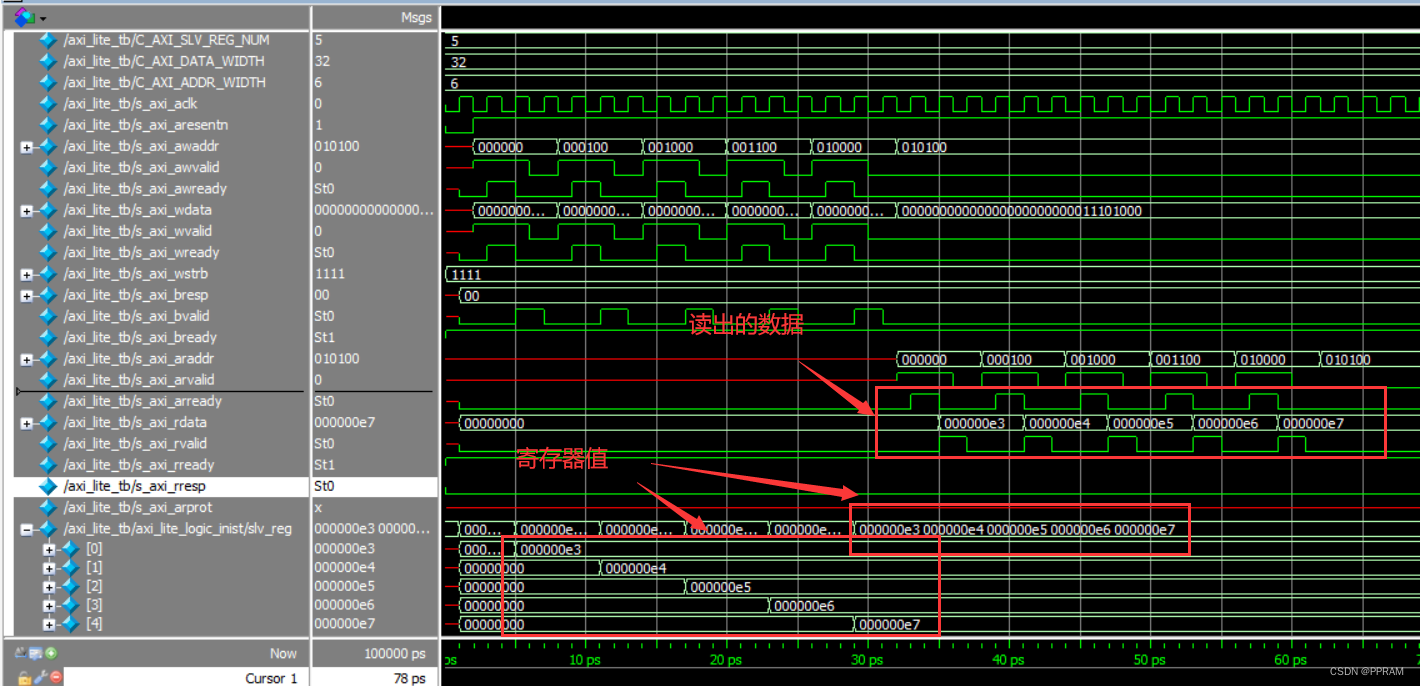

AMBA协议AXI-Lite(AXI-Lite从机代码设计)

文章目录 一、设计思路1、什么时候发生写数据操作?2.什么时候发生数据读操作?3.如何根据AXI_WSTRB信号完成数据的写入? 二、源码设计2.1 写通道源码设计2.2 读通道源码设计2.3 模板代码 三、仿真总结 一、设计思路 在设计开始之前,我们需要弄清楚以下几个问题: 什么时候发生写数据操作?什么时候发生数据写操作?如何根据AXI_WSTRB信号完成数据的写入?

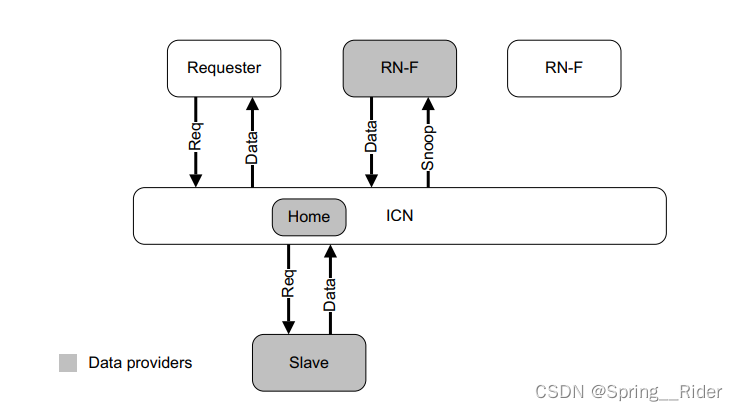

AMBA 5 CHI 协议节点实例和读数据的来源

1. CHI协议节点实例 如上图所示,RN-F、RN-I、HN-F、SN-F、HN-I、SN-I通过内部互联总线连接起来。这里的ICN可以是CMN-700。其中SN-F和SN-I是连接主存,RN-F和HN-F内部都有cache。 2. CHI读数据的可能来源 如上图所示,CHI协议中可能的读数据来源包括了RN-F、HN-F 以及 SN-F 这3个device。 SN-F到RN-F的

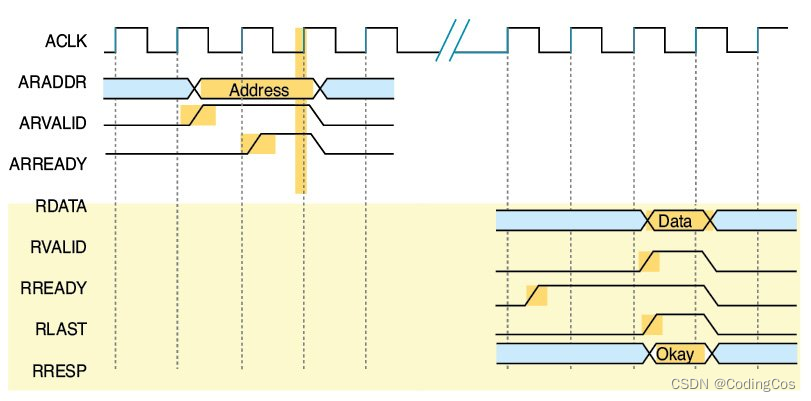

【ARM AMBA AXI 入门 13 -- AXI 协议中 RRESP 信号详细介绍】

请阅读【ARM AMBA AXI 总线 文章专栏导读】 文章目录 AXI 协议中 RRESP 信号RRESP 使用举例RRESP 3bit 使用 AXI 协议中 RRESP 信号 在 AXI (Advanced eXtensible Interface) 协议中,RRESP 信号用来表示读取事务的响应状态,它由从设备(Slave)发往主设备(Master)来通知读取操

![[转]AMBA、AHB、APB、ASB总线简介](https://images2015.cnblogs.com/blog/1138116/201706/1138116-20170617124000040-1467221927.png)

![AMBA AHB APB ASB,处理器总线[zz]](http://hi.csdn.net/attachment/201106/21/0_13086284839u8I.gif)