本文主要是介绍AMBA问题汇总,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

再看AMBA协议时有些问题,模糊的地方,记在这里反复看看,时刻提醒。好多问题和解答都是转自amba社区!

1问:

Regarding AMBA AXI4 Write Strobe port

Hi All,

I am completely new to AMBA AXI4 protocol. I am unclear about exact functionality of Write Strobe (WSTRB) port in write data channel. According to Specification,

we are calculating Lower_Byte_Lane and Upper_Byte_Lane (on page A3-47) to identify valid bytes present on write data bus (WDATA).

For Example, if we have aligned address 0x00, transfer size = 32 bits and data bus of 64-bits, we have valid data present on WDATA[31:0] and WDATA[63:32] will

be ignored during first transfer in a burst. So in this case, Master should drive 0x0F on WSTRB port as we are expecting data on lower 32-bits according to Lower_Byte_Lane

and Upper_Byte_Lane calculation.

My question is that we are determining valid byte lanes based on Lower_Byte_Lane and Upper_Byte_Lane calculation. So what is the significance of WSTRB port?

When we have to consider WSTRB port value in AXI4 slave? And at the same time, do we need to ignore Lower_Byte_Lane and Upper_Byte_Lane values?

One more query: During read data phase, do we need to send read data in particular byte lanes on RDATA bus depedning upon Lower_Byte_Lane and

Upper_Byte_Lane values? Please confirm.

Thanks & Regards,

Tejas

1答:

Hi All,

I am completely new to AMBA AXI4 protocol. I am unclear about exact functionality of Write Strobe (WSTRB) port in write data channel. According to Specification,

we are calculating Lower_Byte_Lane and Upper_Byte_Lane (on page A3-47) to identify valid bytes present on write data bus (WDATA).

For Example, if we have aligned address 0x00, transfer size = 32 bits and data bus of 64-bits, we have valid data present on WDATA[31:0] and WDATA[63:32] will

be ignored during first transfer in a burst. So in this case, Master should drive 0x0F on WSTRB port as we are expecting data on lower 32-bits according to Lower_Byte_Lane

and Upper_Byte_Lane calculation.

My question is that we are determining valid byte lanes based on Lower_Byte_Lane and Upper_Byte_Lane calculation. So what is the significance of WSTRB port?

Page A3-49 of the AXI4 protocol describes "There is one write strobe for each eight bits of the write data bus, therefore WSTRB[n] corresponds to WDATA[(8n)+7:(8n)].", i.e., WSTRB[7] validates WDATA[63:56], and is the most significant bit; WSTRB[0] validates WDATA[7:0], and is the least significant bit.

Moreover, although the master could signal a 32 bit transfer on AWSIZE, the WSTRB info then tells you if all 4 bytes of the 32-bit transfer will contain valid data. For example AWSIZE=3'b010 would signal a 32 bit transfer on this 64-bit data bus, and WSTRB could signal 8'b00001001, indicating only WDATA[31:24] and WDATA[7:0] would contain valid bytes to be transferred.

When we have to consider WSTRB port value in AXI4 slave? And at the same time, do we need to ignore Lower_Byte_Lane and Upper_Byte_Lane values?

The slave needs to know both the AWSIZE and WSTRB information. WSTRB tells the slave the byte lanes containing active data (something it couldn't work out solely based on the AWADDR/AWSIZE/AWBURST combination), but AWSIZE (and AWADDR/AWBURST) is still needed to tell the slave how much the address should increment by for subsequent transfers in a burst.

One more query: During read data phase, do we need to send read data in particular byte lanes on RDATA bus depedning upon Lower_Byte_Lane and

Upper_Byte_Lane values? Please confirm.

Yes correct. Lower_Byte_Lane or Upper_Byte_Lane depend on the first transfer in a burst, i.e. the read address is 32-bit aligned or 64-bit aligned to your 64-bit data bus.

Thanks & Regards,

Tejas

2问:

AXI4 Burst Length

In AXI4 the burst length is increased from 16 to 256.

If burst type is WRAP, do this mean we can do wrap burst of 2,4,8,16,32,64,128 & 256 ?

Also if the burst type is FIXED can the burst length be more than 16 ?

2答AXI - USER and REGION Signal Width

Could you plz share some info on the USER & REGION sideband signals, viz. their usage and signal widths ?

Also can write data width and read width be different or is it always the same ?

3答The USER signals are optional 'sideband' signals that can accompany each AXI channel. The width of them is completely user-defined, as is their purpose. Since their functionality is not defined by the protocol, the use of User signals is generally not recommended as this can lead to interoperability issues if two components use the same User signals in an incompatible manner.

The AWREGION/ARREGION signals are both 4 bits wide and can be used to indicate which 'region' of a slave a transaction is targeted at.This high-level explanation is probably better clarified with a simple example of how they could be used; if a slave has (for example) an area of control registers, and a separate area of data registers, a master could indicate that a transaction is for the data area using the appropriate AxREGION signal, and the slave will not have as much decoding to do as a result.

Your last question is an interesting one because (as far as I'm aware) nothing in the protocol specification says that read and write data widths have to be the same. It would however need to be a pretty unusual design to actually benefit from doing this, and it would likely increase the complexity of working with existing components/interconnects as this isn't something that I've heard of as being supported.

Difference between AXI transfer and transaction

I ve been studying the AXI protocol and I ve come up with a small roadblock. My questions are:1.What is a AXI transfer?

2.What is a AXI transaction?

3.Difference between transfer and transaction.

4.Is a transfer made of multiple transactions or is it the other way around??

5.Is 1 beat ,1 transfer or 1 transaction?

6.Can a single transaction(transfer) occupy more than one burst(because sometimes data can be greater than 256 transfers,with each transfer having 64 bits)?

7.Finally (phew!) can a burst have more than one transaction(because sometimes data to be moved will be of a few bytes, so more than one transaction can be accomodated in one burst)

1. An AXI transfer is defined in some of the ARM documentation as

"A single exchange of information. That is, with one xVALID/xREADY handshake"

2. And an AXI transaction is then described as

"An entire burst of transfers, comprising an address, one or more data transfers and a response transfer (writes only)."

3. So from these you can see that a "transaction" is made up of lots of "transfers", with a write "transaction" including an AW "transfer", one or more W "transfers" and finally a B "transfer". A read "transaction" starts with an AR "transfer" and is followed by one or more "R" transfers".

4. It is "the other way round"

5.A beat would be 1 data channel transfer.

6. No. A "transaction" contains a "burst" of data "transfers", so a "burst" is limited to the maximum number of "transfers" allowed for that transaction type (16 for FIXED and WRAP, 256 for INCR in AXI4 or 16 for AXI3).

7. There is a "Glossary" of the terms used at the end of the AXI spec, and it describes a "Burst" as

"In an AXI transaction, the payload data is transferred in a single burst, that can comprise multiple beats, or individual data transfers."

Maybe section A1.4 in the version of the AXI spec you are looking at will help clarify all of your questions. It describes the terminology used in the spec and answers most of the questions above.

AXI write strobes

the AXI spec says:[...]

For any burst that is made up of data transfers wider than one byte, it is possible that the first bytes that have to be accessed do not align with the natural data width boundary. For example, a 32-bit (four-byte) data packet that starts at a byte address of 0x1002 is not aligned to a 32-bit boundary.

and then shows some examples of bursts with unaligned first bytes.

i also see references to disabling all strobes on any beat of a burst write.

but, what about unaligned ending bytes? for example, a burst of 1kB starting at address 0x1 would have both an unaligned starting and ending byte. is this allowed?

do the bytes of a burst have to be contiguous? could the writes strobes have holes in them, for example, 0x5, 0xa, 0x9, etc.?

also, i was wondering what AXI masters ARM has that makes use of this feature? do ARM processors ever generate unaligned bursts for instruction or data accesses, or is it only the DMA controller that issues unaligned bursts? and in what scenario would a master disable all the strobes after starting a burst write (something like interrupting a dirty line castout?)?

>but, what about unaligned ending bytes?

Wouldn't be allowed. It is only the first transfer in a burst that is unaligned, all the remaining transfers are aligned.

However for a write transaction you could use the WSTRB bits to signal which of the final bytes is valid, that way having the same effect as an unaligned final transfer in the burst. But you cannot do this for reads.

> for example, a burst of 1kB starting at address 0x1 would

> have both an unaligned starting and ending byte. is this allowed?

No. The final transfer would be aligned.

> do the bytes of a burst have to be contiguous? could the writes

> strobes have holes in them, for example, 0x5, 0xa, 0x9, etc.?

The write strobes can change for each transfer of a burst, so you could see the above sequence.

> also, i was wondering what AXI masters ARM has that makes

> use of this feature?

I am not aware of any current ARM masters that use the WSTRBs to indicate sparse transfers, but maybe someone else will know more about specific ARM master designs.

The important word here is CAN. The AWADDR and AWSIZE signals tell you the range of byte lanes that CAN be used, but the WSTRB bits would say which specific possible byte lanes ARE being used in each beat of the FIXED burst.

So WSTRB could be used to make the FIXED burst appear to be unaligned (even though the AWADDR value actually IS aligned.

Obviously if AWSIZE indicated a 32 bit transfer, even with a bus width of 64 bits we could only use WSTRB[3:1] for this transfer to AWADDR=0x1.

Why The address is same for each transfer of transaction in fixed burst of AXI 3 or 4?

In AXI 3/4, let us assume a transaction has 4 transfers.

for example 1st transfer of write transaction address location is 2000 with data of 20.

2nd transfer of write transaction address location is also 2000(as per Spec) with data of 40.

Here My Question is that 1st transfer data is overwrite by 2nd transfer of write transaction i,e in 2000 address location data 40 only available. Is it correct?

After sending two transfers of write transaction to the same address location, Can i read data of 1st transfer of write transaction by using same address location?

In Fixed Burst we need to do write transfer first and read transfer immediately then only operation will be fine. Is it correct?

Whether we can do continuous write transfers first and then continuous read transfers in fixed burst?

In the above case(continuous write & continuous reads) i will have only last write transfer of transaction in address location that can be readed multiple times. Is it correct?

6答You're correct about what the FIXED burst does (multiple reads or writes to the same address). The question is why it would be a useful thing to do. The typical example is the on I mentioned in the other thread - accessing a FIFO.

Imagine you had a piece of hardware that acted as a message queue. Every time you write to it you push another message onto the queue. Every time you read from it you pop the next message off the queue. You could use a FIXED write to push multiple message onto the queue, or use a FIXED read to pop multiple messages off the queue.

Suppose start address is 55, assuming 32 - bit bus, burst length of 4

Aligned_Address = (INT(Start_Address / Number_Bytes) ) * Number_Bytes;

The value is :: 52 or 56 i.e. do we have round to lower or upper value.

Then we calculate the wrap boundary, using

Wrap_Boundary = ((INT(Start_Address / (Number_Bytes * Burst_Length))) * (Number_Bytes * Burst_Length);

What does this wrap boundary actually indicate,

1. The address from where wrapping will take place.

2. The address value after wrap.

Also, if anyone can let me know in a step-wise manner how the address are calculated using the same scenario above, would be great.

Hope to see the replies soon.

The formula in the spec if for calculating the Aligned address in the wrap, not for aligning the start address - that must be aligned by the master making the access.

For a 4-byte beat your start address must be 4-byte aligned. 55 is not. To repeat what I said before:

[snip]

Start_Address needs to be aligned on the beat-size, so for a 32-bit beat it needs 4-byte aligned, 16-bit beat needs to be 2-byte aligned, etc. In this case your start address (55) is not a valid Start_Address for a 32-bit beat - ..., 52, 56, 60, 64, ... would be OK for example.

[/snip]

However, assuming a start address of 56 the following calculation would apply:

Burst Len = 32-bit beat * 4 beats = 16 bytes

Aligned address:

= INT(56 / 16) * 16

= INT(3.5) * 16

= 3 * 16

= 48

Wrap boundary:

= highest byte accessed in burst

= 48 + 16 -1

= 63

Access Pattern:

= 56, 60, 48, 52

一个AXI的burst问题!

| AXI总线,burst操作,不能跨4K边界问题! 在Master_A设计中,假如Master_A只操作一块64M SDRAM(此Master_A不操作任何其他Slave),读写的数据量远远大于4K。因此其中某个Burst的操作可能 会出现在4K边界上。 请问: 在这样的情况下,Master_A设计的Burst操作是否需要遵守4k边界的约定。 |

4K对齐,以32位地址为例,[31:12]相等的地址都是同一个page,没有跨4K边界。 即[11:0] 可以为0~0xFFF. 例如0x1000和0x2000就是在不同的page,跨了4K边界。0x1000和0x1FFF则是在同一个page,没有跨4K边界。同理,0x1FFF和0x2000则跨了4K边界,虽然他们是相邻的byte。

再说到一次burst没有4K大小,但是如果起始地址是0x1FFC, INCR模式,会跨边界吧?

1K对齐,就是说 [31:10]相等的地址都是在一个1K对齐的空间内。

至于真的跨越了,就拆分。例如处理器load多个数据,就是跨页访问,到了接口控制模块,也会把这一个访问拆分成两个访问。在interfere上的都是符合协议的transaction。例如,core要访问0x1FF0-0x200C共32byte的数据(每次beat 4B)。系统会自动给拆分成0x1FF0-0x1FFC和0x2000-0x200C两个transaction。

9问

如果初始地址不对齐(即最低位不和size对齐),发第一次的data时:用到上一个size对齐的所有strobe位,还是只是第一次与意义的位数?

9答

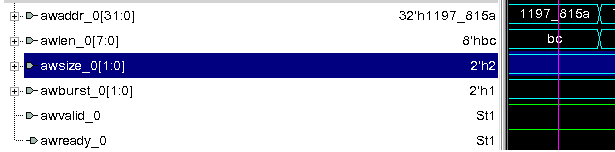

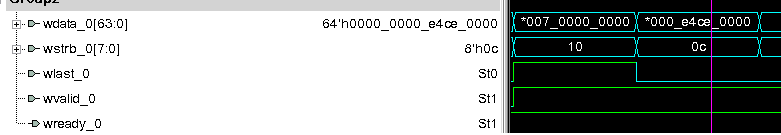

应该是后者,第一次只是有意义的位,看下图。第二次之后又开始对齐,没什么好说的。

这篇关于AMBA问题汇总的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!