本文主要是介绍西南科技大学数字电子技术实验七(4行串行累加器设计及FPGA实现)FPGA部分,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、实验目的

1、掌握基于Verilog语言的diamond工具设计全流程。

2、熟悉、应用Verilog HDL描述数字电路。

3、掌握Verilog HDL的组合和时序逻辑电路的设计方法。

4、掌握“小脚丫”开发板的使用方法。

二、实验原理

三、程序清单(每条语句必须包括注释或在开发窗口注释后截图)

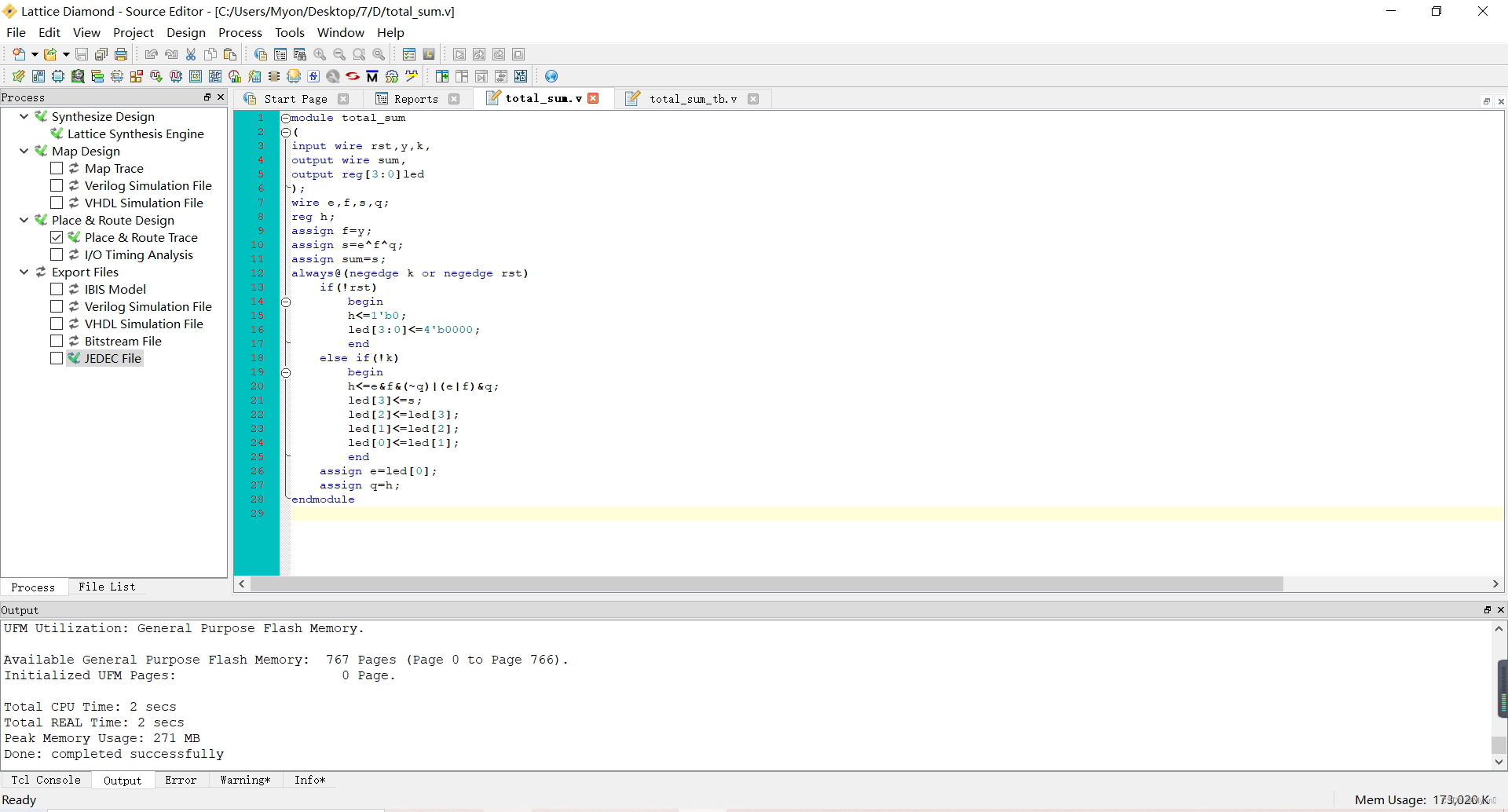

逻辑代码:

module total_sum

(

input wire rst,y,k,

output wire sum,

output reg[3:0]led

);

wire e,f,s,q;

reg h;

assign f=y;

assign s=e^f^q;

assign sum=s;

always@(negedge k or negedge rst)

if(!rst)

begin

h<=1'b0;

led[3:0]<=4'b0000;

end

else if(!k)

begin

h<=e&f&(~q)|(e|f)&q;

led[3]<=s;

led[2]<=led[3];

led[1]<=led[2];

led[0]<=led[1];

end

assign e=led[0];

assign q=h;

endmodule

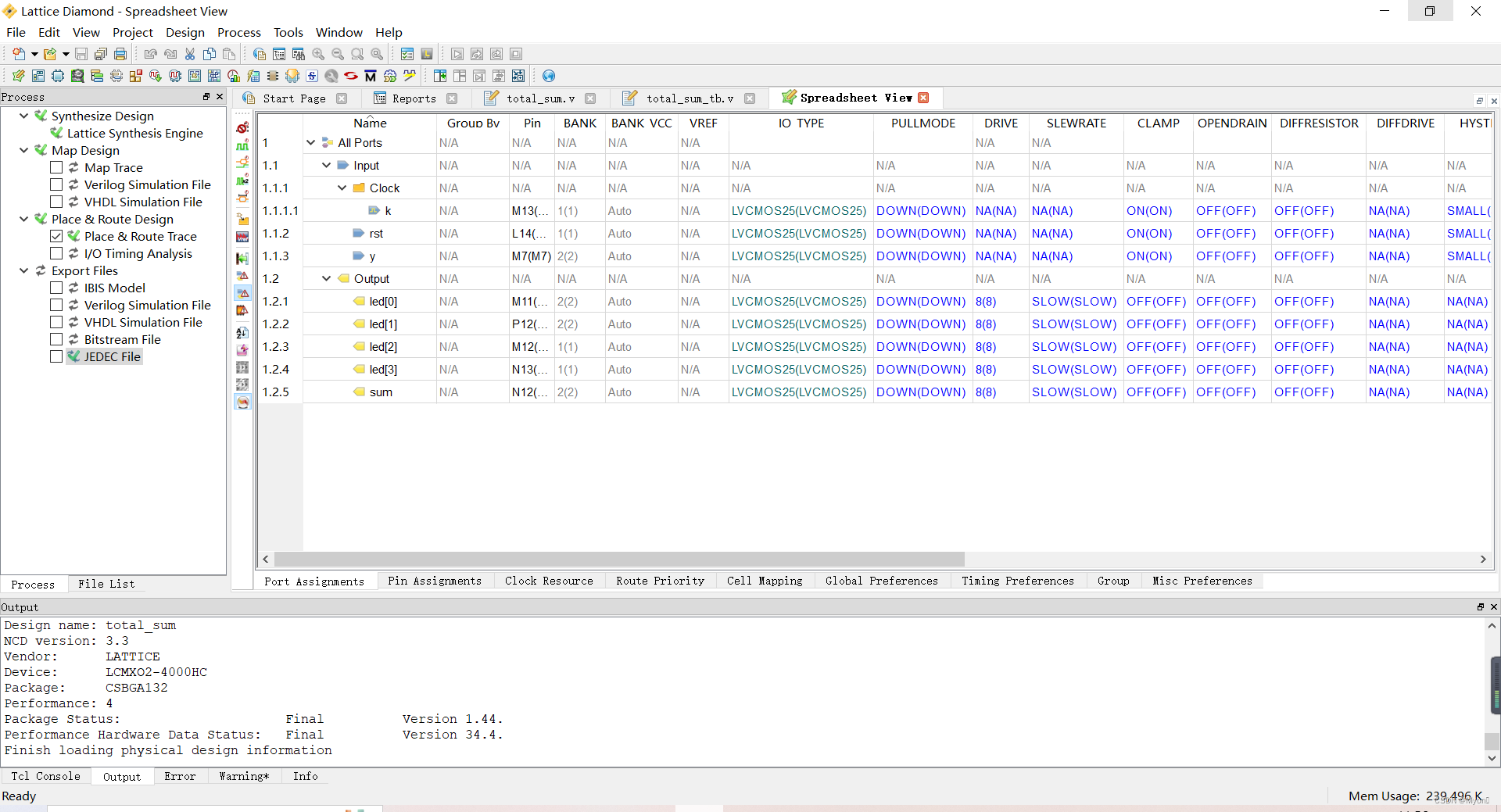

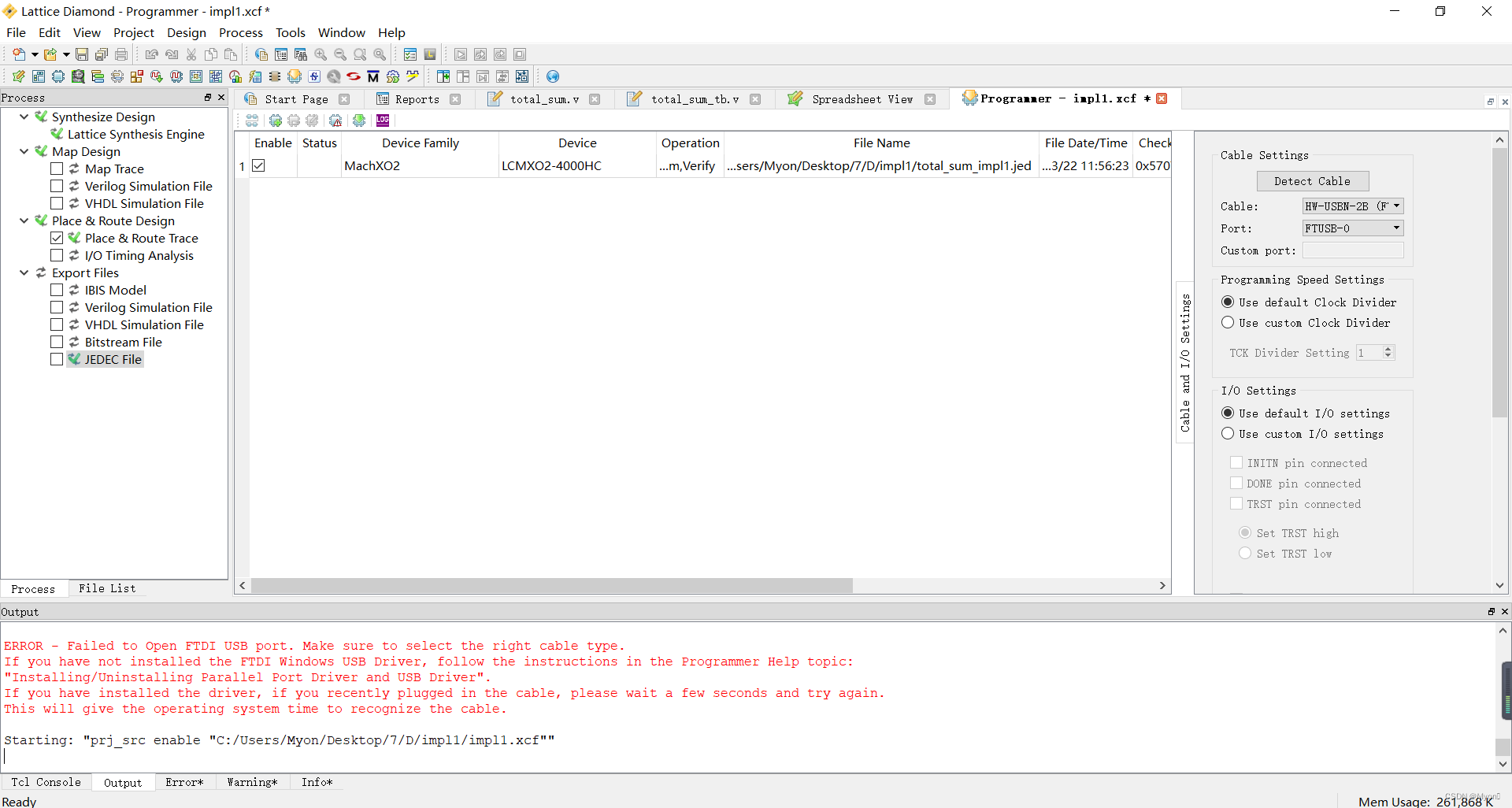

四、综合、管脚分配、生成输出文件、下载(所有步骤截图)

综合:

管脚分配:

小脚丫已被收回,无法进行文件传输

五、仿真程序清单、波形(波形截图必做,截图!)

仿真程序清单:

`timescale 1ns/1ns

module total_sum_tb;

reg rst;//复位键

reg k;//开关

reg y;//输入的数据

wire [3:0] led;//小灯

wire sum;

initial //开始

begin//对一些参数初始化

#10 rst=1; k=1;

#10 rst=0; //复位

#10 rst=1;y=1;

#10 k=0; //在k=1时输入1,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入0,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入1,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入0,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入1,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入1,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入0,并在k=0时运算

#10 k=1;y=1;

#10 k=0; //在k=1时输入0,并在k=0时运算

end

total_sum u1

(

.k(k),//开关

.rst(rst),//复位

.y(y),//输入

.sum(sum),//观察输出

.led (led)//小灯

);

Endmodule

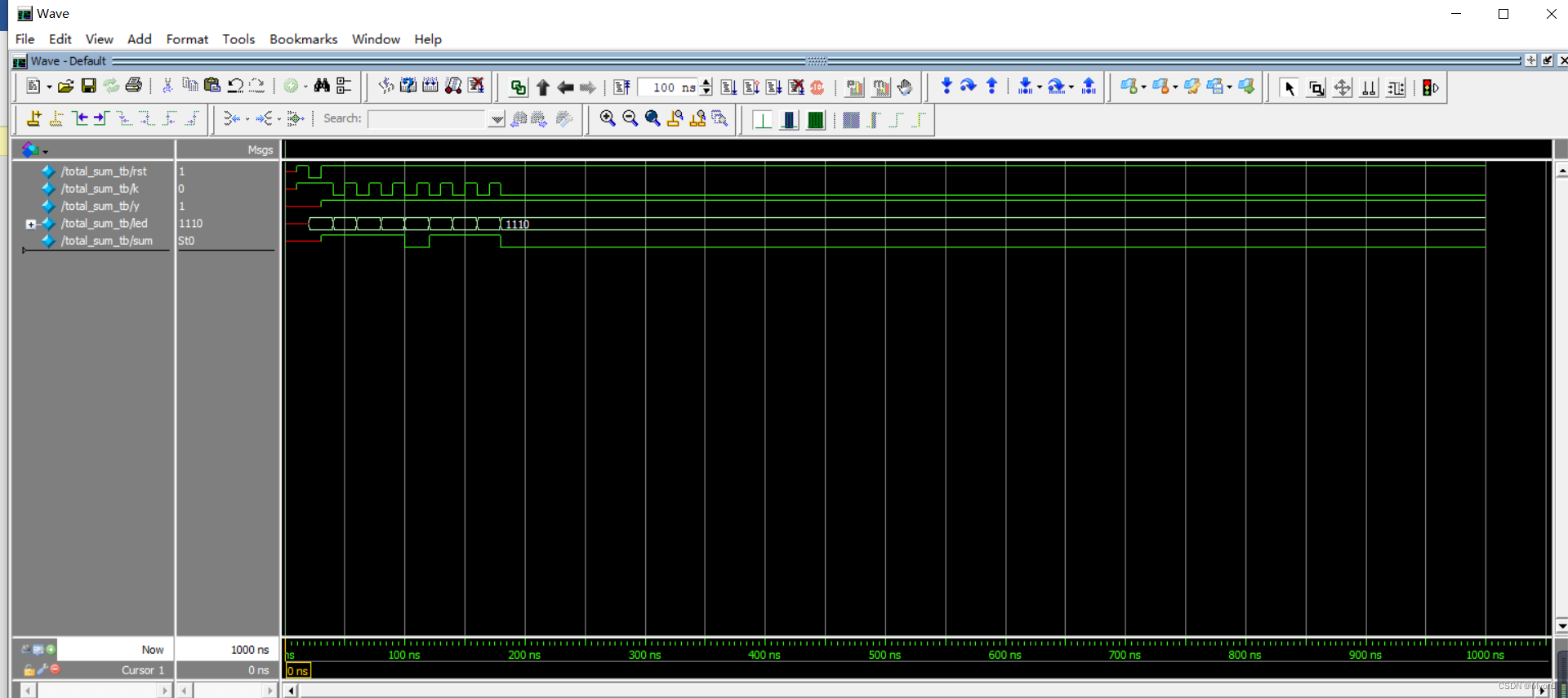

波形图:

六、思考与体会

通过本次实验,我进一步理解了用Verilog语言对FPGA进行了编程的过程与其所需要注意的一些要点,能自己设计出四位串行累加器,并且用FPGA实现了本次实验的内容,经过验证,与仿真结果一致,满足累加器的基本功能,做实验设计时,应该按步骤设计,首先列真值表,根据真值表列出逻辑函数表达式并化简,再根据化简了的逻辑表达式画出逻辑电路图,选择适当的电路芯片合理布线设计实验线路,最后根据路线写代码。在实验练习的巩固下,我对相关的理论知识有了更深刻的记忆和运用。

这篇关于西南科技大学数字电子技术实验七(4行串行累加器设计及FPGA实现)FPGA部分的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!