本文主要是介绍cadence allegro 17.2 design outline的使用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

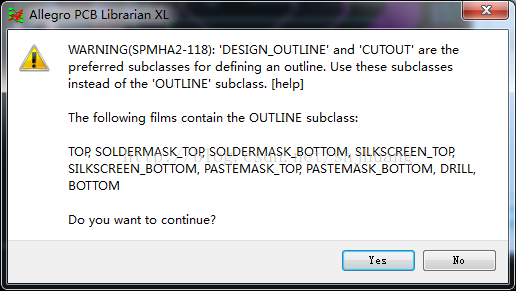

在cadence allegro 17.2 之前,电路板的外观、内部开窗、开孔等均可以通过Board Outline层定义得到。但是到了17.2之后,在输出Artwork的时候,会提示错误对话框,如下:

提示使用DESIGNED_OUTLINE和CUTOUT层来定义你的电路板外观。

当然,你不理会它这个提示,照样使用Board Outlinel来定义电路板外观也是可以的,毕竟输出Gerber文件后,电路板厂家才不管你的软件是怎么定义的呢。

但是你要面临两个问题(我目前发现的)。

1. 每次输出Gerber文件都会跳出上述对话框,很烦人。

2. 输出3D图形的时候,看不到电路板哦。

解决的办法就是老老实实使用Designe Outline层定义电路板尺寸、内部开窗等。如何使用?

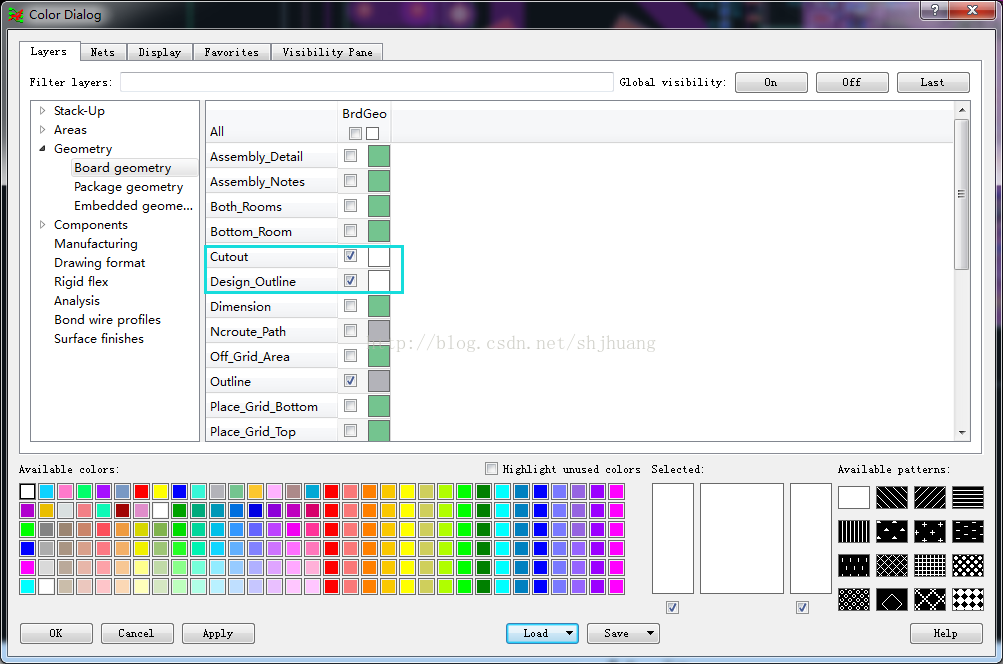

1. 在颜色选择对话框将上述两层颜色打开。

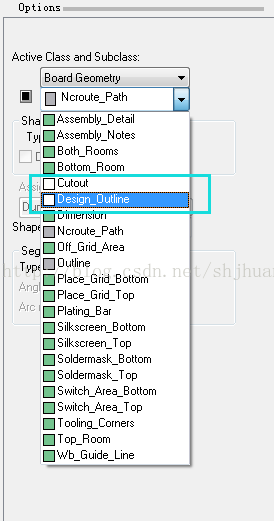

2. 放置电路板外观,及Design Outline,这个和17.2之前的版本不一样,不能使用画线的方式添加Designe Outline,因为画线时在Board Geometry类中并未能找到Design Outline或Cutout子类。只能通过添加shape的方式添加。

3. 与Board Outline不同的是,电路板内开窗不能使用Design Outline,而是使用Cutout来定义,操作方式参考上面第二点。

以上,就是使用Design Outline和Cutout定义电路板外观的操作方式。

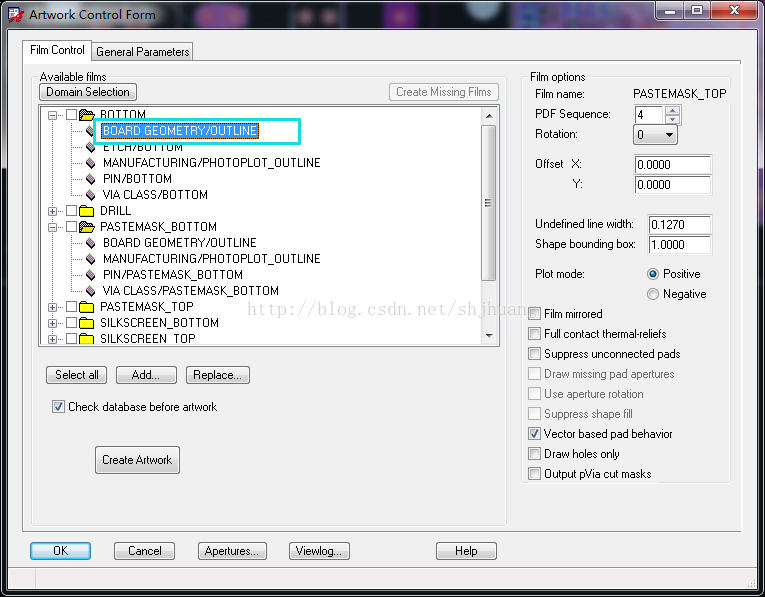

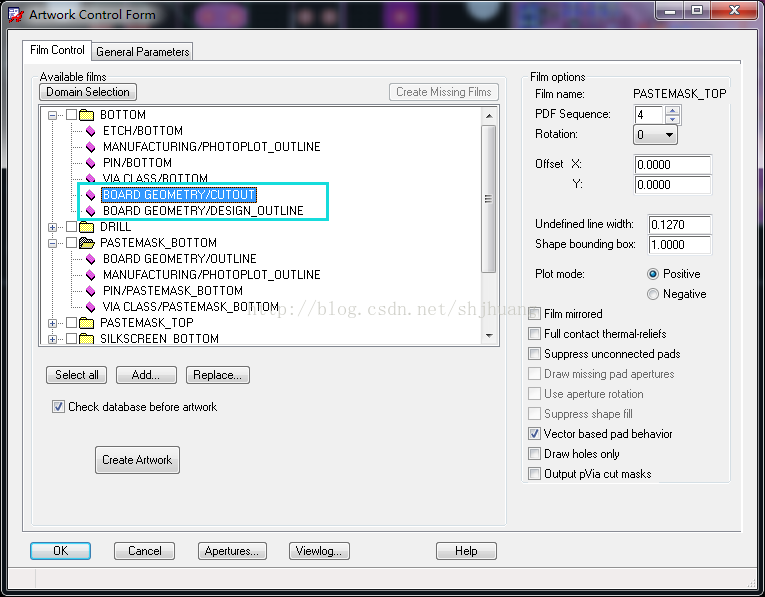

最后你需要去掉刚才收到的那个烦人的对话框,做法就是:打开Artwork Control Form将每层的BOARD GEMOETRY/OUTLINE去掉,替换成DESIGN OUTLINE和CUTOUT即可。

这篇关于cadence allegro 17.2 design outline的使用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!