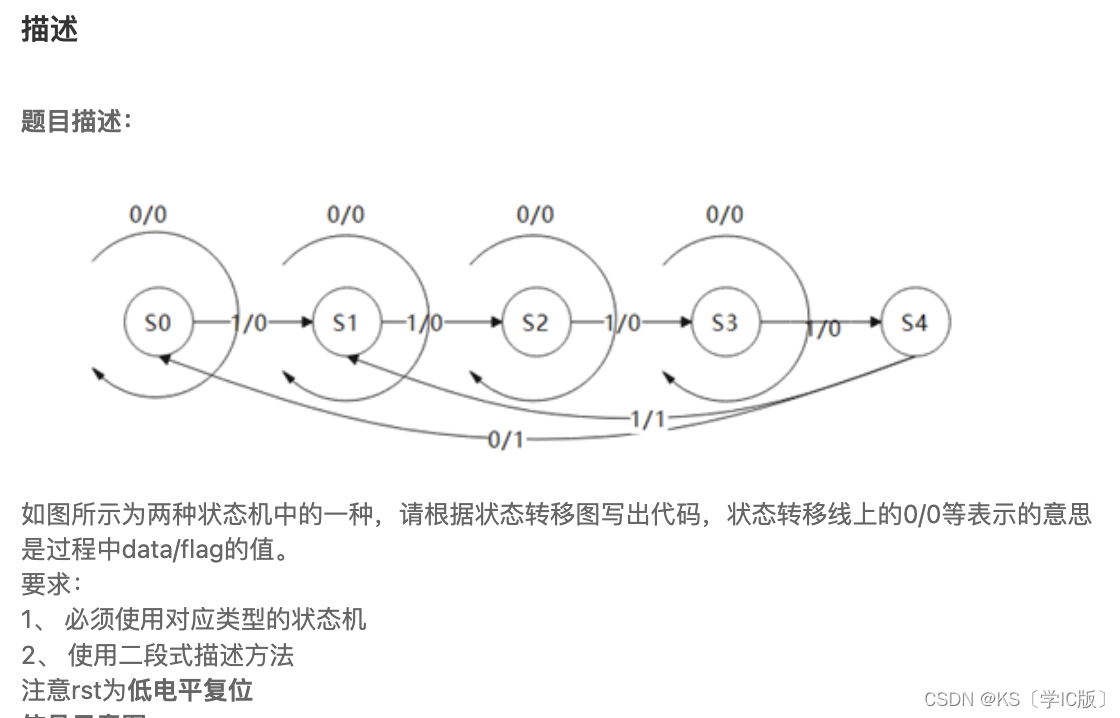

本文主要是介绍「Verilog学习笔记」根据状态转移写状态机-二段式,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

和三段式相比,就是将输出块和次态切换块合并。

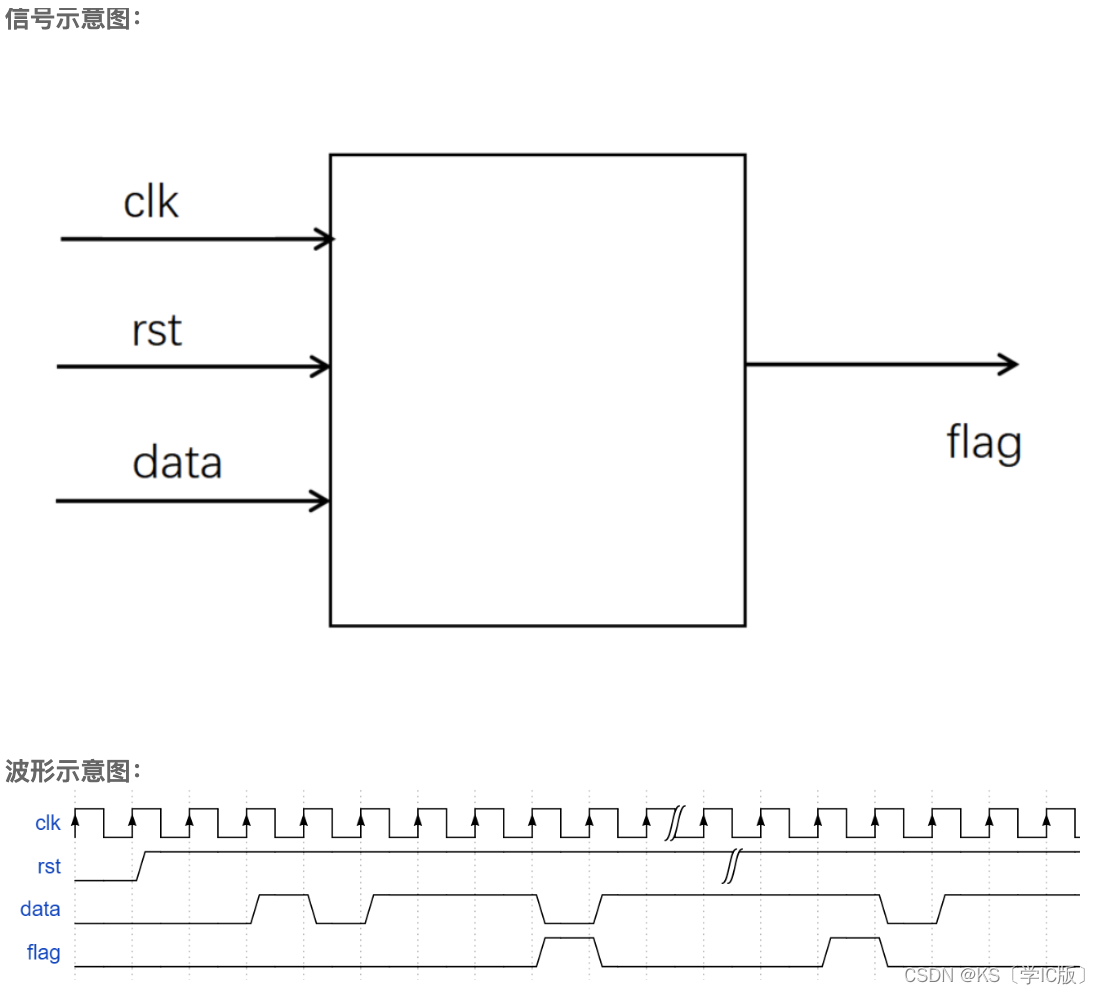

`timescale 1ns/1nsmodule fsm2(input wire clk ,input wire rst ,input wire data ,output reg flag

);//*************code***********//parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3, S4 = 4 ; reg [2:0] nstate, state ; always @ (posedge clk or negedge rst) begin if (~rst) state <= 0 ; else state <= nstate ; endalways @ (*) begin if (~rst) begin nstate <= S0 ; flag <= 0 ; endelse begin case (state) S0 : begin nstate = data ? S1 : S0 ; flag = 0 ;endS1 : begin nstate = data ? S2 : S1 ; flag = 0 ; endS2 : begin nstate = data ? S3 : S2 ; flag = 0 ; endS3 : begin nstate = data ? S4 : S3 ; flag = 0 ; endS4 : beginnstate = data ? S1 : S0 ;flag = 1 ; enddefault : beginnstate <= S0 ; flag = 0 ; endendcaseendend//*************code***********//

endmodule这篇关于「Verilog学习笔记」根据状态转移写状态机-二段式的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!