本文主要是介绍IC-FPGA类-2018年中总结暨2019年flag,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

2018年最后一个工作日了,简单写一篇,算是纪念吧。

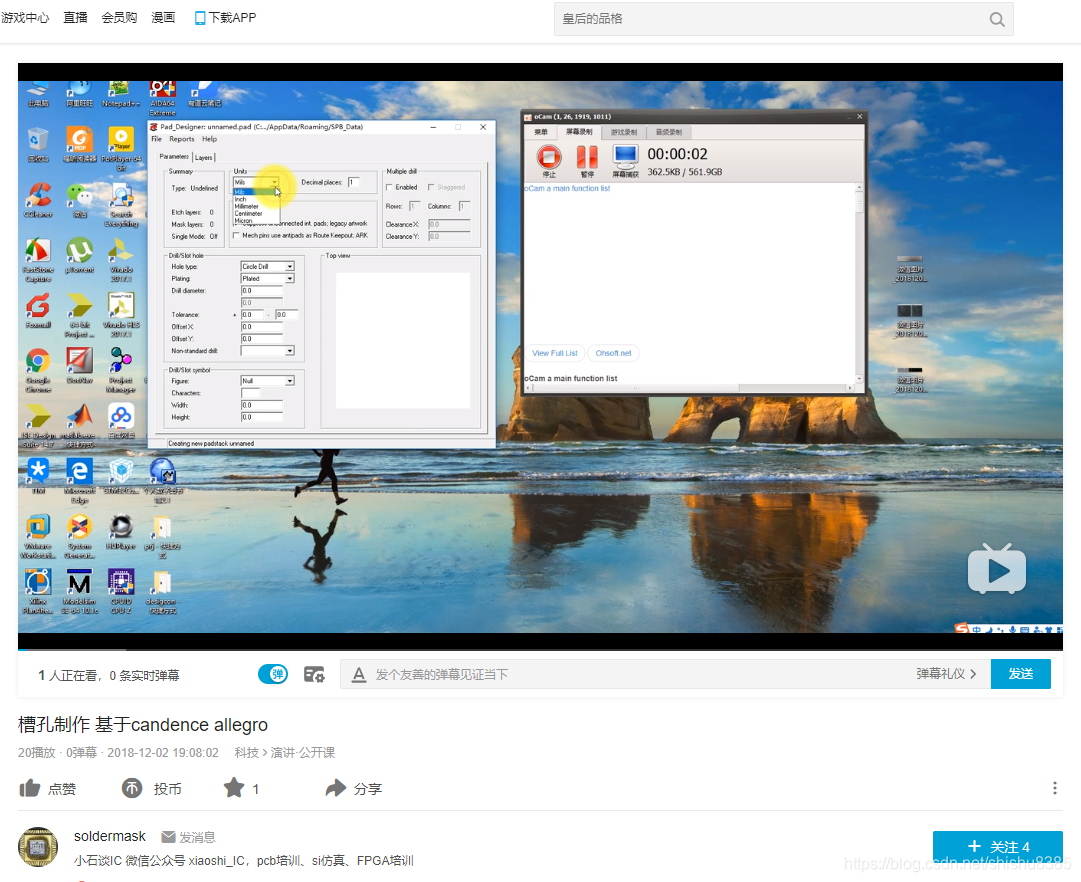

2018年,这年换了工作和方向,一路跌跌撞撞走来,开通了微信公众号,到现在217个订阅,在youtube,B站建立了视频分享,在csdn,知乎建立了自己的主页,也算迈出了自己的第一步。

youtube系列视频:

https://www.youtube.com/watch?v=BhqKdtRLNu4&t=69s

B站系列视频:(同步)

https://www.bilibili.com/video/av37263521

知乎主页:

https://www.zhihu.com/people/shishu8385/activities

CSDN主页:

https://blog.csdn.net/shishu8385

2019,在开源的这条小路上,继续沿着这条路走下去,希望一切顺利。

本公众号长期聚焦于:嵌入式软件(c语言)开发,信号&电源完整性,模拟电路版图,高速模拟电路&系统协同封装(SiP)&仿真&工程实现,模拟集成电路,数字电路后端设计,数字电路设计,电源系统&芯片级(AC-DC,DC-DC),板级射频系统性能优化,硬件板级系统研发。

由于要生存,开源不等于免费,但我会尽最大努力免费,毕竟做这些,还是太耗费精力了,再者,免费的东西有时也不被重视。

2019年侧重点在于:verilog数字设计(FPGA,少量IC),软件无线电通信算法(matlab和verilog实现,基于HackRF和USRP),通信原理基础知识分享(书籍+matlab),等

基本路线设计:

数字ic,FPGA设计,进阶,简单的接口设计->状态机设计->静态时序分析->各模块设计(异步FIFO,等)算法->matlab理解通信原理->bilibili(哔哩哔哩)matlab教程->FFT原理->FFT算法->通信IC设计

争取能完成一个从零到有的一个通信系统的设计,同时伴随视频,工程,源码。

喜欢就关注我的微信公众号吧。 xiaoshi_IC

喜欢就关注我的微信公众号吧。 xiaoshi_IC

喜欢就关注我的微信公众号吧。 xiaoshi_IC

喜欢就关注我的微信公众号吧。 xiaoshi_IC

喜欢就关注我的微信公众号吧。 xiaoshi_IC

这篇关于IC-FPGA类-2018年中总结暨2019年flag的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![BUUCTF靶场[web][极客大挑战 2019]Http、[HCTF 2018]admin](https://i-blog.csdnimg.cn/direct/ed45c0efd0ac40c68b2c1bc7b6d90ebc.png)