本文主要是介绍FPGA_单引脚输入输出-三态,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

FPGA_单引脚输入输出-三态

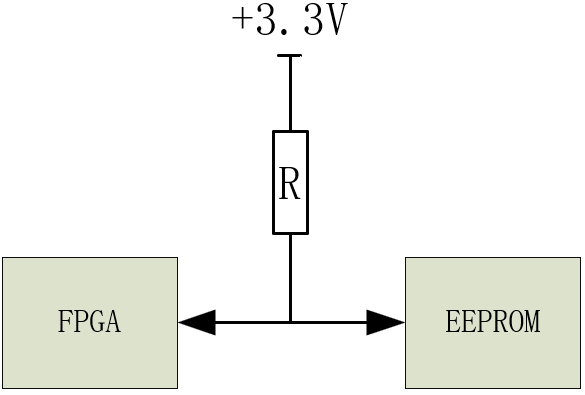

以常见的I2C协议通讯方式讲解,SDA线既可以接收数据也可以发送数据, I2C 发送写控制命令,在空闲状态时,我们给 I2C 数据方向控制(sda_dir)信号赋值高电平,将 sda 总线的方向设置为主机 FPGA 输出数据。至于我们为什么要定义一个 I2C 数据方向控制信号,是因为数据线 SDA 是双向的,如下图所示,为了避免主机、从机同时操作数据线,可以在 FPGA内部可以使用三态门结构避免此事件发生。

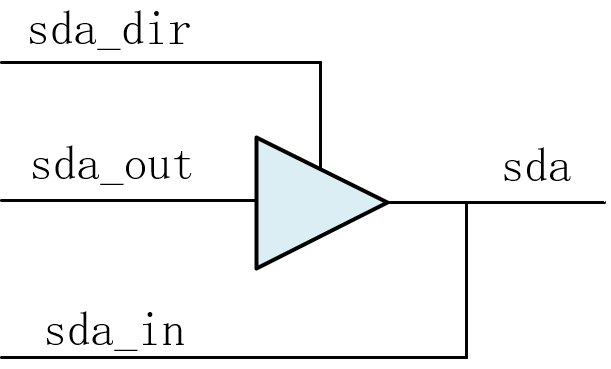

sda_dir 表示 I2C 数据方向,为 1 时表示主机(FPGA)输出信号,为 0 时 FPGA 输出高阻态,表示释放控制权。如下图所示:

所以在 I2C 单次写操作,既每次 FPGA 输出数据时,在进行数据传输之前都需要先将 sda_dir 信号拉高,在数据传输完成后再将 sda_dir 信号拉低,将 SDA 总线的控制权交给从机发送响应数据。

实现方式

assign i2c_sda = i2C_sda_dir?(i2C_sda_out?1'1bz:0): 1'1bz;

这篇关于FPGA_单引脚输入输出-三态的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!