本文主要是介绍ALTERA千兆网IP核Triple-Speed Ethernet使用方法,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、实验实现功能

本文仅实现最简单的fpga向电脑主机发送hello world,UDP包,每隔一秒发送一次。上板跑通,可证明整条传输链路打通,对IP核的配置及使用是正确的。主要参考文献是altera官方的ug 01008"Triple-Speed Ethernet Intel FPGA IP User Guide".读者需对以太网OSI分层模型有基本的了解。需要知道物理层帧格式、IP层包格式以及UDP报文格式。这个在UG01008的附录内也有介绍。

二、数据流以及控制流

搭建nios片上系统,CPU c程序通过avalon_mm总线配置千兆网(即三速以太网(Triple-Speed Ethernet,TSE)IP核,配置完成后,拉起一个PIO寄存器的值,指示逻辑模块定时发送以太网帧(物理层)。

三、工程需注意点

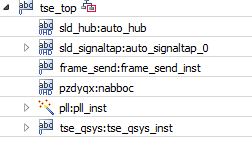

工程结构如下图

tse_top例化三个模块。

1.frame_send是定时发送以太网帧的逻辑模块,通过avalon_streanm接口连接到qsys模块tse_qsys上。

2.tse_qsys为片上系统的顶层文件,内涵nios cpu,jtag_uart,onchip mem,tse ip核以及pio等组件。

3.pll为qsys和frame_send模块以及tse_top提供数个频率的时钟。

tse_top顶层模块

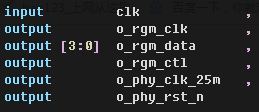

tse_top的输入输出口如下图

o_rgm_clk是rgmii接口时钟,本实验为125Mhz(TSE IP核配置为千兆模式,百兆模式下该时钟应为12.5MHz,十兆模式下应为1.25Mhz)

o_rgm_data是rgmii接口数据,位宽为4位,若ip核配置为gmii接口,则该信号为8位。rgmii接口下,ip核内例化了ddr时钟,上升沿和下降沿均可以采样数据,因而可以节省一半的数据引脚。

o_rgm_ctl是rgmii接口的控制信号,也是双沿传输的。上升沿传输发送使能,下降沿传输发送使能和发送错误的异或。

o_phy_clk_25m是发送给phy芯片的时钟,没有这个时钟,phy芯片不会工作的。

o_phy_rst_n是phy芯片的复位信号。上点后,phy芯片需要被复位。

tse_qsys模块

该模块是qsys的顶层模块。

搭建qsys系统时需要注意一下几点。

1.tse ip核内FIFO宽度设置为8bit较为方便。

2.时钟频率按照ug1008设置,即配置IP核的avalon_mm总线时钟50mhz,ip核接收逻辑端以太网帧的avalon stream总线频率100Mhz.

3.例化qsys顶层时,magic_sleep_n需设置1.ff_tx_crc_fwd需设置0.status_connection_set_10设0,status_connection_set_1000设1.

frame_send模块

该模块在nios配置完ip核后,开始定时发送以太网帧。

该模块需注意一下几点:

1.

图中,frame_length至少为64byte.

2.ff_tx_crc_fwd被设置为0后,ip核会自动为以太网帧添加FCS

3.ip核自动为帧添加preable和sfd

其他内容按照以太网帧格式生成即可。

四、c程序和实验运行流程

1.c程序按照ug1008 97页推荐配置IP核参数即可.

2.quartus内编译完工程后烧录进板子,打开wireshark设置好捕获规则,开始捕捉。然后eclipse内运行c程序,程序运行完后,逻辑模块即开始持续发送udp报文,电脑端wirehark内可捕获到来自板子的UDP报文。

这篇关于ALTERA千兆网IP核Triple-Speed Ethernet使用方法的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!