本文主要是介绍GoWin FPGA--- startup2,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

-

clock

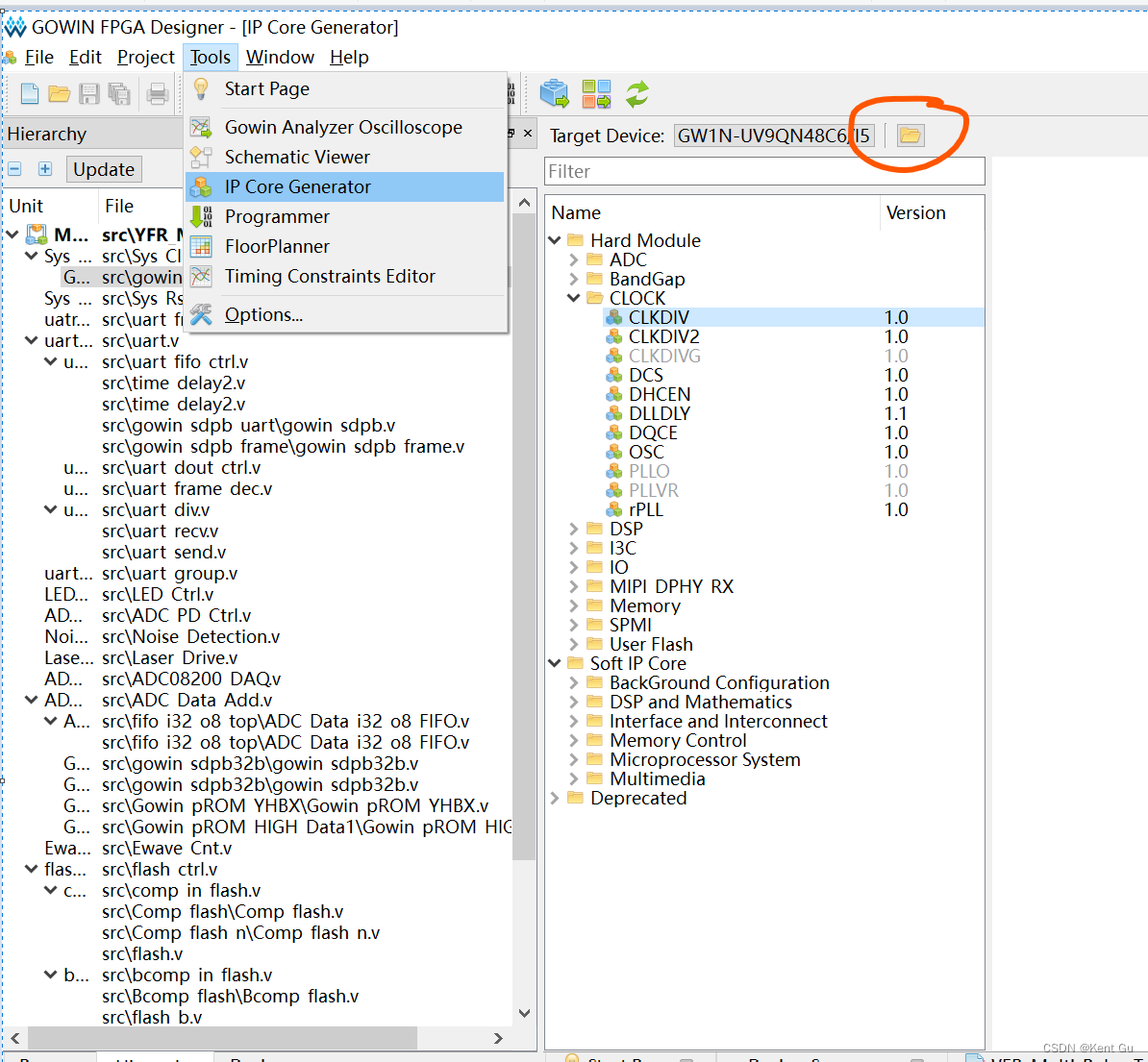

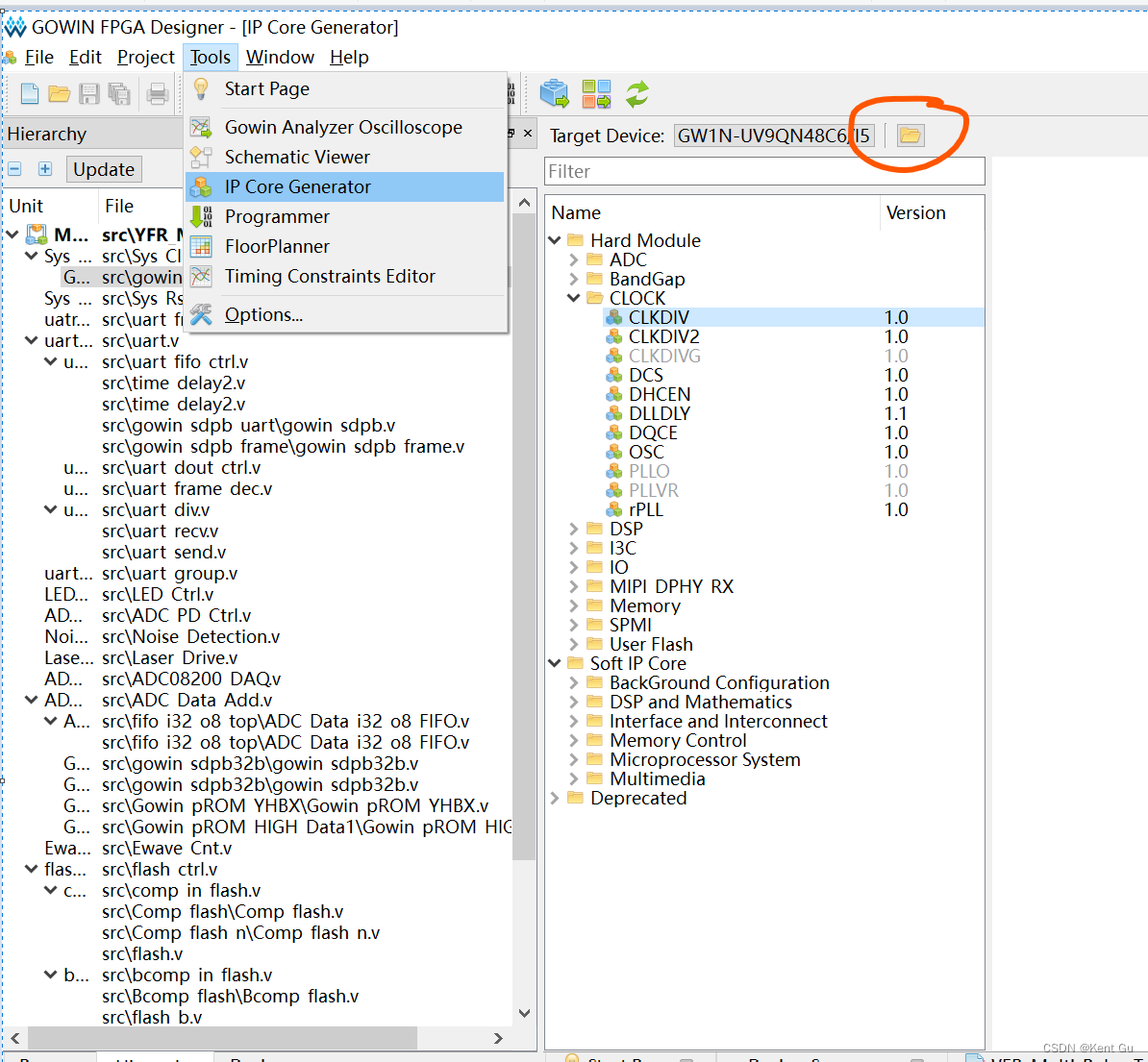

Click Tools\IP Core Generator\rPLL, and open the configure file

-

原语 for Clock

双击选项,生产对应的代码,Copy到制定的地点。

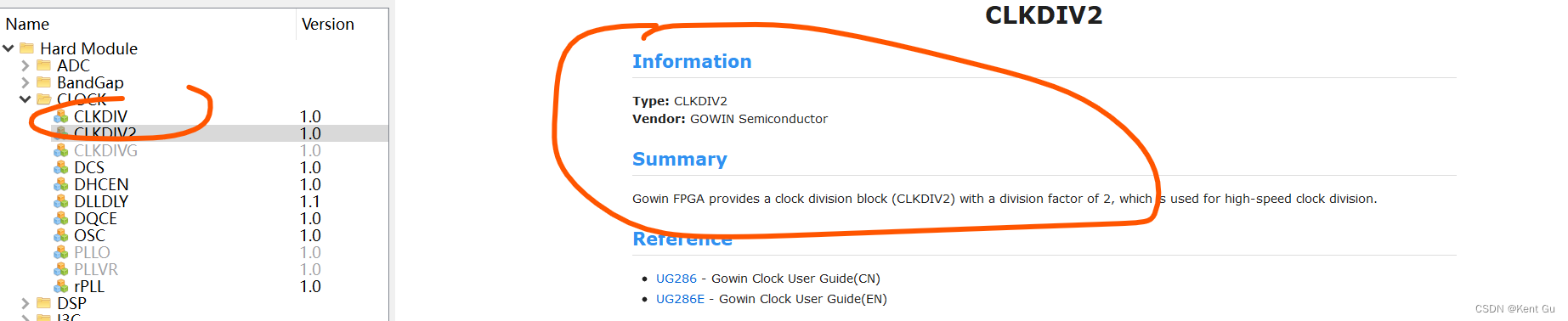

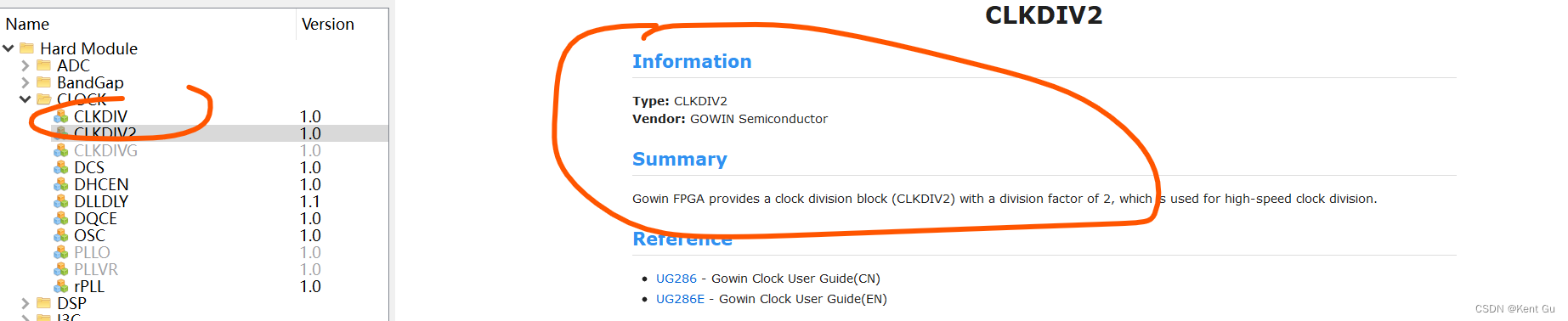

右侧有对应的说明文件

这篇关于GoWin FPGA--- startup2的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

本文主要是介绍GoWin FPGA--- startup2,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

clock

Click Tools\IP Core Generator\rPLL, and open the configure file

原语 for Clock

双击选项,生产对应的代码,Copy到制定的地点。

右侧有对应的说明文件

这篇关于GoWin FPGA--- startup2的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

http://www.chinasem.cn/article/443034。

23002807@qq.com