本文主要是介绍FPGA受冷落?英特尔端出了这个全家桶,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

▌本文来源:芯谋研究(已授权)

11月18日,英特尔的FPGA技术大会在线上举行。与其说是FPGA技术大会,可能叫“可编程”技术大会更合适。与去年爆出全球最大容量FPGA这样的猛料相比,今年的FPGA技术大会被eASIC抢了不少风头,FPGA方面最主要的更新就是软件堆栈。

FPGA在英特尔的存在感越来越低了吗?它真的融入英特尔的架构体系中了吗?

开放式FPGA堆栈是一步什么棋?

先从这次发布的开放式FPGA开发堆栈(英特尔OFS)说起。交付灵活平台的核心是硬件开发人员,英特尔牢牢抓住了这点。

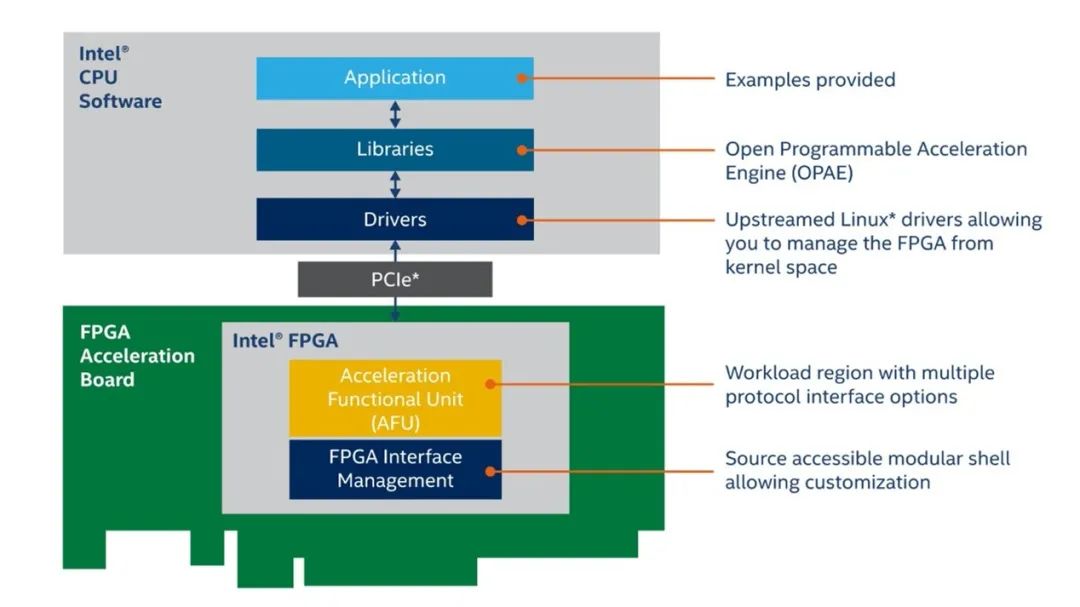

最新发布的开放式FPGA堆栈,是采用开源方法交付的可访问源代码的软硬件代码集合,可支持开发人员根据自身设计要求进行调整。代码本身将完全开源,并向上溯流至 Linux 内核,面向整个社区开放。还有模块化硬件源代码,可与行业标准接口进行组合,支持更加轻松地构建特定于应用的解决方案。

对于任何新的基于FPGA加速平台的开发,包括FPGA硬件设计、英特尔至强可扩展处理器就绪的软件堆栈以及应用工作负载等,都会遇到一个核心挑战——那就是如何分配从零开发和代码重用或IP授权之间的比例。

对于开发者来说,最高效的开发方式可能就是“不要让我弄明白它是什么,只是给我一种方法去实现我想做的事”。要让FPGA应用更广泛,就要让用户“忽略”他们用的是FPGA。就以数据中心为例,FPGA进入的最主要障碍也许并不是速度和成本,而是I/O设备软件和驱动程序的可用性。当硬件升级达到某种程度时,最关键是让它更易用,从而进一步打开用户生态。

英特尔OFS为Linux内核将提供定制化的软硬件基础设施,解决了软硬件及应用开发人员面临的许多痛点,包括开发FPGA设计(“拿来与定制”)所需的模块化、可组合代码,以及开源上游代码,从而让开源分销商能够为第三方和专有英特尔OFS平台提供本地支持。那么,英特尔OFS为硬件、应用和软件开发人员带来的价值分别是什么?简而言之,分别是定制化、在整个英特尔FPGA平台便利的移植性以及主要操作系统厂商分销的本地支持。

在易用性的探索上,曾经的Altera、现在的英特尔,以及对手Xilinx始终在努力。Xilinx在去年推出Vitis统一软件平台,据称该平台历经五年、投入总计 1000 个人工年而打造,目的在于让用户无需深入掌握硬件专业知识,就可以根据软件或算法代码自动适配和使用其硬件架构。不限制使用专有开发环境,而是可以插入到通用的软件开发工具中,并利用丰富的优化过的开源库,使开发者能够专注于算法的开发。

另一方面,从硬件的商用逻辑来看,传统硬件利润率增长越来越乏力,不论是电子元器件,还是更大的电子系统。就连特斯拉仅依靠汽车销售也无法实现持续盈利,这也是它为什么要用软件定义汽车,转向自动驾驶+娱乐服务这样的软服务去实现高利润。而靠软件赚钱的前提,就是要有庞大的用户基础。把FPGA放到英特尔包括CPU、GPU、FPGA等整个XPU架构的体系中去看,就不难理解这步棋的用意。

英特尔数据平台事业部副总裁兼FPGA 和电源产品事业部总经理 Patrick Dorsey表示,过去 FPGA 仅面向使用 RTL 或硬件语言进行开发的技术人员,现在取得了长足的进步。他提到了对于英特尔oneAPI的支持,oneAPI旨在提供统一的编程模型,简化 CPU、GPU 和 FPGA 的跨架构开发工作,可帮助软件开发人员和硬件开发人员简化开发工作,oneAPI 基于开放的规范和标准,以鼓励不同厂商采用统一编程模型,同时在软件友好型环境中提高了易用性。

英特尔数据平台事业部副总裁兼FPGA 和电源产品事业部总经理 Patrick Dorsey

英特尔副总裁、可编程解决方案事业部总经理Dave Moore表示:“经过早期客户的验证,英特尔开放式FPGA开发堆栈能够大幅降低研发周期,同时提升代码和硬件设计的重用率,对于希望加速工作负载的客户和合作伙伴而言是理想之选。”

英特尔副总裁、可编程解决方案事业部总经理Dave Moore

三管齐下的“定制逻辑连续体”优势

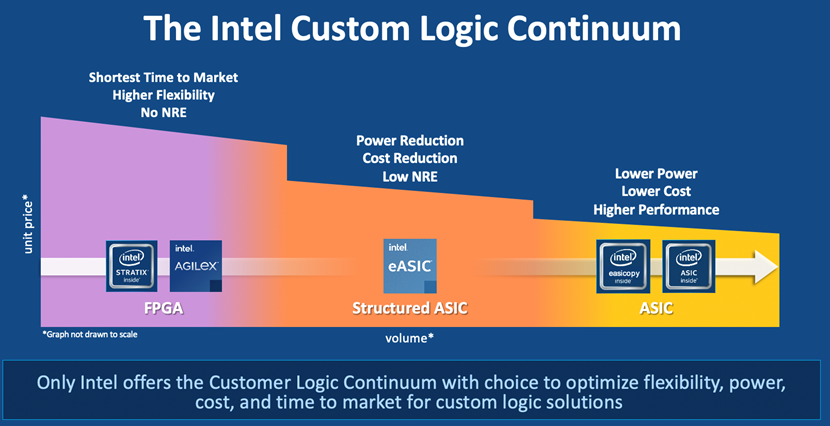

在FPGA技术大会上抢了FPGA风头的正是最新发布的eASIC N5X,这是英特尔于2018年收购eASIC后推出的首款结构化eASIC产品,搭载了与英特尔 FPGA兼容的硬件处理器系统。通过FPGA中的嵌入式硬件处理器帮助用户将定制逻辑与设计迁移到结构化ASIC中,带来了更低的单位成本,更快的性能和更低的功耗等好处,与FPGA相比最高可降低50%的核心能耗和成本,可用于加速5G、人工智能、云端与边缘工作负载的应用性能。

这款产品的推出,使英特尔成为市场上唯一一家实现了完整的定制逻辑连续体的半导体公司,涵盖FPGA、结构化ASIC以及ASIC。这也意味着,英特尔能够通过三管齐下的方法,支持在整个产品生命周期内重复进行灵活的优化:FPGA可为用户设计提供更佳的产品上市优势和更高的灵活性;ASIC能以更低的功耗和成本实现优异的硬件优化型性能;结构化eASIC则可以有效平衡产品上市优势与性能、成本之间的关系。

Patrick Dorsey介绍,以上每个选项都可以利用一组通用 IP,开发人员可以从这三种功能中任选其一作为开端,然后根据需求变化可以随时迁移至其他选项,在整个产品生命周期内都可以进行迁移。

“任性”的任意异构集成

有了FPGA、eASIC,别忘了英特尔还有tile或chiplet方面的技术,可以将多种制程技术、功能,甚至供应商产品集成到一种封装或一台设备中。

Patrick Dorsey表示,借助创新异构架构,可以充分利用各种 FPGA chiplet 库,这些库中包含专门用于处理、存储和传输数据的 FPGA chiplet,还有定制和专业 chiplet,有助于快速开发和推出 FPGA 芯片。这一特色被英特尔称为“任意异构集成”,也就是任何增值功能都可以集成到 FPGA 中,包括用户的定制 ASIC。

据了解,英特尔目前已经启动了若干个将用户的ASIC 集成到 FPGA 的计划。

首先推出了基于 Stratix 10 FPGA 系列的异构架构。通过chiplet 策略,英特尔对 DDR 内存、收发器速度和协议功能、高带宽内存、PCIe、UPI、DSP 甚至是 AI 张量块进行了不同组合,推出了六种定制型 Stratix 10 器件。其中的一个 Stratix 10 NX产品家族。NX 器件采用异构技术,可提供 AI 优化的计算能力。此外,还采用了封装内高带宽内存和 58GBPS 收发器,可提供英特尔首款 AI 优化的FPGA,以支持高带宽低延迟 AI 加速应用。英特尔已经开始批量交付 Stratix 10 NX,可帮助客户加速语音识别、安全和实时视频分析等应用。

利用 FPGA chiplet 策略的第二代产品家族是Agilex 系列 FPGA。相比 Stratix 10,Agilex 采用英特尔10nm SuperFin 技术和改进的 FPGA Hyperflex 架构,其性能提升40%,功耗降低40%。Agilex 还实现了收发器创新,数据速率是前代产品的两倍。

英特尔FPGA当前三大重点:

5G、SmartNIC、边缘优化

英特尔数据平台事业部网络和可配置逻辑部门高级总监张嘉君博士表示,随着电信行业向 5G 过渡,英特尔将网络基础设施视为最重要的机遇,2023 年它将为芯片市场贡献 250 亿美元的产值,而FPGA 网络芯片约占 250 亿美元 TAM 的 10%。

她表示,在以数据为中心的 5G 时代,可编程技术将在核心、RAN 和边缘网络中发挥关键作用。由于 5G 标准仍在演进,预计 FPGA 将继续发挥其可编程优势,用作 ASIC sidecar,以捕捉新特性。由于不同的垂直市场中出现了更多的用例, FPGA 作为 sidecar将在 5G 时代变得愈发重要。

涉及前沿市场的应用,Dave Moore谈到,在过去的垂直市场转型中,FPGA 的主要作用是扩展平台功能。FPGA 是一个“白板”,支持需要定制的苛刻应用,正如当前在云端 SmartNIC的 实施一样。通信服务提供商正在进行大规模网络改造,FPGA凭借可编程性,系统可以随着需求和标准的变化快速调整,5G 部署的早期阶段以及 Open RAN 实施的初步规划就是如此。借助 FPGA SmartNIC 平台,用户可以根据未来业务增长情况进行调整,保护已有硬件投资。

此外,英特尔还将持续提供边缘优化型 FPGA。其中包括 MAX、Cyclone 和 Arria FPGA。有些应用需要采用下一代技术,而有些应用更加注重成本,需要采用稳定的平台和工具。英特尔会继续提供边缘优化型 FPGA,并致力于为此类 FPGA 提供较长的产品生命周期。在无线或军事雷达等应用领域,此类 FPGA 可用作高端控制器、ASIC/ASSP 替代产品、高带宽低延迟数据路径引擎,或大规模并行处理。

写在最后

守旧与创新之间,英特尔当前找到了一个平衡点:一方面充分发挥既有优势,包括架构、制程、软件等,使之充分组合、产生裂变;另一方面,在需要补足的环节正在快速奔跑,比如最新的开放式FPGA开发堆栈。

端出了一个全家桶的英特尔,有着前所未有的人无我有的信心。这都是朕打下的江山。

- THE END -

🍁

往期精选

【免费】FPGA工程师招聘平台

资料汇总更新|软件安装包、书籍、源码、技术文档、手册……

基于FPGA的CRC校验码生成器设计

干货 | 拆解FPGA芯片,带你深入了解其原理

笔记连载 | Day4 Xilinx ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念篇

资料下载 | Vitis文档电子版

开课通知 | 2021FPGA寒假班来啦!

这篇关于FPGA受冷落?英特尔端出了这个全家桶的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!