本文主要是介绍嵌入式FPGA IP正在发现更广阔的用武之地,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

作者:郭道正, Achronix Semiconductor中国区总经理

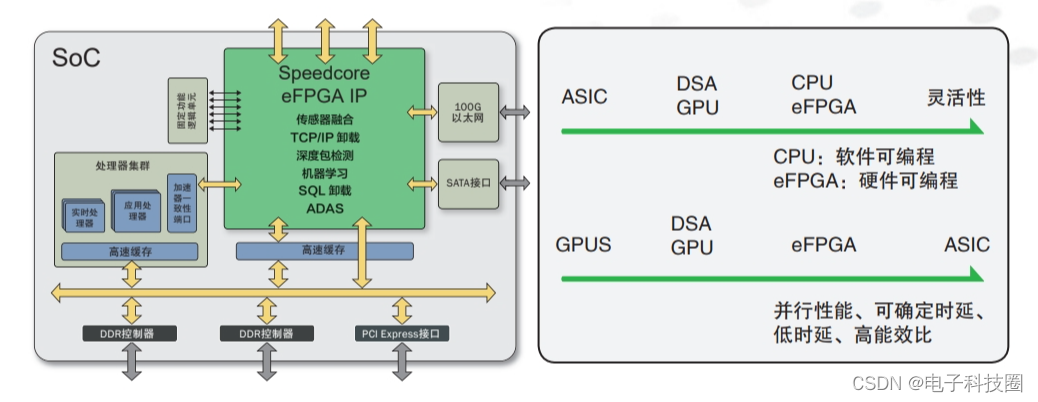

在日前落幕的“中国集成电路设计业2023年会暨广州集成电路产业创新发展高峰论坛(ICCAD 2023)”上,Achronix的Speedcore™嵌入式FPGA硅知识产权(eFPGA IP)受到了广泛关注,预约会议、专程前往或者驻足询问的芯片设计业人士的数量超过了往届,表明了越来越多的国内开发者正在考虑为其ASIC或SoC设计添加高性能eFPGA逻辑阵列。

众多潜在用户的需求,反映了当前各行各业都在加速导入智能化技术,并利用eFPGA来在其ASIC或SoC中添加硬件数据处理加速功能,并为不断演进的算法或者标准保留可编程性。Speedcore eFPGA IP包括了查找表、存储器、数字信号处理器(DSP)和机器学习处理器(MLP)等构建模块。它们都采用了模组化的结构设计,以支持客户根据其客制化终端系统的需求,来量身定制相应的资源组合。

Achronix的Speedcore IP以GDSII格式提供,同时提供相应的文档,以支持设计师将Speedcore eFPGA实例集成到其特有的ASIC之中。Achronix还提供配套的ACE设计工具,用于编译针对Speedcore eFPGA的设计。目前,Speedcore eFPGA IP已被全球数十家领先的科技企业采用,总的出货量超过了1500万。

简要功能介绍

由于Speedcore eFPGA是一款嵌入式IP,因此它被设计为整个ASIC的一个单元组件,被ASIC的其他完全定制的单元模组所包围(见下图)。Speedcore eFPGA包括以下功能:

·可编程内核逻辑阵列,具有客户自定义的功能

·内核I/O环

·FPGA配置单元(FCU)

·配置存储器(CMEM)

·用于调试和编程的接口

·用于测试的接口(DFT)

核心资源介绍

通过选择下列每种资源的数量,就可以定义一个定制Speedcore eFPGA IP的功能:

·逻辑 - 6输入查找表(LUT),加上集成的快速加法器

·逻辑RAM - 两种选择:

·用于LRAM2k的每个存储器单元的容量最多可达2Kb,其中包括与MLP紧耦合的存储器

·用于LRAM4k的每个存储器单元的容量最多可达4Kb

·Block RAM - 两种选择:

·用于BRAM20k的每个存储器单元的容量最多可达20Kb

·用于BRAM72k的每个存储器单元的容量最多可达72Kb,包括与MLP紧耦合的存储器

·DSP64 - 每个单元模块有一个18 x 27乘法器、64位累加器和27位预加法器

·MLP - 机器学习处理器(MLP)模块,包含乘法器、加法器、累加器和紧耦合存储器(包括BRAM72k和LRAM2k)

交付与应用价值

由于Achronix采用了根据客户需求来定制GDSII的商业模式,每个Speedcore eFPGA实例的资源模块的数量和组合都是基于客户需求来搭配提供。Achronix的Speedcore eFPGA IP可用于台积电(TSMC)的16FF+、16FFC、12FFC、7nm、5nm和3nm工艺技术节点,也可以移植到其他工艺节点上。

在ASIC或者SoC中嵌入Speedcore eFPGA将带来诸多好处,与一款独立的FPGA芯片相比,Speedcore eFPGA IP提供了以下优点:

·降低功耗多达75%

·节省90%的成本

·延迟缩短到1/100,同时带宽提高了10倍。

因此,Speedcore eFPGA具有极高的应用价值。

开发与编程

Achronix是唯一一家可以同时大批量生产并交付eFPGA IP和独立FPGA芯片的公司,而且它们都采用同一套ACE开发工具来支持。设计人员可以100%确信Speedcore eFPGA IP将会正常工作,因为它在Achronix的Speedster系列独立FPGA 芯片中已得到了全面的验证,并且经过了大量的流片验证。

由于Speedcore eFPGA IP采用的是与Achronix的独立FPGA芯片和搭载Achronix Speedster7t FPGA芯片的VectorPath加速卡相同的工具,开发人员可以先在这些独立FPGA芯片或者加速卡上完成设计,然后再移植到Speedcore eFPGA上。客户可以选择以下所列配置接口中的一项或多项组合来进行编程:

·JTAG

·并行CPU(x1、x8、x16、x32、x128数据宽度模式)

·串行闪存(1个或4个闪存器件)

·128位AXI总线

总结与展望

Achronix的Speedcore eFPGA IP保持了高端FPGA的性能,最高运行频率可达750MHz,典型的运行频率也可以达到300MHz-500MHz,可以为ASIC或者SoC提供高性能硬件加速,是诸多智能化应用和边缘计算的理想选择,因而被领先科技企业选择用于通信基础设备、网络加速、智能驾驶和金融科技等多种应用中。

从我们在ICCAD 2023上与客户的交流来看,一些领先的国内系统公司和芯片设计企业已经认识到eFPGA的优点与价值,并进一步在探讨与Achronix进行基于eFPGA的chiplet等新的合作模式。因此,我们可以展望在未来几年中,集成了Speedcore等eFPGA的ASIC或者SoC将是智能化和高速网联等领域内芯片设计企业的一条重要的创新之道。联系本文作者,请发送邮件到:dawson.guo@achronix.com

这篇关于嵌入式FPGA IP正在发现更广阔的用武之地的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!