本文主要是介绍NES(FC) FPGA游戏卡开发笔记(6)---- 再整理下思路和具体工作(包括N8 Pro mapper部分的FPGA代码简单分析),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

开发方案的考虑

1)N8是CPLD+FPGA,N8 Pro是两个FPGA(其实也是类似CPLD+FPGA)。ICE40芯片的配置文件也是固化在芯片内的。N8的CPLD的任务是扩展SPI接口可以访问SDIO卡,另外可以向mapper FPGA下载mapper文件进行配置操作。而N8 Pro的这些功能可以让STM32 CPU完成,N8 Pro强化了其他功能,比如cheat,在游戏内调出菜单做即时保存,这些是ICE40去完成的?

另外用CPLD可以增加盗版的难度。

2)如果只需要游戏加载,退出游戏保存文档到sdio卡和从sdio卡加载文档功能的话,感觉可以用MCU+FPGA的方案就可以实现,所以优先可以做这种的,如果有问题再做考虑。游戏玩家的主要需求是大容量rom也可以玩,更多的mapper支持。

N8 pro mapper功能的FPGA源代码

GitHub - krikzz/EDN8-PRO: EverDrive N8 PRO dev sources

上面的链接是N8的开发者开源的FPGA代码。Cyclone IV上的SystemVerilog源代码,非常完整的mapper实现,有可能删除了和ICE40的逻辑部分(没深入看代码)。

作者的开源的做法非常符合一个NES社区的共享的精神,毕竟这些NES rom的扒板,MMC芯片的功能分析,mapper号的整理都是有NES hack社区完成的。CPLD和MCU的代码没有开源,毕竟这一块是作者的版权,与NES社区关系不大。

文件列表

下载代码之后,在mapper/top目录下有个top.qdf文件,是Quartus的项目文件。用QuartusII软件打开。

top.sv的顶层module,可以看到所用到的CyClone IV FPGA芯片的所有输入输出管脚资源。另外提一下里面定义了moudle dac_ds(完成某些MMC芯片的sound功能?好像不是很全,没具体分析了)。

map_255.sv,这个专门是为NESOS.nes(作者开发的游戏菜单,相当于一个nes游戏,在游戏机上电之后的菜单),通过这个菜单选择加载游戏。(注:之前的笔记提到过用模拟器加载nesos.nes文件的时候说不支持255,毕竟这个是开发者自己用的私有mapper,但为什么NES头格式是mapper 15呢?)

map_xxx.sv,这个xxx是数字,就是某个mapper号。比如map_000.sv,实现了mapper 0的游戏mmc功能,但并不仅仅包括mapper 0,还包括好几种mapper号。作者的设计思路是把所有mapper号进行分组,分成多组,每个map_xxx.sv实现一组的mapper功能。这样的话一次加载配置相当于支持了多个mapper号。如果玩家第一个加载的游戏mapper号属于mapper 0,则加载map_000.sv(对应最终编译的rbf文件)。如果要换个游戏,如果下个游戏的mapper号也是数学map_000.sv支持的,则不用加载新的rbf文件了,只要加载游戏rom就可以了。除非下一个游戏是属性非map_000支持的。mapper分组的好处是充分利用FPGA的资源,毕竟CyClone提供了6000多大逻辑单元,当然理想的情况是一次全部加载。

map_hub.sv,连接所有的map_xxx.sv通信接口。相当于一个hub功能。

eep24x.sv,

先推荐一个网站:NesCartDB - Search(游戏卡数据库),提供了详细的游戏卡信息。

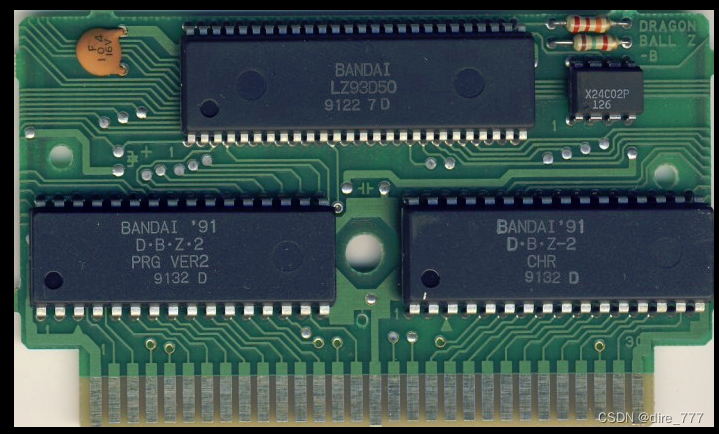

下图就是龙珠ZII激神弗利沙的游戏卡信息

LZ93D50是MMC芯片(万代出的),X24C02P是一块EEPROM芯片。eep24x.sv就是实现了这块芯片的功能。这个游戏是mapper 16,在FPGA完成mapper 16功能的时候需要mmc和eeprom的实现。

dma.sv,完成数据从MCU的SPI接口通过DMA方式再下载到SRAM。

closks.sdc,FPGA的时钟约束文件,spi是50MHz时钟,cpu m2是2MHz时钟。

资源

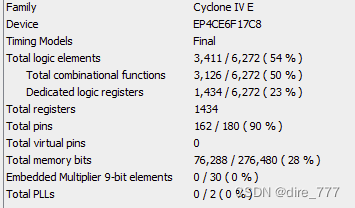

上图是通过QuartusII编译之后的资源使用情况,162个pin,3411个逻辑单元,不到8k的ram资源。

在项目编译之后,还可以查看RTL view。看代码比较抽象,看RTL视图这样就不那么抽象了。

IO管脚使用的非常多。这可以作为FPGA选用,方案实现的参考。选择FPGA的逻辑单元肯定没有问题。但具体淘宝上的开发板的IO数目可能不能满足要求了。

设计思路,问题,下一步的学习和开发的工作

通过分析代码,分析mmc的工作机制对设计的框架大致有点数了。下一步就可以在实现上需要完成哪些事,有哪些问题还需要厘清。

1)CPU如果执行游戏,或者说CPU指针指向第一条指令开始运行。

游戏卡插入游戏机卡槽,游戏机上电,CPU如何运行第一个游戏菜单游戏(假设游戏菜单已经在RAM中了)?这里需要学习一下6052的体系结构,或者NES的启动操作步骤(找些书看看其中的部分就可以了。

2)游戏卡上电之后具体操作是什么?

MCU上电,固件运行,加载SDIO驱动,fatfs文件系统,USB驱动(这个可以暂不考虑)。从sd卡读取游戏菜单nes文件,下载到SRAM,配置FPGA,使能mapper功能(这个是游戏菜单的mapper)。让CPU可以运行游戏菜单。

需要考虑的问题:

1)这些操作需要多少时间?菜单游戏加载从上电到完成需要多少时间,游戏机启动到开始运行大概需要多少时间?

2)是先配置FPGA,还是先下载游戏菜单?这个选择影响各个芯片直接的线的连接和管脚IO资源的使用。

3)如何下载到SRAM,

是利用MCU的XMC(类似于STM32的FSMC)执行访问SRAM。

比如配置好FPGA之后,MCU的数据和地址,控制总线连接到FPGA,通过FPGA再连接到SRAM(利用MCU的XMC外接SRAM功能)。或者MCU通过SPI连接FPGA,在通过FPGA的传输模块(DMA)下载到SRAM。

4)在游戏菜单运行之后,玩家选择某个游戏,游戏菜单收到一个操作指令之后,需要控制MCU加载游戏到SRAM,同时加载对应的mapper文件到FPGA(思考:是不是可以把mapper255做到其他mapper的rbf文件中呢?)。这个功能的实现可以参考多合1卡游戏的具体实现。毕竟多合1卡也是菜单加游戏。

5)游戏机复位,玩家按复位按钮之后的FPGA的操作:

需要重新加载游戏菜单。从SD卡加载游戏菜单,mapper255的FPGA控制加载。(思考:可不可以不从SD卡加载,利用mapper255的mmc的功能,可以把游戏菜单软件拷到SRAM的高地址,然后用切换bank的方式进行加载?)

这里需要了解硬件复位之后的工作机制(需要阅读NES架构文档和编程文档)。

6)游戏存档到SDIO卡,在游戏菜单中选择保存到SDIO卡

一种是按复位就保存(如果上个游戏是有存档功能的),一种是在菜单用户手动控制存档。

7)游戏存档加载,玩家在加载某个游戏之后,自动从SDIO卡从加载游戏对应的文档。

如果SDIO卡中有多个该游戏的存档的时候,选择哪一个呢?是最新的?还是弹出菜单让用户选择?

下一步是学习一下6052,厘清启动,复位操作过程。关注启动时间。(游戏加载是否可以在启动时间内完成,如果完不成怎么办?)CPU是不是有能力知道游戏卡已经准备好了,可以运行了?

3)AD电路图设计软件使用

计划是一边做一遍学。

4)数字逻辑和Verilog编程学习

从N8Pro的FPGA源代码可以大致了解一下需要哪些功能需要,以及对数字逻辑的知识要求。

大部分MMC实现的逻辑控制比较简单,只需要基本的数据逻辑知识就可以了。而且还有实例,看代码就行。

DMA功能,寄存器实现,SPI数据接收逻辑实现,RAM,FIFO。这些模块功能都比较基础。难度都不大。

找一本verilog的编程书看看语法(另外找一本编程规范的书看看)。可以边看代码边学,看不懂就查书。可以写写代码分析文档。

其实整个设计(主要是FPGA部分)难度很低,大概是个本科生或者研究生的毕业设计或者作业,也没有创新的地方。逻辑部分的设计远远不如用FPGA实现一个usb2.0控制器的难度,只是需要时间,毕竟那么多mapper功能需要支持,只是工作量的问题。

30年前做个MMC控制器还有点难度,现在的工具和资源那么方便,clone一个这样的芯片太容易了。

这篇关于NES(FC) FPGA游戏卡开发笔记(6)---- 再整理下思路和具体工作(包括N8 Pro mapper部分的FPGA代码简单分析)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!