本文主要是介绍易灵思FIFO操作指南,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

易灵思FIFO操作指南

- 一.软件设置界面

- 二.FIFO端口定义

- 三.FIFO时序

- 小结

一.软件设置界面

打开任意工程,在IPM菜单栏里面,双击FIFO IP ;

生成IP ,需要在module name 处 命名,

在配置界面根据需要,使能某些指示信号;

右下角点击generate生成。

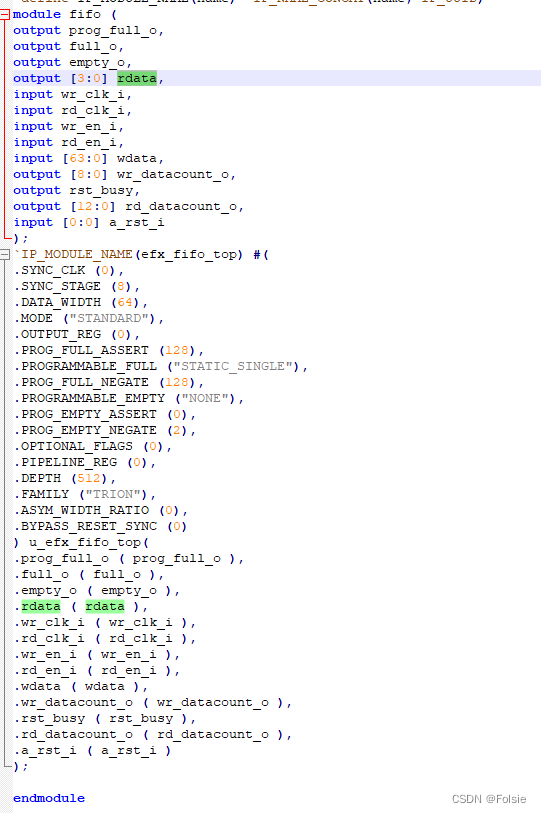

二.FIFO端口定义

| 时钟,复位端口定义 | Synchronous | Asynchronous |input?output|功能描述 |

|–|–|–|–|–|–|–|–|

| | | | |

| a_rst_i | √ | √ | input | 异步复位信号,初始化所有内部指针和输出标志。 |

| wr_clk_i | | √ | input | 写时钟 |

| rd_clk_i | | √ | input | 读时钟 |

| clk_i | √ | | input | 时钟(同步模式下,只有一个时钟) |

| wr_datacount_o [n-1:0] | | √ | output | 异步 FIFO 写入域数据计数 |

| rd_datacount_o [n-1:0] | | √ | output | 异步 FIFO 读取域数据计数 |

| datacount_o [n-1:0] |√ | | output | 同步 FIFO 数据计数

| | | | |

| | | | |

| | | | |

| 写数据端口定义 | | |

| wr_en_i | | | Input | 写数据使能

| wdata [m-1:0] | | | Input | 写数据

| full_o | | | output | 写满标志

| almost_full_o | | | output (可选) | 几乎写满

| prog_full_o | | | output(可选) | (可设置)几乎写满

| wr_ack_o | | | output(可选) | 写入确认。代表上一个写时钟的wr_en_i成功

| overflow_o | | | output (可选) | 溢出。代表上一个写时钟的wr_en_i被拒绝

| | | | |

| | | | |

| | | | |

| 读数据端口定义 | | |

| rd_en_i | | | Input | 读使能

| rdata [m-1:0] | | | output | 读数据

| rd_valid_o | | | output (可选) | 读数据取有效

| empty_o | | | output | 读空标志

| almost_empty_o | | | output (可选) | 几乎为空

| prog_empty_o| | | output(可选) | (可设置)几乎为空

|underflow_o | | | output(可选) | 代表上一个读时钟的rd_en_i被拒绝

三.FIFO时序

同步FIFO标准模式

同步FIFO FWFT模式

异步FIFO标准模式

异步FIFO FWFT模式

小结

1.在实际使用易灵思的FIFO时,为了避免版本更新产生的IP重加载和重配置 ,笔者一般都会将对应IP生成下的 .v 文件直接copy到工程目录下进行使用;

2.如FIFO模块 对应产品的.V文件中,如果要重新配置 ,将再次生成的 .v文件的这部分做替换就行 ;

这篇关于易灵思FIFO操作指南的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!