易灵思专题

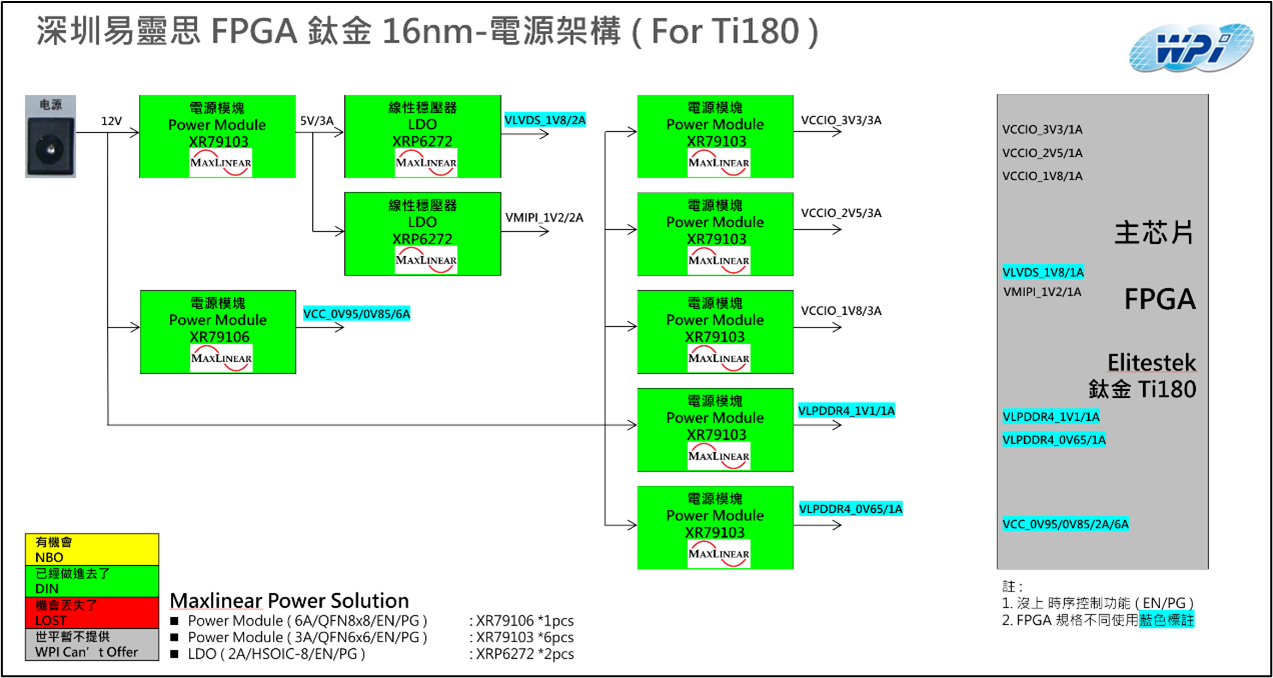

联合 Maxlinear 迈凌 与 Elitestek 易灵思 - WPI 世平推出基于 FPGA 芯片的好用高效电源解决方案

近期 WPI 世平公司联合 Maxlinear 迈凌电源产品搭配 Elitestek 易灵思 FPGA 共同合作推出基于 FPGA 芯片的好用高效电源解决方案。 Elitestek 易灵思 FPGA 核心产品有 2 大系列 : Trion 系列与钛金系列。Trion 系列主要特点是 : 1. 40nm 工艺 2. 超低功耗 ( 可低至竞争对手的 1/2 ) 3. 超小封装 (

【risc-v】易灵思efinix FPGA riscv嵌入式软件源码分享

系列文章目录 分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。 本系列会覆盖以下FPGA厂商 易灵思 efinix 赛灵思 xilinx 阿尔特拉 Altera 本文内容隶属于【易灵思efinix】系列。 【risc-v】易灵思efinix FPGA sapphire_soc IP配置参数分享-CSDN博客 【risc-v】易灵思efini

易灵思Inout管脚操作指南

易灵思Inout管脚操作指南 一.原理说明二.软件设置界面三.逻辑内的设置 一.原理说明 易灵思器件在设计时,逻辑层和硬件(硬核接口,管脚接口)层是分开独立的,无论是MIPI,,DDR,PLL 和 JTAG,对于用户来说,可以把硬件层当做外围器件来看待,只需要关注和逻辑层关联的接口的时序; LVDS 和 GPIO 一样,当然也都是同样的设计理念; 二.软件设置界面 1.

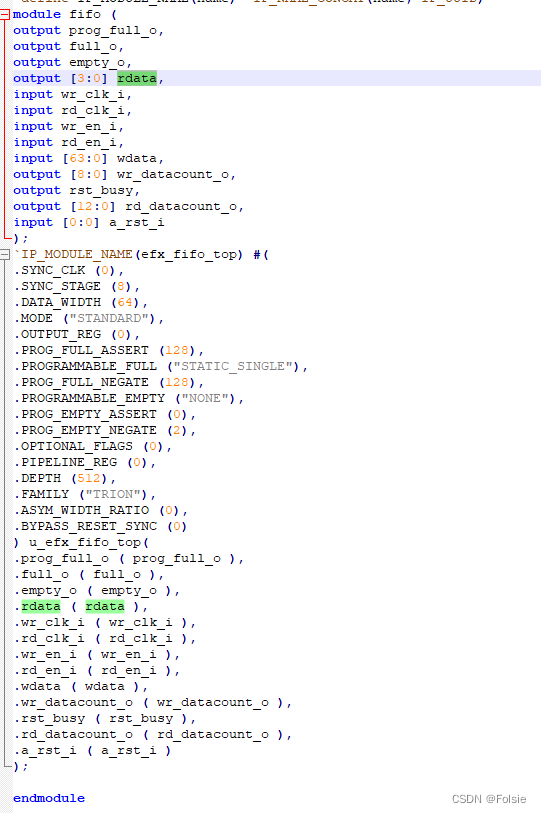

易灵思FIFO操作指南

易灵思FIFO操作指南 一.软件设置界面二.FIFO端口定义三.FIFO时序小结 一.软件设置界面 打开任意工程,在IPM菜单栏里面,双击FIFO IP ; 生成IP ,需要在module name 处 命名, 在配置界面根据需要,使能某些指示信号; 右下角点击generate生成。 二.FIFO端口定义 | 时钟,复位端口定义 | Synchronous | Async

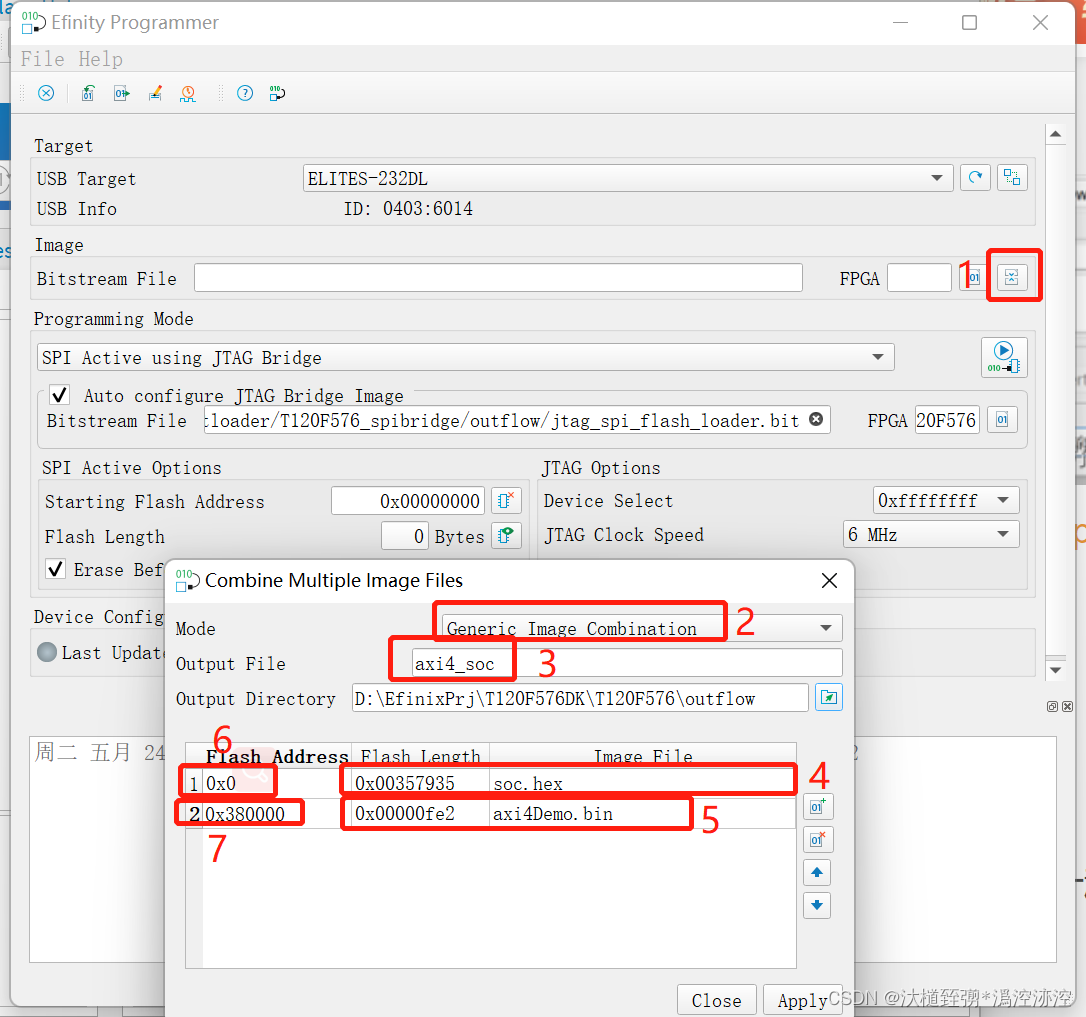

易灵思的Riscv-Sapphire软核搭建及开发流程

目录 一、首先生成Sapphire软核ip 二、创建Eclipse工程 三、配置Eclipse的编译环境 四、合并逻辑的hex和软核的bin的文件 一、首先生成Sapphire软核ip 通过软件Efinity的IP-Catalog功能生成Sapphire-riscv的IP核,我这里保持默认参数,如下图: 找到相应的目录,目录里的IP文件夹下会有生成的sapphire的目录