本文主要是介绍VIVADO 2014.4 如何编写mealy状态机并测试,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

VIVADO 2014.4 如何编写mealy状态机并测试

1. 题干描述:

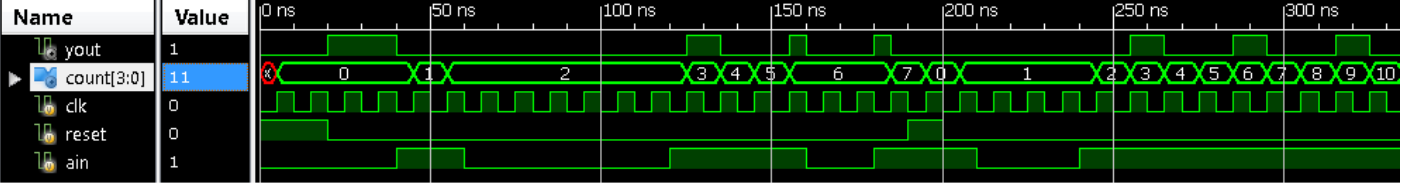

Design a sequence detector implementing a Mealy state machine using

three always blocks. The Mealy state machine has one input (ain) and

one output (yout). The output yout is 1 if and only if the total

number of 1s received is divisible by 3 (hint: 0 is inclusive,

however, reset cycle(s) do not count as 0- see in simulation waveform

time=200). Develop a testbench and verify the model through a

behavioral simulation.

即需要实现mealy状态机,该状态机有一个输入(0/1)和一个输出(0/1)。只有累计输入1的个数为3的倍数才会输出1(0个1也输出1)。

2. 理想的仿真波形图:

3.绘制mealy状态机

4.新建项目

请务必保持硬件配置(芯片选项:xc7a35tcpg236-1)正确,其他的选项按新建项目的默认选项来即可

最后一步的图:

5.新建约束文件

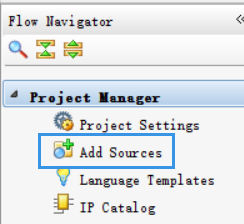

新建文件的地方(项目窗口的左侧):

在弹出来的窗口里选择:

然后在弹出来的地方选择新建一个约束文件:

自己取名字就行,然后把代码拷贝进去:

## Switches

set_property PACKAGE_PIN V17 [get_ports {ain}] set_property IOSTANDARD LVCMOS33 [get_ports {ain}]set_property PACKAGE_PIN R2 [get_ports {clk}] set_property IOSTANDARD LVCMOS33 [get_ports {clk}]## LEDs

set_property PACKAGE_PIN U16 [get_ports {yout}] set_property IOSTANDARD LVCMOS33 [get_ports {yout}]set_property PACKAGE_PIN W18 [get_ports {count[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {count[0]}]

set_property PACKAGE_PIN U15 [get_ports {count[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {count[1]}]

set_property PACKAGE_PIN U14 [get_ports {count[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {count[2]}]

set_property PACKAGE_PIN V14 [get_ports {count[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {count[3]}]##Buttons

set_property PACKAGE_PIN T18 [get_ports reset] set_property IOSTANDARD LVCMOS33 [get_ports reset]

6.编写设计文件

这一块才是mealy状态机逻辑实现的代码编写,我采用的是三个always版块实现,这也是mealy状态机的典型实现方式之一。

新建设计文件也在第五步的add resource那里,点击添加之后选择第二个选项“Add or create design sources”:

之后选择新建啦:

接下来自己取名字新建就行,注意文件类型是sv结尾的:

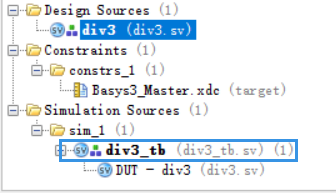

可以看到左侧上方的source板块有了自己新建的.sv文件和导入的约束文件。

点开.sv结尾的设计文件,比如我的:

继续复制我的代码hh,代码是根据mealy状态图写的哦:

`timescale 1ns / 1psmodule div3(output logic yout,

output logic[3:0] count,

input logic clk,

input reset,

input ain);typedef enum logic [1:0] { S0,S1,S2,S3} statetype;

statetype state, nextstate;always_ff@(posedge clk,posedge reset)

if (reset) begin state<=S0;count=0;

end

else begin state<=nextstate;if(ain)count<=count+1;

endalways@(state,ain,reset)case(state)S0: if(reset)yout=0;else if(!ain) yout=1;else yout=0;S1: yout=0;S2: yout=0;S3: if(ain) yout=1;else yout=0;endcasealways@(ain,state)case(state)S0: if(ain)nextstate=S1;else nextstate=S0;S1: if(ain)nextstate=S2;else nextstate=S1;S2: if(ain)nextstate=S3;else nextstate=S2;S3: if(ain)nextstate=S1;else nextstate=S3;endcaseendmodule

最后啦,加入仿真测试文件,这个也和前面一样"Add sources",之后选择:

接下来不多说了,也是create File… ,后续步骤都是默认的,没有需要修改的地方,然后就得到一个仿真文件:

和前面的一样,抄代码(大佬可自行编写,这一部分和mealy机无关的,会编写的人懂hh):

module div3_tb();logic yout;logic [3:0] count;logic clk, reset, ain;div3 DUT(yout,count,clk,reset,ain);// generate clockalways // no sensitivity list, so it always executesbeginclk = 0; #5; clk = 1; #5;endinitial beginain = 0;reset = 1;#20 reset = 0;#20 ain = 1;#20 ain = 0;#60 ain = 1;#40 ain = 0;#20 ain = 1;#10 reset = 1;#10 reset = 0;#10 ain = 0;#30 ain = 1;end

endmodule

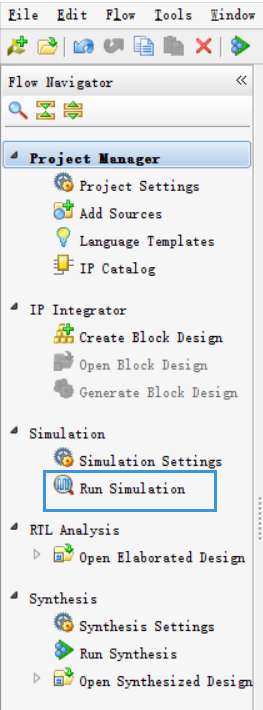

所有文件已经准备就绪,接下来就是运行仿真了,点最左侧竖条框的仿真运行:

鼠标单击之后,在弹出来的选择框里选第一个:Run behavioral simulation

稍等片刻可看到结果:

一切就好啦~

不出意外的话我还会写一篇moore状态机的例子~

这篇关于VIVADO 2014.4 如何编写mealy状态机并测试的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!