本文主要是介绍hnu 数字电路 实验2.3 4位行波加法器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

3.用VHDL语言设计一个4位行波加法器

① 理解要求,需要完成一个一一进位的四位行波加法器。初步计划:设计一个半加器->利用半加器完成全加器的设计->设计四位行波加法器。

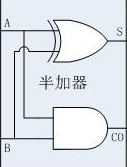

② 原理图:

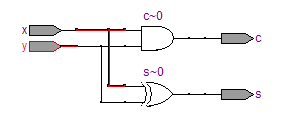

半加器:

全加器:

③ 打开QuartusII,新建工程,工程命名为adder_4,开始编写源代码。

④ 写好源代码,保存文件。

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity half_adder isport(x,y:in std_logic;s,c:out std_logic);

end half_adder;architecture dataflow_3 of half_adder isbegins <= x xor y;c <= x and y;

end dataflow_3;LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity full_adder isport(x,y,z:in std_logic;s,c:out std_logic);

end full_adder;architecture struc_dataflow_3 of full_adder iscomponent half_adderport(x,y:in std_logic;s,c:out std_logic);end component;signal hs,hc,tc:std_logic;beginHA1:half_adderport map(x,y,hs,hc);HA2:half_adderport map(hs,z,s,tc);c <= tc or hc;

end struc_dataflow_3;LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity adder_4 isport(B,A:in std_logic_vector(3 downto 0);C0:in std_logic;S:out std_logic_vector(3 downto 0);C4:out std_logic);

end adder_4;architecture structural_4 of adder_4 iscomponent full_adderport(x,y,z:in std_logic;s,c:out std_logic);end component;signal C:std_logic_vector(4 downto 0);beginBit0:full_adderport map(B(0),A(0),C(0),S(0),C(1));Bit1:full_adderport map(B(1),A(1),C(1),S(1),C(2));Bit2:full_adderport map(B(2),A(2),C(2),S(2),C(3));Bit3:full_adderport map(B(3),A(3),C(3),S(3),C(4));C(0) <= C0;C4 <= C(4);

end structural_4;

(如图为源代码)

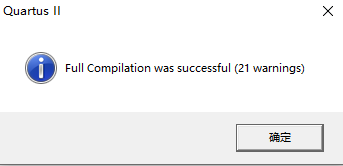

⑤ 编译与调试。确保顶层实现的命名和工程名一致。编译成功。

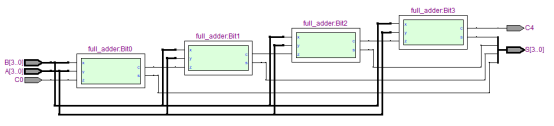

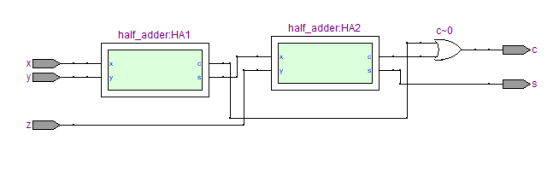

⑥ 查看RTL视图。

四位全加器:

全加器:

半加器:

⑦ 结果分析及结论。

如RTL图所示,该4位全加器分层构建而成,每一层的RTL视图和原理图相符。

⑧ 功能仿真的波形及验证。

a.新建波形文件,将对应的16种输入存储在波形文件adder_4.vwf中。

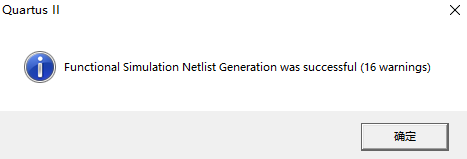

b.生成网表。

c.进行功能仿真。

波形图如下图:

d.结果分析及结论

⑨ 实现时序仿真。

a.仿真成功。

b.时序仿真波形图如下:

c.结果分析及结论(为方便说明以及观测,A,B,S向量表示的二进制数用在分析过程中统一用十进制数表示)

d.编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

从B1到S3耗时最长,为10.410ns,从C0到S0耗时最短,为8.141ns,可结果由耗时最长的那个决定,故整体耗时为10.410ns。

这篇关于hnu 数字电路 实验2.3 4位行波加法器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!