本文主要是介绍【Xilinx Kintex-7 Virtex-7 LVDS bank电压】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

各种介绍很多,也都写的似乎很长很详细,但有错误。

详细的查阅Xilinx 论坛 43989

核心

总结一下就是Xilinx 7serious 的FPGA ,你如果要配置成LVDS,这的LVDS是正儿八经的那种,那么FPGA 这块你只需要记住两点就可以。

第一,假如你用的是HR bank,就是宽压的,或者说可以单端到3.3V的,那么就要配置成LVDS_25;对应的VCCO也需要是2.5V;

第二,假如要用的是HP bank,高性能的,那么直接LVDS;VCCO 给到1.8V;

总结以上这两种都是直接对接标准的LVDS的。

1、HR和HP banks基本介绍

Xilinx的7系列FPGA有两种IO Bank:HP(High Performace)和HR(High Range)。

HP(high-performance)I/O banks的设计目的是为了获取更高的Memory及chip-to-chip间的传输速率;

HR(high-range)I/O banks的设计目的是为了更宽的I/O电平标准。

两种BANK的IO口电压不同,其中HR I/O Banks的VCCO电压最大为3.3V,HP I/O banks的VCCO电压最大为1.8V。

特别是初次使用7系列时,在硬件设计中特别要注意它们I/O口的最大工作电压,一不注意就会把电压搞错,导致FPGA不能正常工作。

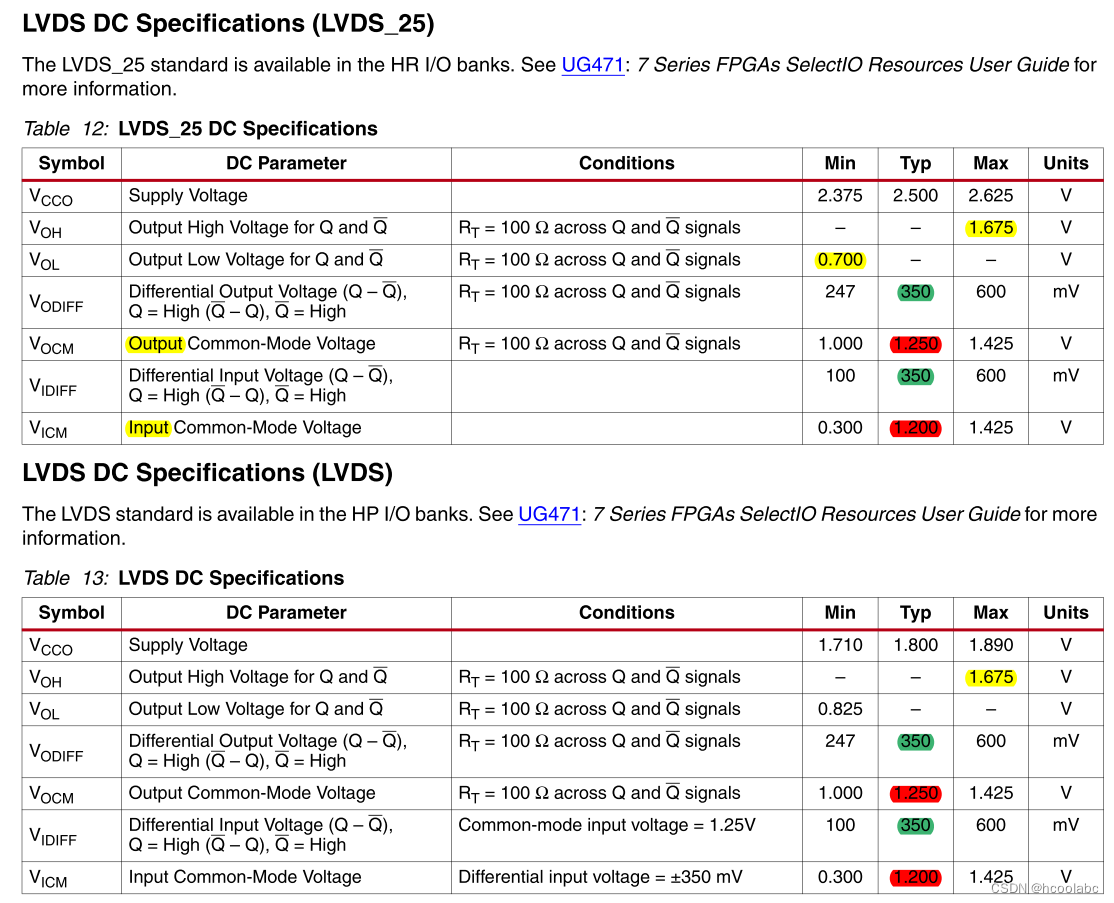

2、HR和HP banks的LVDS电平

当两个banks的I/O口作为LVDS电平时,HR banks的I/O电压VCCO只能为2.5V,HP banks的I/O口电压为1.8V。

{两个banks支持LVDS的标准不同,HR I/O banks的I/O只能分配LVDS_25标准,HP分配为LVDS标准}。

这说的不对,都是对外支持标准的LVDS,可以认为Xilinx在设计HR bank 时,多了某种驱动,或者认为0.7V左右的压降,类似PN结一类的东西;后文细说猜想原因)

查阅DS182 手册,LVDS_25和LVDS的电气特性是一致且与标准LVDS相同。

黄色是对参考地电压高电平不超过1.675V,低电平不低于0.7V;

绿色表示差分对的摆幅,或者说二者差值的绝对值,典型值为350mV;

红色表示输出输入的共模电压;

高速AD/DA的LVDS工作电压一般为1.8V,一些硬件工程师可能担心:HR bank的工作电压为2.5V,但是HR bank的LVDS却不是2.5V,可以直接工作电压为1.8V的外设。

3、HR banks电压接错LVDS还能使用吗

当1.8V工作电压AD/DA的LVDS接口连接到FPGA时,设计人员把FPGA HR banks的I/O口电压VCCO直接设计跟AD/DA I/O一样的电压为1.8V,这时也勉强可以工作。HR I/O电压设计为1.8V,同样可以作为LVDS使用。I/O电压主要影响LVDS的阻抗匹配。那么电压不对就无法保证LVDS速率达到理论速率。

但如果给到3.3V,那只能接收,不能发送了。

某些较旧的 FPGA 系列中提供的“LVDS_33”I/O 标准在 7 系列、UltraScale 或 UltraScale+ 器件中不受支持。

无论是高范围 (HR) bank、高密度 (HD) bank 还是高性能 (HP) bank,其 VCCO 引脚都不能以 3.3V 供电(如果使用 LVDS 输出)。

7 系列、UltraScale 和 UltraScale+ I/O bank 可能支持较旧系列的LVDS_33输出,但必须注意确保:

未违反数据表1和表2中的Vin值。

不违反 LVDS(HP 组)或 LVDS_25(HR 或 HD 组)的 VIDIFF 和 VICM。

可能需要使用IBIS模型运行信号完整性仿真,以确保不违反这两项。

即使VCCO电平不是1.8V,在HP I/O bank中具有LVDS输入也是可以接受的。LVDS 输出(因此是双向 LVDS)只能在 1.8V 供电的组中使用。

同样,即使VCCO电平不是2.5V,在HR或HD I/O bank中具有LVDS_25输入也是可以接受的。LVDS_25输出(以及双向LVDS_25)只能在以 2.5V 供电的组中使用。

但是,必须满足以下条件:

DIFF_TERM属性必须为 FALSE - 您需要使用外部差分终端电阻器。

确保驱动器件的 VOD 和 VOCM 电平在 7 系列、UltraScale 或 UltraScale+ 接收器的 VIDIFF 和 VICM 范围内,并且不违反数据手册表 1 和表 2 中的 VIN。

表 1-55:7 系列 FPGA 中的“每个受支持的 I/O 标准的 VCCO 和 VREF 要求” SelectIO 资源用户指南 (UG471) 概述了所有支持的 I/O 标准的 VCCO 和 VREF 电压轨要求,输入和输出列不同(双向引脚需要同时遵守两者)。

表 1-77:UltraScale 架构 SelectIO 资源用户指南 (UG571) 中的“每个受支持的 I/O 标准的 VCCO 和 VREF 要求”概述了所有支持的 I/O 标准的 VCCO 和 VREF 电压轨要求,输入和输出列不同(双向引脚需要同时遵守两者)。

这篇关于【Xilinx Kintex-7 Virtex-7 LVDS bank电压】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-30 RS485串口程序收发环路设计](https://i-blog.csdnimg.cn/direct/320b5c48ecbf46a2b876f556cbe213e5.png)