本文主要是介绍FPGA设计FIR滤波器低通滤波器,代码及视频,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

名称:FIR滤波器低通滤波器

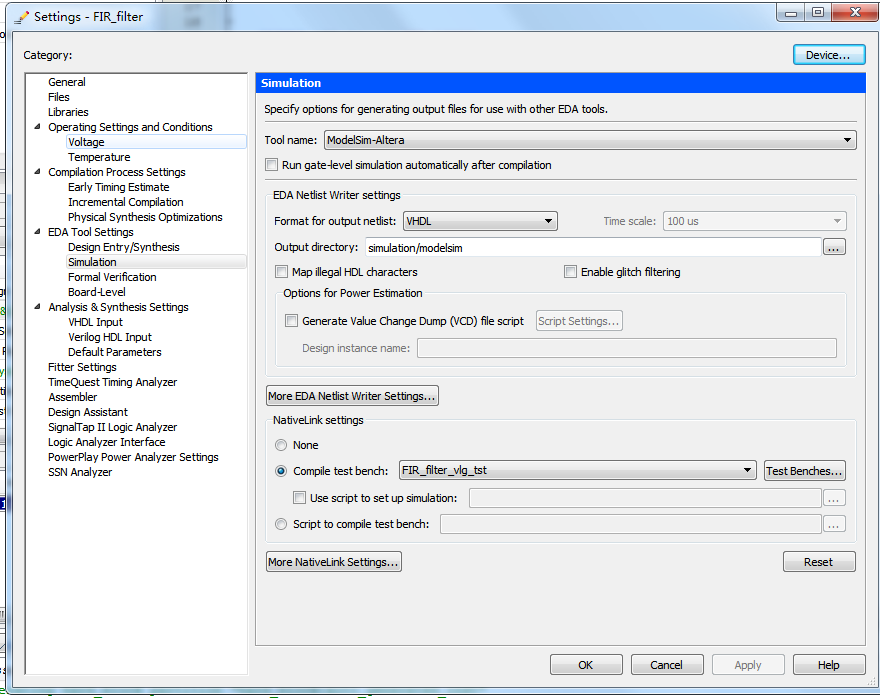

软件:Quartus

语言:Verilog/VHDL

本资源含有verilog及VHDL两种语言设计的工程,每个工程均可实现以下FIR滤波器的功能。

代码功能:

设计一个8阶FIR滤波器(低通滤波器),要求截止频率为20KHz,使用线性相位结构。

参数设计方法:

使用matlab软件设计滤波器系数

滤波器系数设计:

打开Matlab软件在指令窗口中键入:m=fir1(7,0.2),即可得到如下的系数:

0.009、0.048、0.164、0.279、0.279、0.164、0.048、0.009

将系数放大1000倍即:9,48,164,279;乘加计算计算完成后再除以1000.

演示视频(以VHDL工程文件为例,verilog同理):

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=212

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

FIR滤波器低通滤波器(代码在文末付费下载)软件:Quartus语言:Verilog/VHDL本资源含有verilog及VHDL两种语言设计的工程,每个工程均可实现以下FIR滤波器的功能。代码功能:设计一个8阶FIR滤波器(低通滤波器),要求截止频率为20KHz,使用线性相位结构。参数设计方法:使用matlab软件设计滤波器系数滤波器系数设计:打开Matlab软件在指令窗口中键入:m=fir名称:FIR滤波器低通滤波器(代码在文末付费下载)软件:Quartus语言:Verilog/VHDL本资源含有verilog及VHDL两种语言设计的工程,每个工程均可实现以下FIR滤波器的功能。代码功能:设计一个8阶FIR滤波器(低通滤波器),要求截止频率为20KHz,使用线性相位结构。参数设计方法:使用matlab软件设计滤波器系数滤波器系数设计:打开Matlab软件在指令窗口中键入:m=fir![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=212

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=212

部分代码展示

verilog代码:

//滤波器 module FIR_filter( input clk_in,//50MHz input reset_p,//高电平复位 output [9:0]fir_data//滤波后结果 ); wire [9:0] data_in; wire clk_100K; //分频模块,50M分频到100K div_clk i_div_clk( . clk_in(clk_in), . clk_out(clk_100K) ); //产生带噪声的正弦波 sin_noise i_sin_noise( . clk_in(clk_in),//50MHz . reset_p(reset_p),//高电平复位 . sin_and_noise(data_in)//产生带噪声的正弦波 ); //8阶线性相位结构FIR FIR i_FIR( . clk(clk_100K),//100K . reset_p(reset_p),//高电平复位 . data_in(data_in),//周期1K,噪声频率30K左右 . fir_data(fir_data)//滤波后结果 ); endmodule

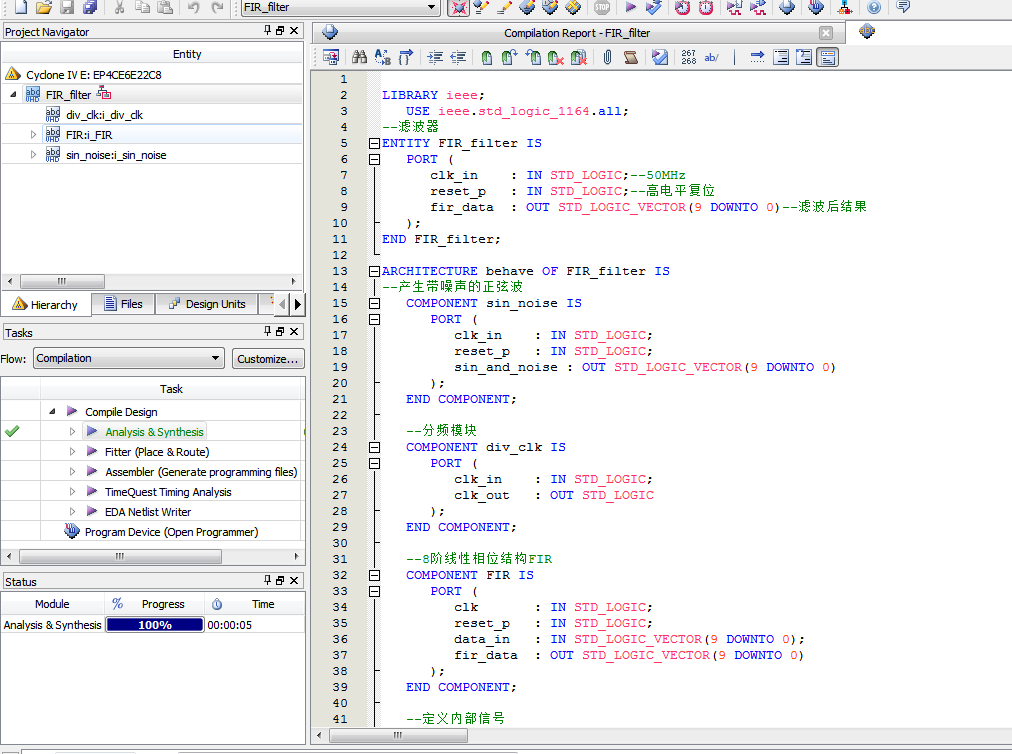

VHDL代码:

LIBRARY ieee;USE ieee.std_logic_1164.all; --滤波器 ENTITY FIR_filter ISPORT (clk_in : IN STD_LOGIC;--50MHzreset_p : IN STD_LOGIC;--高电平复位fir_data : OUT STD_LOGIC_VECTOR(9 DOWNTO 0)--滤波后结果); END FIR_filter; ARCHITECTURE behave OF FIR_filter IS --产生带噪声的正弦波COMPONENT sin_noise ISPORT (clk_in : IN STD_LOGIC;reset_p : IN STD_LOGIC;sin_and_noise : OUT STD_LOGIC_VECTOR(9 DOWNTO 0));END COMPONENT;--分频模块COMPONENT div_clk ISPORT (clk_in : IN STD_LOGIC;clk_out : OUT STD_LOGIC);END COMPONENT;--8阶线性相位结构FIRCOMPONENT FIR ISPORT (clk : IN STD_LOGIC;reset_p : IN STD_LOGIC;data_in : IN STD_LOGIC_VECTOR(9 DOWNTO 0);fir_data : OUT STD_LOGIC_VECTOR(9 DOWNTO 0));END COMPONENT;--定义内部信号SIGNAL data_in : STD_LOGIC_VECTOR(9 DOWNTO 0);SIGNAL clk_100K : STD_LOGIC; BEGIN--分频模块,50M分频到100K i_div_clk : div_clkPORT MAP (clk_in => clk_in,clk_out => clk_100K);--产生带噪声的正弦波 i_sin_noise : sin_noisePORT MAP (clk_in => clk_in,--50MHzreset_p => reset_p,--高电平复位sin_and_noise => data_in--产生带噪声的正弦波);--8阶线性相位结构FIRi_FIR : FIRPORT MAP (clk => clk_100K,--100Kreset_p => reset_p,--高电平复位data_in => data_in,--周期1K,噪声频率30K左右fir_data => fir_data--滤波后结果);END behave;

设计文档(以VHDL工程文件为例,verilog同理):

设计文档.doc

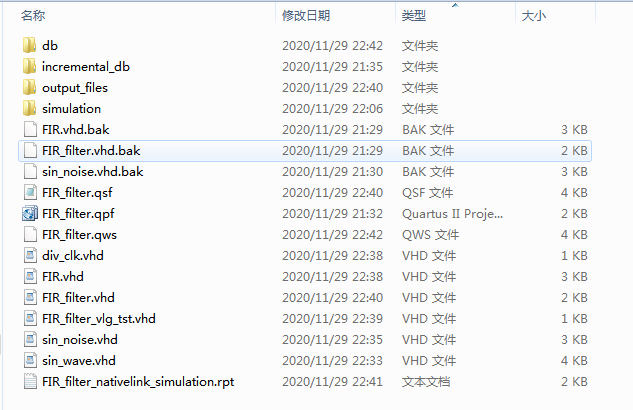

1. 工程文件

2. 程序文件

3. 程序编译

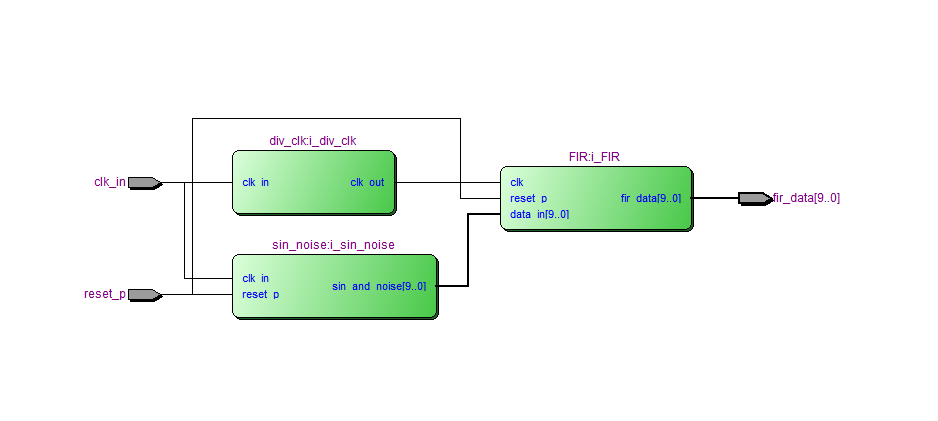

4. RTL图

5. Testbench

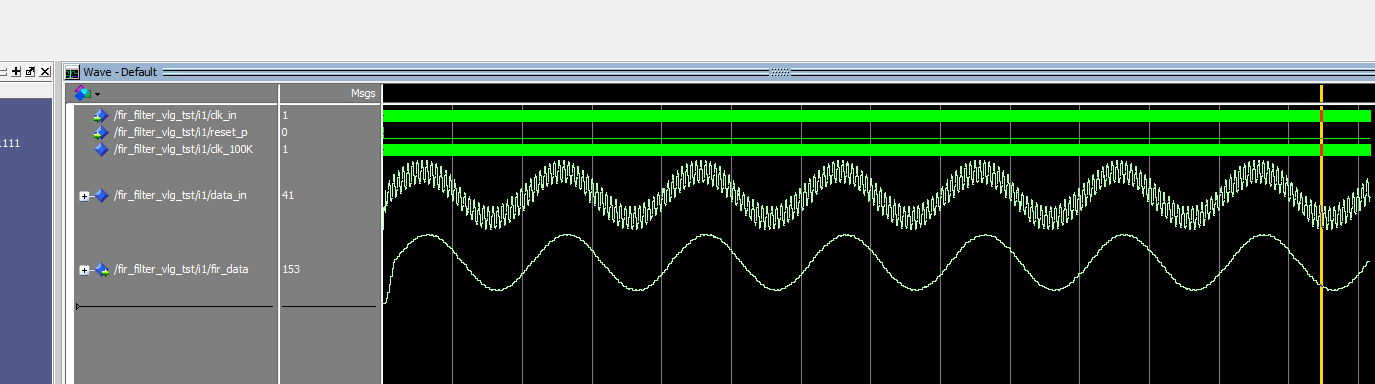

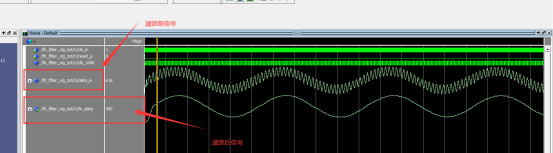

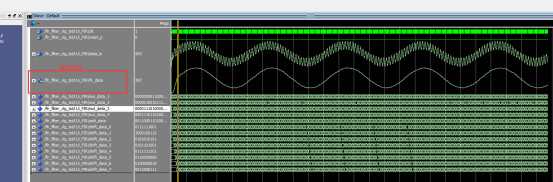

6. 仿真图

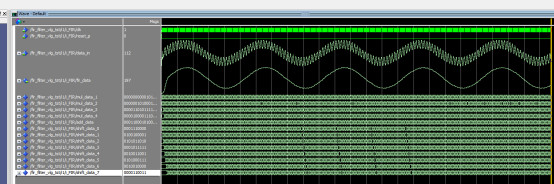

整体仿真

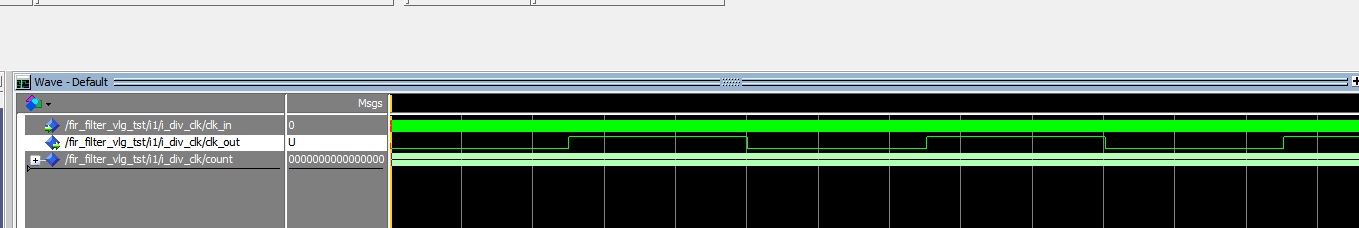

分频模块仿真

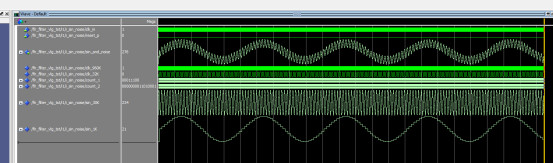

产生带噪声正弦波模块仿真

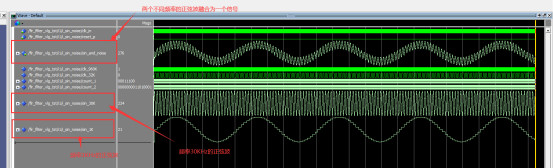

滤波器模块仿真

这篇关于FPGA设计FIR滤波器低通滤波器,代码及视频的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!