本文主要是介绍vivado如何快速找到schematic中的object,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

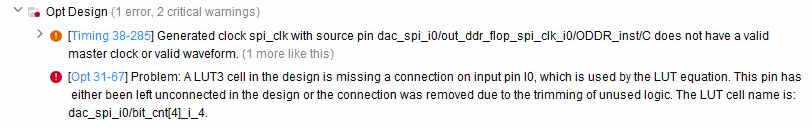

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错,比如:

报的错误是dac_spi_i0/bit_cnt[4]_i_4的这个LUT有个输入悬空了,这个工程的逻辑比较简单,例化的嵌套也比较少,因此在schematic一层层找也很容易可以找到,但如果工程比较复杂,在很内部的一个LUT的输入悬空了,找起来就很费劲了。

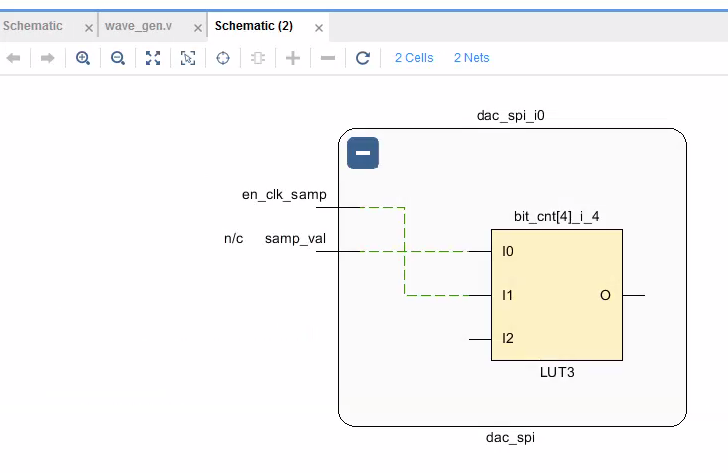

笔者碰到的问题是在vivado的axi-interconnect ip中报了这个错误,而且是ip内部套了好几层的地方,如果再一层层往下找就比较麻烦了,不过vivado提供了tcl指令可以帮我们快速找到这个LUT在schematic中的位置:

show_schematic [get_cells dac_spi_i0/bit_cnt[4]_i_4]

就会快速定位到schematic中的位置:

微信公众号:傅里叶的猫

这篇关于vivado如何快速找到schematic中的object的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!