本文主要是介绍CY7C68013A芯片与FPGA,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 环境

- 软件环境

- 其它工具

- USB基础

- USB2.0设备组成

- USB设备模型

- USB设备分层

- USB Host Controller 主机控制器

- 分类

- USB Host

- USB2.0 数据帧

- USB传输

- 事务

- 传输类型

- 芯片 cypress CY7C68013

- 开发包安装

- FX3

- 固件程序设计

- 步骤

- 驱动程序设计

- 计算机上层应用软件

- USB2.0 FPGA

- USB基础

- 资料

- 官方文档

- 其它工具

- 电路设计

环境

软件环境

KEIL:嵌入式软件的开发。

Vivado 或 quartus :FPGA(可编程门阵列)和SoC(系统片上集成电路)开发。

其它工具

CyConsole

Signaltap:抓取数据验证FPGA接受到数据的正确性。

USB基础

USB2.0设备组成

每一个USB设备由一个或多个配置来控制其行为(对操作系统的支持);一个配置是由**接口(Interface)组成;接口则是由管道(Pipe)组成;管道是和USB设备的端点(Endpoint)**对应,端点都是输入输出成对的。在固件编程中,USB设备、配置、接口和管道都来描述符来报告其属性。

管道的端点总是成对出现,即In Endpoint和Out Endpoint。

In Endpoint:由device向Host发送数据的端点。

Out Endpoint:由Host向device发送数据的端点。

端点0默认为控制管道,其它端点可以配置成数据管道。一个具体的端点,只能工作在一种传输模式下。

USB设备模型

- 主机(host)控制端作为主机端,驱动的设备是USB Host Controller。

- 外设端被称为设备端,驱动的设备是USB Device Controller。

由于USB协议的主从定位思想,从设备只需要响应主机控制器的请求,不能主动发起请求,通常所说的USB驱动都是指主机端的驱动程序。

但近年来随着嵌入式设备的广泛使用,运行Linux系统嵌入式设备也需要通过USB协议与主机端通信,因此从设备端的Linux也需要进行USB设备驱动程序开发,为了避免和主机端的USB设备驱动开发混淆,就将运行Linux的从设备驱动开发称为USB gadget driver。

USB设备分层

USB设备被分为三层:

usb host controller:最底层,也是总线接口层,负责传输和接收数据包;

usb core:USB核心层,Linux系统已经根据USB协议规范实现的通用接口。作为中间层,主要完成总线与设备上端点的通信,端点是数据最终的生产者和消费者,一个设备可以有多个端点。因此,这一层其实就是总线和端点的路由。

usb function:USB功能层,调用下层的接口实现不同的功能,如USB鼠标、USB键盘、USB话筒。通常的USB驱动开发指的都是这层的工作。

USB设备驱动开发-USB协议相关(一)

USB Host Controller 主机控制器

USB 设备和主机的接口,一个主机可以支持多个host controller。控制所有的USB设备的通信。

CPU把要做的事情分配给主机控制器,主机控制器替他去完成剩下的事情,事情办完了再通知CPU。绝对不应该偷偷加工数据。

主机控制器控制总线上包的传输, 使用1ms或125us的帧。包在帧中被传输,或由Host到Device(out事务),或由Device到Host(in事务)。传输总是由Host发起(轮询传输)。回此每条USB总线只能有一个Host。

分类

- UHCI: Universal Host Controller Interface (通用主机控制接口, USB1.0/1.1)。

- OHCI: Open Host Controller Interface (开放主机控制接口,USB1.0/1.1)。负责处理全速/低速设备。

- EHCI: Enhanced Host Controller Interface (用于USB2.0高速设备的“增强主机控制接口”)。主要针对高速的USB设备。

Warning:当端口被OHCI所拥有时,没办法插入个高速设备。只有EHCI控制器才能识别出设备是全速、高速还是低速。

USB主机控制器(Host Controller)–深入理解

USB Host

- USB Host:该设备可以作为USB主机连接USB外围设备,如连接U盘、键盘、鼠标等。一般的PC机的USB接口都是USB Host Only的模式。

- USB Device(target、Slave):该设备可以以U盘的身份连接USB主机。从设备,属于被控制设备,可输入输出数据。

- USB OTG全称是USBOn-The-Go,属于直接控制和传输设备,既可以做USB HOST也可以做USB Slave,通过ID信号来控制主、从切换。

什么是USBHOST、USB Slave和USB OTG?它们之间有什么区别?

USB2.0 数据帧

USB2.0和USB1.1规范的最大不同就是数据帧。在USB1.1规范中,USB数据采用每毫秒一个数据帧的方式进行数据传输,在毫秒数据帧的开始,USB主机首先产生帧开始(SOF)数据包,并传输当前数据帧号,后面是传输数据。

对于USB2.0规范,为了支持480Mbps高速传输速度,USB2.0提出了微帧的概念,每毫秒数据帧又包含8个微帧。

USB传输

虽然USB定义了数据在总线上传输的基本单位是包,但是我们还不能随意地使用包来传输数据,必须按照一定的关系把这些不同的包组织成事务才能传输数据。

事务

通常由两个或者三个包组成:令牌包,数据包和握手包。

- 令牌包用来启动一个事务,总是由主机发送。

- 数据包传送数据,可以从主机到设备,也可以从设备到主机,方向由令牌包来制定。

- 握手包的发送者通常为数据接收者,当数据接收正确后,发送握手包。设备也可以使用NAK握手包来表示数据还未准备好。

传输类型

- 批量传输。通常用于数据量大,对数据的实时性要求不高的场合。

- 等时传输(同步传输)

- 中断传输

- 控制传输

其中,批量传输、等时传输、中断传输每传输一次数据都是一个事务;控制传输包括三个过程,建立过程和状态过程分别是一个事务,数据过程则可能包含多个事务。

芯片 cypress CY7C68013

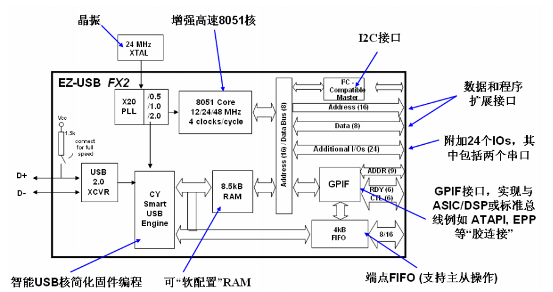

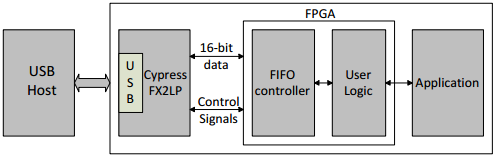

可以通过两个不同的模式将 FX2LP 连接至 FPGA。这两个模式分别为通用可编程接口( GPIF)模式和从设备 FIFO模式。

USB通讯基FPGA的CY7C68013A实现(2)

开发包安装

官方开发包地址:

CY3684工具包

05: CY3684 68013开发套件安装指南

FX3

EZ-USB™ FX3 Software Development Kit

固件程序设计

步骤

- 双击打开C:\Cypress\USB\CY3684_EZ-USB_FX2LP_DVK\1.1\Firmware\Bulkloop\bulkloop.Uv2,将用keil编译器打开。

- 打开Project->Components,Environmem,Bookx…,修改安装路径

- Keil编译成功后的是HEX格式的,又经过了Cypress的hex2bix程序转换成了iic文件。

EZ-USB FX2LP,CY7C68013A学习笔记[1]

CY7C68013A之keil编译代码

驱动程序设计

计算机上层应用软件

USB2.0 FPGA

USB基础

图解USB设备的枚举 过程

资料

一天一个设计实例-FPGA和USB(二)

CY7C68013A教程

CY68013 FPGA通信联调总结

基于CY7C68013A芯片的USB2.0设计

Cypress固件架构彻底解析及USB枚举

基于CY7C68013A的FPGA配置和通信接口设计

Window XP驱动开发(十三) 芯片功能驱动端 (代码实现,针对USB2.0 芯片CY7C68013A)

window xp 驱动(USB

FPGA USB FX2 图片发送试验 驱动CY7C68013A实现 提供2套工程源码和技术支持

CY7C68013A driver for MAC OS

官方文档

EZ-USB™ FX2LP FX2G2 USB 2.0 Peripheral Controller

其它工具

基于EZ-USB FX2 CY7C68013A模块的应用(一)——FX2 芯片片上回环测试

电路设计

USB通讯基FPGA的CY7C68013A实现(2)

Cy7c68013A驱动电路设计注意事项

这篇关于CY7C68013A芯片与FPGA的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!