本文主要是介绍40. DDR2内存初始化代码分析-3,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

rd_fetch计算公式。 假设delay=0,则rd_fetch=0.75向上取整数=1

在write的情况下,假设device无delay。

write命令发出后,经过WL=(RL-1),DQ总线上开始输出数据,总线被device端收入数据时,也应该对DQS相移90度,刚好在data-eye的中心位置收入数据。在device端的DLL只是做时钟同步,而不是做相移,因此相移90°的功能就交给controller端去完成。具体做法:DMC端发出DQ后,延迟90°才发DQS,device端看到DMC端发过来的DQS后才收入收据。 延时90°的功能由Controller端的DLL实现。成本原因。

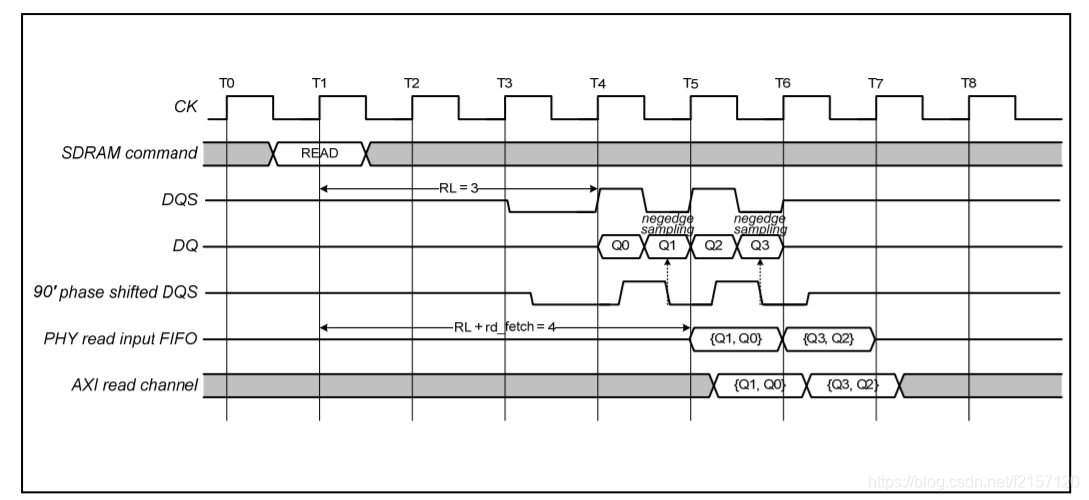

读/写锁存数据的器件不同,从而导致读写时序的不同。读数据:CPU读取,是由CPU从总线上取走数据,因此,此时是DMC发read命令,同时发clk,device回DQS,DMC对DQS延时90°后取走数据。

写数据:Device锁存数据,DMC发数据后,同时发送相对于DQ相位移动了90°的DQS信号,device收到DQS以后锁存数据。

这就是写数据时,特别需要加一个物理层的DLL的原因。

这篇关于40. DDR2内存初始化代码分析-3的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!