ddr2专题

LATTICE进阶篇DDR2--(1)获取官网DDR2例程并仿真

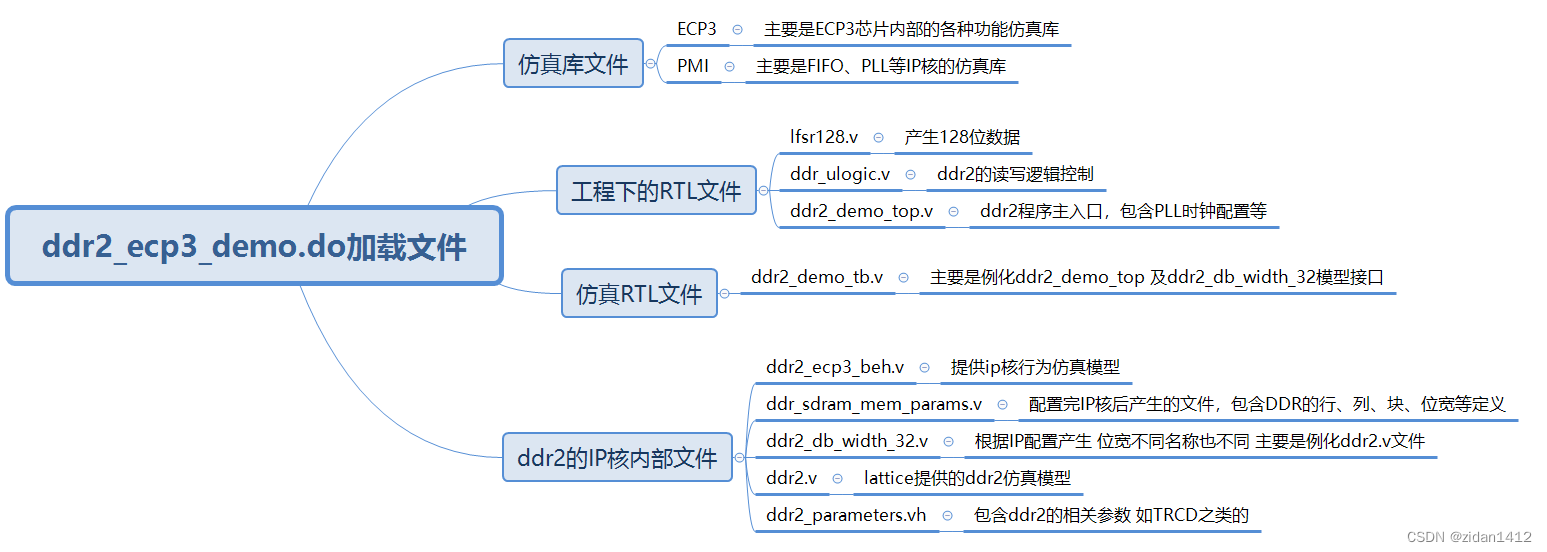

前言 本章主要讲述如何从官网下载DDR2的DEMO例程,并将例程的仿真运行起来。 官网的DEMO在Diamond工程里是没有调用任何任何IP核的,只是在仿真的时候调用了CORE文件夹下的IP核源文件进行仿真,该DEMO工程主要是拿来产生仿真波形,对比IP核数据手册学习DDR2的控制时序,在真正的工程中,我们是需要单独去配置调用IP核的。 器件:Lattice ECP3 环境:win10

LATTICE进阶篇DDR2--(0)获取ddr2 IP核

前言 想要仿真lattice的DDR2由来已久,但苦于对其了解甚少,在查阅过很多资料后,终于对这个IP核的仿真有了一些了解。 现做一些总结,以备不时之需,也让有需要的朋友,少走一些弯路。 环境:win10 + Diamond3.13 首先我们要知道,像DDR2这种IP核,是需要我们自己去联网下载的。 下载有两种方法,通过Diamond联网下载,或者前往Lattice官网进行下载。 方法

从内部结构分析DDR2到DDR3的变化及DDR3原理图分析

1、概述 内存的升级都是为容量和读写速度服务的,每次升级无疑会使容量、读写速度增加、功耗降低,从而引起的一些硬件和时序变化。 从SDRAM芯片内部结构分析其原理,从内部结构讲解SDRAM与DDR的变化,从内部结构讲解DDR到DDR2的变化。 下图列出了从SDRAM到DDR3每代内存的时钟频率范围和预取长度,SDRAM内核时钟频率和接口时钟频率一致,在每个时钟的上升沿传输数据,不需

DDR3和DDR2和DDR的工作原理及技术区别

DDR2与DDR的区别 (1)DDR的定义: 严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,部分初学者也常看到DDR SDRAM,就认为是SDRAM。DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系。 SDRAM在一个时钟周期内只传输

DDR2(SDRAM)初始化 28个步骤总结

S5PV210 DDR2初始化 28个步骤总结 首先在初始化DDR之前,引入一个关于DRAM Drive Strength的概念----DRAM Drive Strength(也被称为:driving strength),表示“DRAM驱动强度”。这个参数用来控制内存数据总线的信号强度,数值越高代表信号强度越高,增加信号强度可以提高超频的稳定性。但是并非信号强度高就一定好。所以,这里我们

DDR2学习笔记(3)

READ指令 (1)READ指令用来初始化一个触发读存储到一个被激活的行上。变量BA1,BA0用来选择bank,A0-A9用来选择在bank中的列,A10决定是否使用auto precharge。如果选择了auto precharge,该行在读操作结束之后变为precharge;如果没有选择auto precharge,该行在结束读操作之后为随后的存取保持激活状态。 开启READ 指令的

烧友必看 主流DDR2内存芯片编号识别

前言: DDR2已经渐成主流,虽然在很多人的眼中,DDR2仍然有着这样或那样的不足,但在业界主力厂商的大力推广下,在CPU平台不断向更高频率冲刺的时候,DDR2代替原有的DDR已经不可避免。因此,我们推出这篇导购文章,希望能给大家在选购DDR2内存模组时提供帮助。本文的编号资料截止至2005年6月。 1、三星(SAMSUNG) 三星电子DDR2内存芯片外观 三星电子有关DDR2内存芯

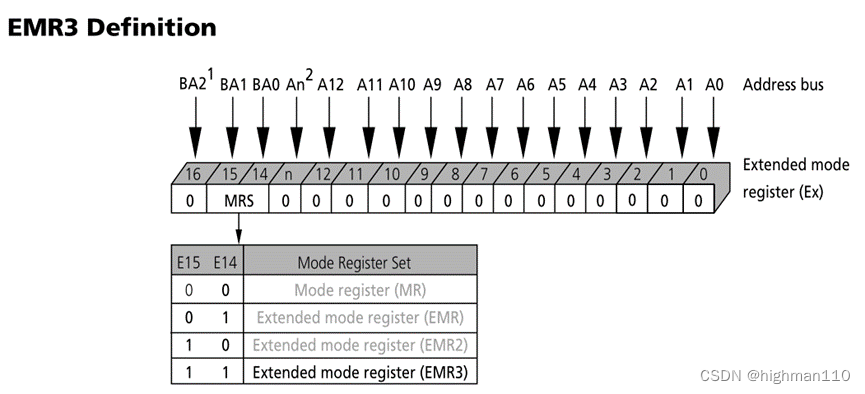

【DRAM存储器十六】DDR2介绍-DDR到DDR2的变化、DDR2框图详解、模式寄存器

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR数据手册》 目录 DDR2 SDRAM介绍 DDR2相对DDR的变化 DDR2 SDRAM芯片框图 DDR2 SDRAM的mode register DDR2 SDRAM介绍 到DDR2了,同样以镁

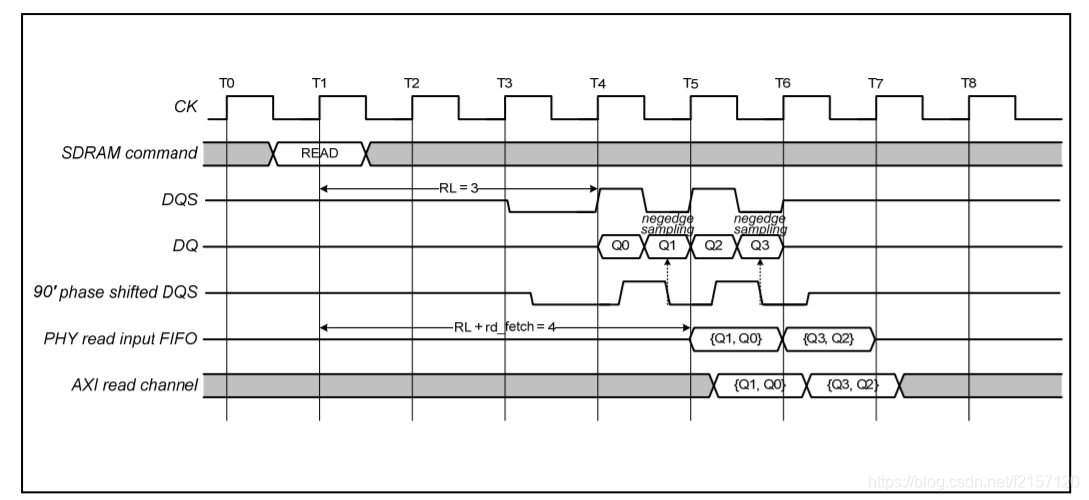

40. DDR2内存初始化代码分析-3

rd_fetch计算公式。 假设delay=0,则rd_fetch=0.75向上取整数=1 在write的情况下,假设device无delay。 write命令发出后,经过WL=(RL-1),DQ总线上开始输出数据,总线被device端收入数据时,也应该对DQS相移90度,刚好在data-eye的中心位置收入数据。在device端的DLL只是做时钟同步,而不是做相移,因此相移90°的功