本文主要是介绍FPGA-VHDL-竞赛抢答器设计(平台实现)-2023,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

题目四:竞赛抢答器设计(平台实现)★

- 抢答器的输入路数为8路;(8位二进制输入)

- 当主持人宣布开始(拨下A7键时为有效),抢答时当某一方先按下按键,其他键则失效;

- 用一个数码管显示抢中的路编号,并开始进行60秒倒计时(用两个数码管显示),时间到用一指示灯进行闪烁提示;

- A7键回位后,进行下一轮抢答。

重要的事情说三遍:

可以参考,不要伤害认真做的同学!

可以参考,不要伤害认真做的同学!

可以参考,不要伤害认真做的同学!

VHDL代码:

------------------This is Main Code,Please set it to Top level Entity------------------------

--%%%%%%%%%%%%%%%%%%%%%

--%%|YZM-- (^@^)/ hi|%%

--%%|21******** |%%

--%%|2023.4.5 |%%

--%%%%%%%%%%%%%%%%%%%%%

library ieee;

use ieee.std_logic_1164.all;

entity Main is

generic (Num:integer :=8); --4 is Digital frequency num;

----------------------------------------------------------------------------------------

port(frequency_in: in std_logic_vector(0 to 3); --待测频率(选择frequency_in(0)为基准频率)Choose_Frequency_in: in std_logic_vector(0 to Num-1); --开关选择seg_sel: out std_logic_vector(6 downto 0); --数码管信息bit_sel: out std_logic_vector(7 downto 0); --数码管选择Led_out: out std_logic_vector(7 downto 0); begin_start: in std_logic );

end Main;

----------------------------------------------------------------------------------------

architecture Digital_frequency_meter_design_main of Main is

----------------------------------------------------------------------------------------type showIndex is array (0 to 7) of natural; --数组存储数码管信息signal showers: showIndex; --数码管signal Nixie_tube_NOW :integer:= 0; --数码管显示位置状态signal TIME_NOW:integer := 60; --时间状态signal NowClk: std_logic; --1hz频率signal Set_END:integer:=0; --结束标志signal CHOOSE_1:std_logic:='0'; --按键标志signal CHOOSE_2:std_logic:='0'; --按键标志signal CHOOSE_3:std_logic:='0'; --按键标志signal CHOOSE_4:std_logic:='0'; --按键标志signal CHOOSE_5:std_logic:='0'; --按键标志signal CHOOSE_6:std_logic:='0'; --按键标志signal CHOOSE_7:std_logic:='0'; --按键标志signal CHOOSE_8:std_logic:='0'; --按键标志signal INPUT_NUM:integer := 0; --频率选择状态

----------------------------------------------------------------------------------------begin

--###############################选择状态进程############################### SCAN_1: process(frequency_in(1))beginif Choose_Frequency_in(0)'event and Choose_Frequency_in(0)= '1' then CHOOSE_1<=not (CHOOSE_8 or CHOOSE_2 or CHOOSE_3 or CHOOSE_4 or CHOOSE_5 or CHOOSE_6 or CHOOSE_7 );end if;if Choose_Frequency_in(1)'event and Choose_Frequency_in(1)= '1' then CHOOSE_2<=not (CHOOSE_1 or CHOOSE_8 or CHOOSE_3 or CHOOSE_4 or CHOOSE_5 or CHOOSE_6 or CHOOSE_7 );end if;if Choose_Frequency_in(2)'event and Choose_Frequency_in(2)= '1' then CHOOSE_3<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_8 or CHOOSE_4 or CHOOSE_5 or CHOOSE_6 or CHOOSE_7 );end if;if Choose_Frequency_in(3)'event and Choose_Frequency_in(3)= '1' then CHOOSE_4<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_3 or CHOOSE_8 or CHOOSE_5 or CHOOSE_6 or CHOOSE_7 );end if;if Choose_Frequency_in(4)'event and Choose_Frequency_in(4)= '1' then CHOOSE_5<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_3 or CHOOSE_4 or CHOOSE_8 or CHOOSE_6 or CHOOSE_7 );end if;if Choose_Frequency_in(5)'event and Choose_Frequency_in(5)= '1' then CHOOSE_6<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_3 or CHOOSE_4 or CHOOSE_5 or CHOOSE_8 or CHOOSE_7 );end if;if Choose_Frequency_in(6)'event and Choose_Frequency_in(6)= '1' then CHOOSE_7<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_3 or CHOOSE_4 or CHOOSE_5 or CHOOSE_6 or CHOOSE_8 );end if;if Choose_Frequency_in(7)'event and Choose_Frequency_in(7)= '1' then CHOOSE_8<=not (CHOOSE_1 or CHOOSE_2 or CHOOSE_3 or CHOOSE_4 or CHOOSE_5 or CHOOSE_6 or CHOOSE_7 );end if;if begin_start='1' then CHOOSE_1<='0'; CHOOSE_2<='0'; CHOOSE_3<='0'; CHOOSE_4<='0'; CHOOSE_5<='0'; CHOOSE_6<='0'; CHOOSE_7<='0'; CHOOSE_8<='0';end if;if CHOOSE_1='1' then INPUT_NUM<=1;else if CHOOSE_2='1' then INPUT_NUM<=2;else if CHOOSE_3='1' then INPUT_NUM<=3;else if CHOOSE_4='1' then INPUT_NUM<=4;else if CHOOSE_5='1' then INPUT_NUM<=5;else if CHOOSE_6='1' then INPUT_NUM<=6;else if CHOOSE_7='1' then INPUT_NUM<=7;else if CHOOSE_8='1' then INPUT_NUM<=8;else INPUT_NUM<=0;Set_END<=0;end if; end if; end if; end if; end if; end if; end if; end if;if TIME_NOW=0 then Set_END<=1; end if;end process SCAN_1;

-----------------------------------------------------------------------------

--###############################基础频率产生进程############################Create_1Hz_Clk: process(frequency_in(0))variable clk_count: integer := 0;beginif frequency_in(0)'event and frequency_in(0) = '1' then if clk_count = 375000 thenclk_count := 0;NowClk<=not NowClk;if Set_END/=1 then TIME_NOW<=TIME_NOW-1; end if; if INPUT_NUM=0 then TIME_NOW<=60; end if;else clk_count := clk_count + 1;end if;Nixie_tube_NOW <=( Nixie_tube_NOW + 1)mod 8;end if;end process Create_1Hz_Clk;

------------------------------------------------------------------------------

Show_Num: process(frequency_in(0))

beginshowers(4)<=INPUT_NUM;if TIME_NOW>=10 thenshowers(0)<=(TIME_NOW-(10*(TIME_NOW/10)));else showers(0)<=TIME_NOW;end if;showers(1)<=TIME_NOW / 10 ;end process Show_Num;

------------------------------------------------------------------------------

--###############################LED显示进程###############################

Show_End: process(NowClk)

beginif Set_END=1 thenif NowClk='1' then Led_out<="01010101";elseLed_out<="10101010";end if;elseLed_out<="00000000";end if;

end process Show_End;

------------------------------------------------------------------------------

--###############################数码管显示进程############################### SHOW_NIXIE:process(Nixie_tube_NOW) begincase showers(Nixie_tube_NOW) iswhen 0 => seg_sel <= "1111110" ;--数字0when 1 => seg_sel <= "0110000" ;--数字1when 2 => seg_sel <= "1101101" ;--数字2when 3 => seg_sel <= "1111001" ;--数字3when 4 => seg_sel <= "0110011" ;--数字4when 5 => seg_sel <= "1011011" ;--数字5when 6 => seg_sel <= "1011111" ;--数字6when 7 => seg_sel <= "1110000" ;--数字7when 8 => seg_sel <= "1111111" ;--数字8when 9 => seg_sel <= "1111011" ;--数字9when 10=> seg_sel <= "0000000" ;--10是不显示数字when others => Null;end case;case Nixie_tube_NOW iswhen 7 => bit_sel <= "11111111";--数码管7when 6 => bit_sel <= "11111111";--数码管6when 5 => bit_sel <= "11111111";--数码管5when 4 => bit_sel <= "11101111";--数码管4when 3 => bit_sel <= "11111111";--数码管3when 2 => bit_sel <= "11111111";--数码管2when 1 => bit_sel <= "11111101";--数码管1when 0 => bit_sel <= "11111110";--数码管0when others => null;end case;end process SHOW_NIXIE;

end Digital_frequency_meter_design_main;

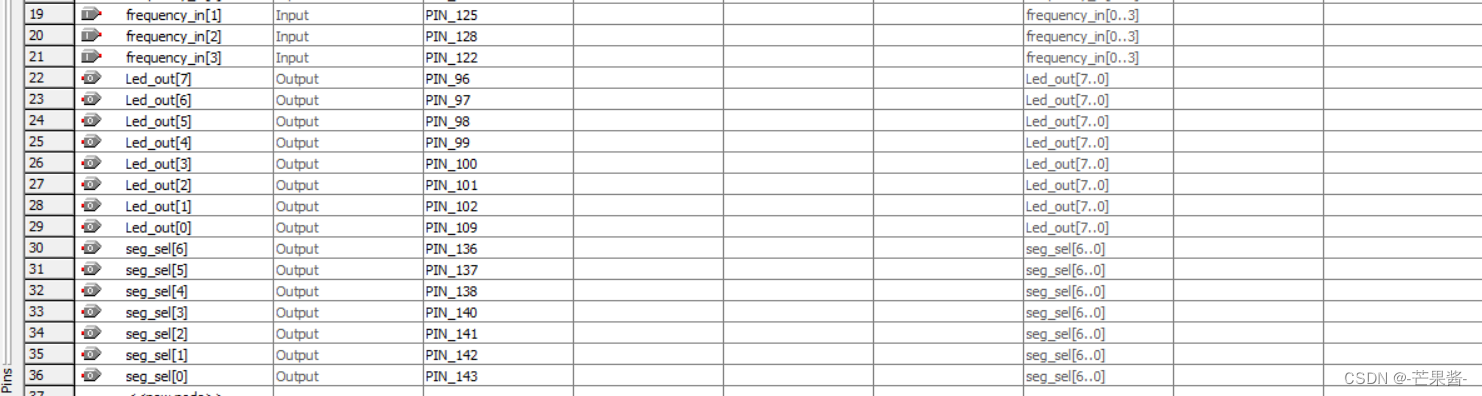

----------------------------------------------------------------------------------------pin设置:

这篇关于FPGA-VHDL-竞赛抢答器设计(平台实现)-2023的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!