本文主要是介绍《CPU设计实战》第四章lab3记录找bug,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

修bug之路

1. debug_wb_pc

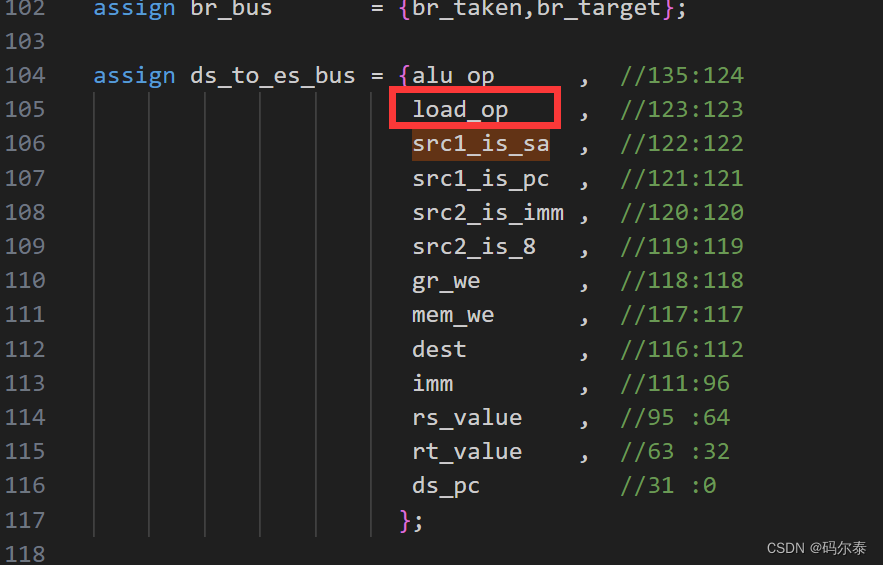

一个信号一个信号找下去,发现ID_stage.v中load_op未赋值

assign load_op = inst_lw;

- 代码解释

module decoder_5_32(input [ 4:0] in,output [31:0] out

);

//这个循环被命名为 gen_for_dec_5_32。

genvar i;

generate for (i=0; i<32; i=i+1) begin : gen_for_dec_5_32assign out[i] = (in == i);

end endgenerate

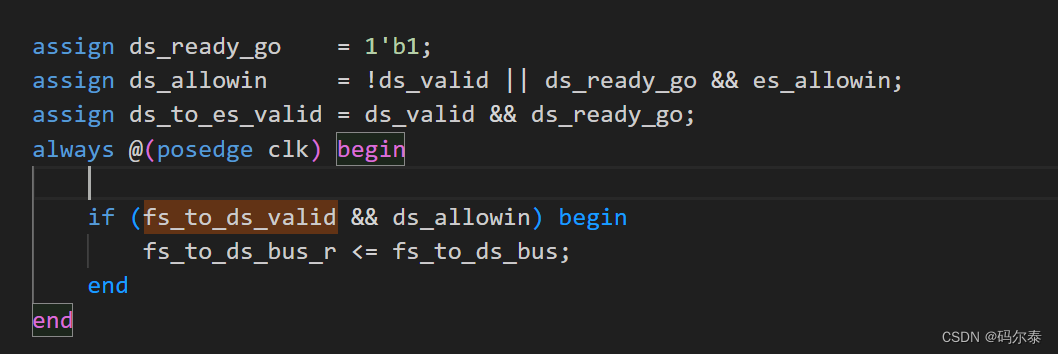

2. ds_valid未赋值

这里没有:

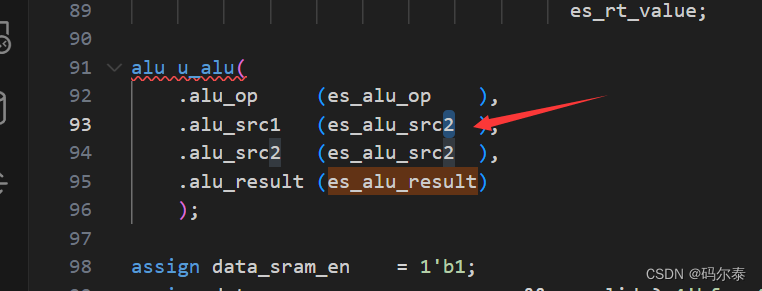

3. 模块实例化错误

alu u_alu(.alu_op (es_alu_op ),.alu_src1 (es_alu_src1 ),.alu_src2 (es_alu_src2 ),.alu_result (es_alu_result));

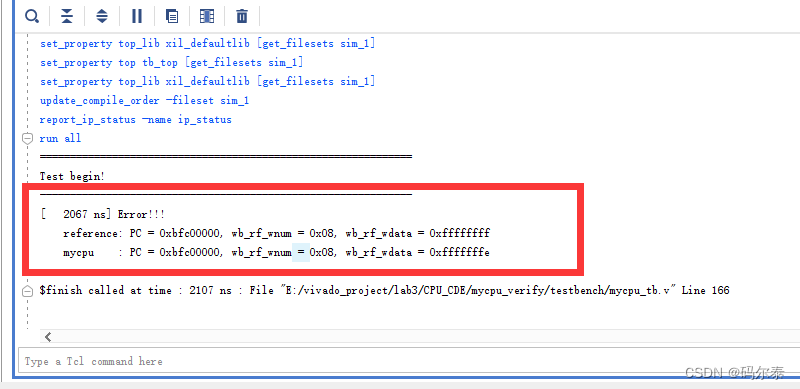

4.

借鉴

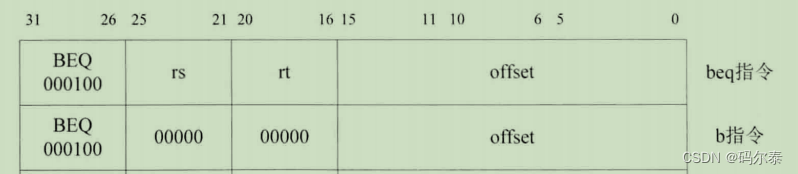

mips指令格式

暂停,学习汇编程序去。

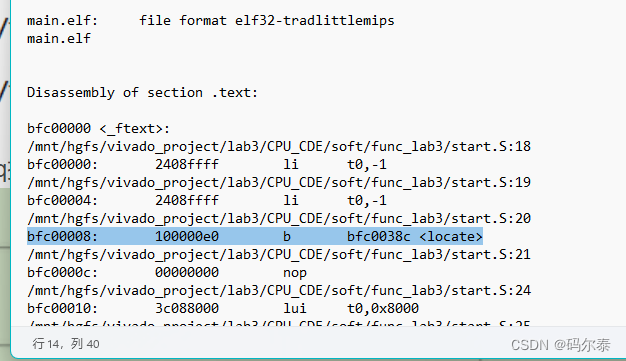

应该跳转到bfc0038c,但是顺序执行了

该bug自己没有解决,借鉴了上面大佬的。

5.

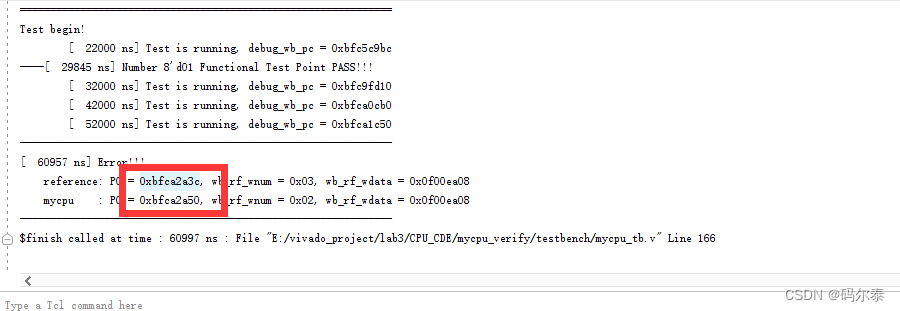

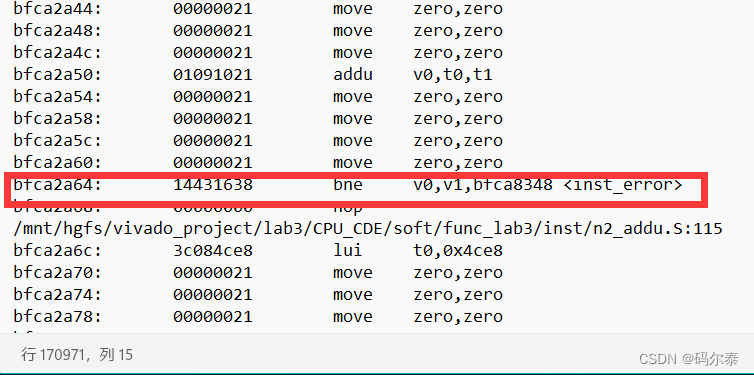

应该还是某个转移指令出错。

有可能是bne。

对rtl代码和如何调试还是不熟悉。剩下的都是参考别人的弄出来的。待补。。。

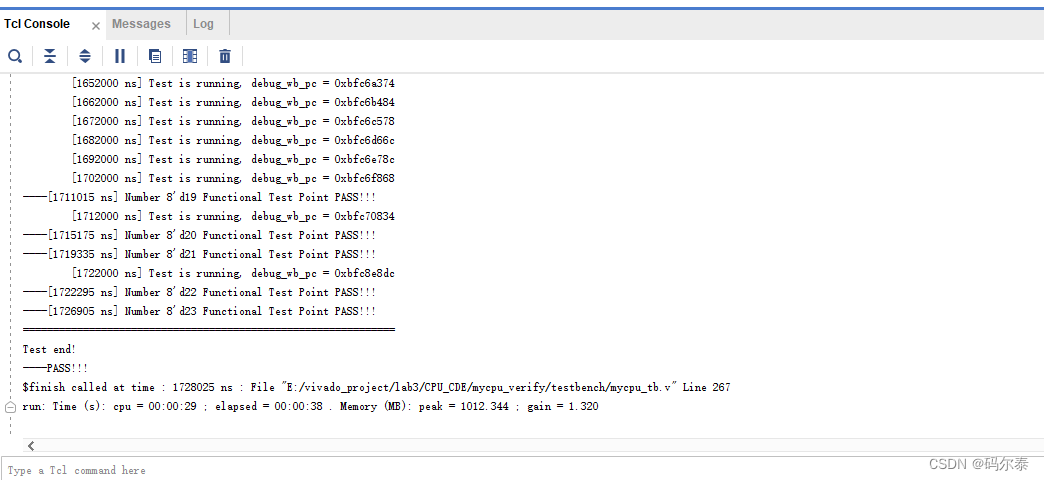

这就算成功了,可是不是自己debug出来的。。。

这篇关于《CPU设计实战》第四章lab3记录找bug的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!