本文主要是介绍翻译_Clock Domain Crossing Design,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

翻译_Clock Domain Crossing Design

原文标题及连接:Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog.

作者:Clifford E. Cummings

Sunburst Design, Inc.

cliffc@sunburst-design.com

摘要

在多时钟设计中,需要在时钟域交叉(Clock Domain Crossing,CDC)边界处仔细构造重要的设计考虑因素。本文详细介绍了一些最新的策略和众所周知的最佳方法,以解决跨CDC边界传递一个或多个信号的问题。

文中包括了与CDC验证相关的技术,以及一个有趣的2深FIFO设计,用于在时钟域之间传递多个控制信号。

尽管本文描述的设计方法通常可以使用任何硬件描述语言(HDL)实现,但示例使用的是高效的SystemVerilog技术。

1.0 引言

在2001年,我提交了我的第一篇关于多异步时钟设计的论文。那时,我没有找到任何好的资源来描述进行适当的多时钟设计所需的设计和综合技术。

2001年的论文是我多年ASIC和FPGA设计经验中收集的技术的集合。在2001年会议演讲结束时,数十位工程师和同事向我分享了足够多的有趣想法和技术,以至于我可以为这个主题写一个续集。在过去的八年里,我在高级和专家级的Verilog和SystemVerilog培训课程中包括了多时钟设计技术的指导,同时在这段时间里,更多的同事和学生与我分享了额外的有趣的多时钟设计技术。

自2001年发布第一篇多时钟论文以来,业界普遍将这些设计方法归类为时钟域交叉(CDC)技术。我将在本文中使用这个通用术语。

本文包括了2001年论文中描述的最佳技术,以及在过去十年中与我分享的更新的有趣和高效的多时钟设计技术的集合。实际的会议演讲幻灯片将主要是自2001年原始演讲以来纳入的新技术的集合,只保留足够的原始幻灯片来介绍基本的CDC设计概念和问题。

2.0 亚稳态

亚稳态指的是在设计的正常操作期间,信号在一段时间内不假定稳定的0或1状态。在多时钟设计中,亚稳态无法避免,但可以中和亚稳态的有害影响。

引用Dally和Poulton的书[9]中关于亚稳态的内容:

当用时钟采样一个变化的数据信号时…事件的顺序决定了结果。事件之间的时间差异越小,确定哪个事件先发生所需的时间就越长。当两个事件发生得非常接近时,决策过程可能需要的时间超过了分配的时间,这时就会发生同步失败。

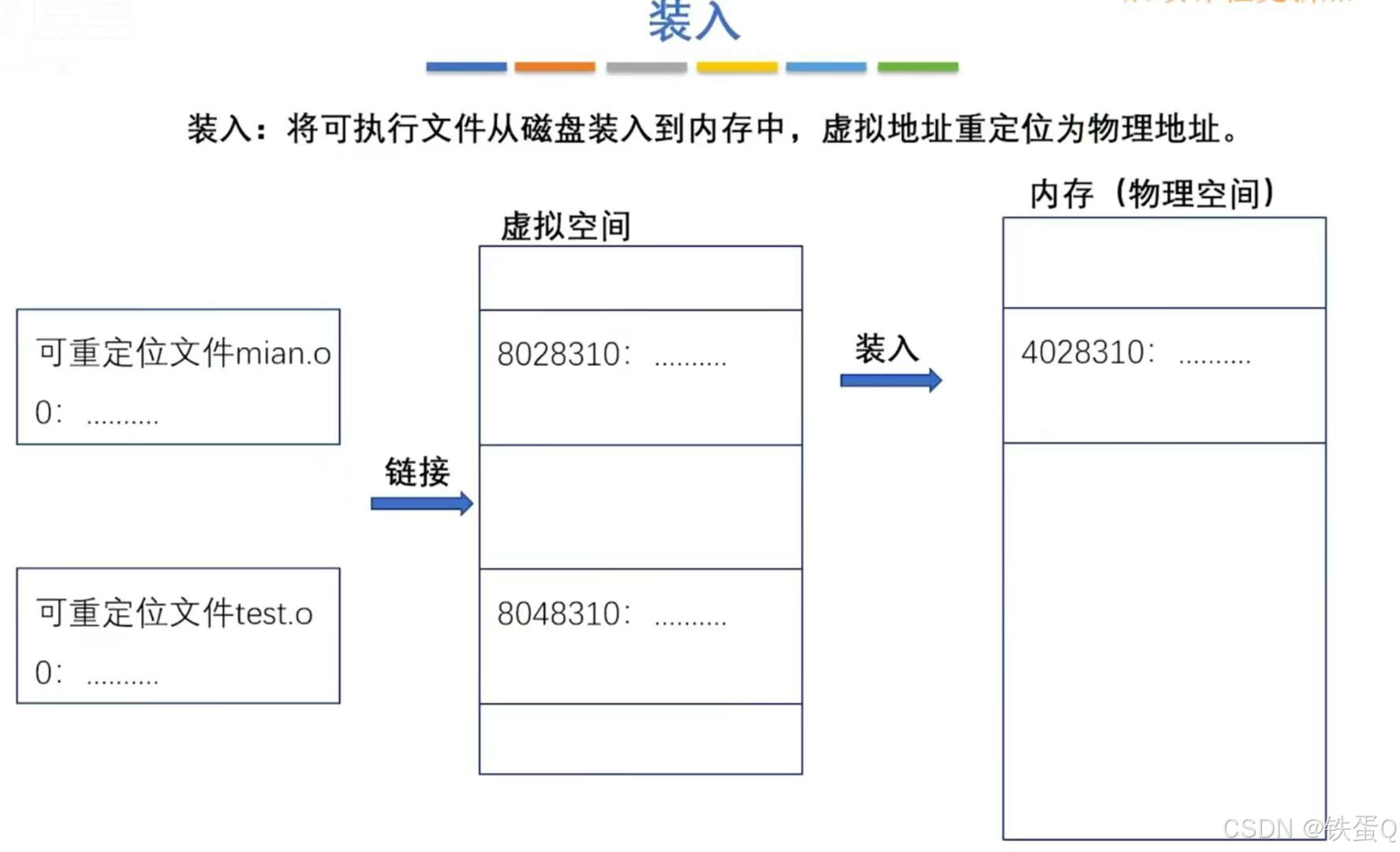

图1显示了当一个在第一个时钟域产生的信号在第二个时钟域的时钟信号的上升沿太近时发生的同步失败。同步失败是由输出进入亚稳态并且在必须再次采样输出之前没有收敛到合法稳定状态引起的。

2.1 为什么亚稳态是个问题?

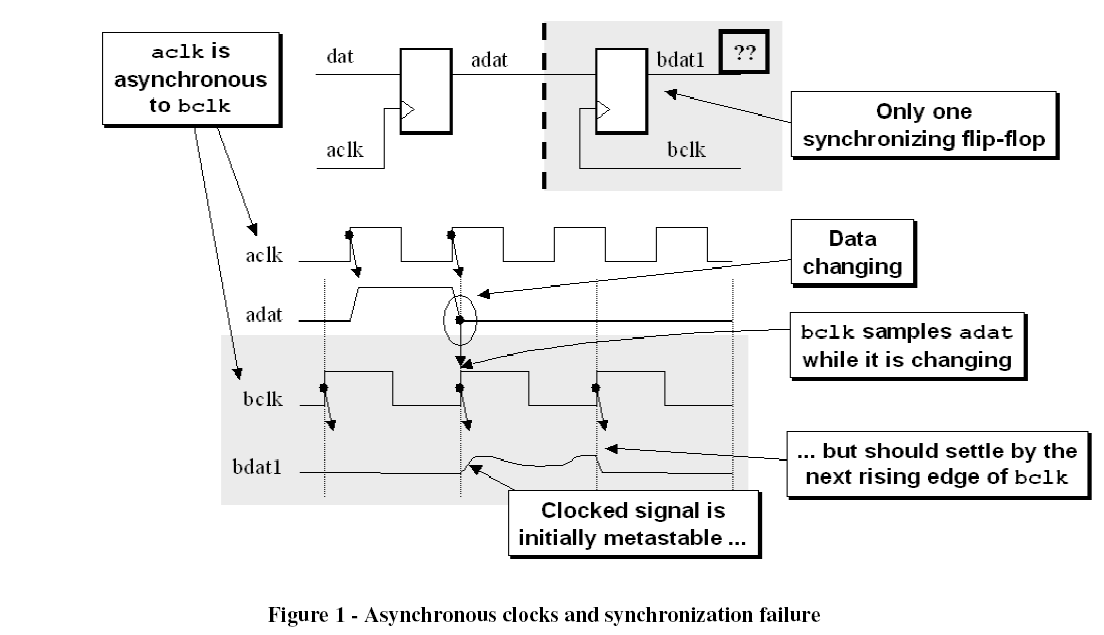

那么,为什么亚稳态是个问题呢?图2显示了一个在接收时钟域中穿越额外逻辑的亚稳态输出,可能会导致整个设计中传播非法信号值。由于CDC信号可能会在一段时间内波动,接收时钟域中的输入逻辑可能会识别波动信号的逻辑电平为不同的值,从而将错误的信号传播到接收时钟域。

每个在设计中使用的触发器都有一个指定的建立时间和保持时间,或者在上升时钟边沿之前和之后数据输入不允许变化的时间。这个时间窗口被精确地指定为设计参数,以防止数据信号在太靠近可能使输出进入亚稳态的另一个同步信号时发生变化。

3.0 同步器

在时钟域之间传递信号时,一个重要的问题是,我是否需要采样从一个时钟域传递到另一个时钟域的信号的每个值?

3.1 两种同步场景

在跨CDC边界传递信号时,有两种可能的场景,确定哪种场景适用于您的设计非常重要:

- 允许在时钟域之间传递的样本被错过。

- 必须采样传递至时钟域之间的每个信号。

**第一种场景:**有时不必采样每个值,但采样的值必须准确。一个例子是标准异步FIFO设计中使用的一组格雷码计数器。在正确设计的异步FIFO模型中,同步的格雷码计数器不需要捕获来自相反时钟域的每个合法值,但关键是采样的值必须准确,以识别何时发生了满和空条件。

**第二种场景:**CDC信号必须在CDC信号上发生变更之前被正确识别或确认。

在这两种场景中,CDC信号将需要某种形式的同步进入接收时钟域。

3.2 双触发器同步器

再次引用Dally和Poulton[9]关于同步器的话:

同步器是一个设备,它采样一个异步信号,并输出一个信号版本,该信号的转换与本地或采样时钟同步。

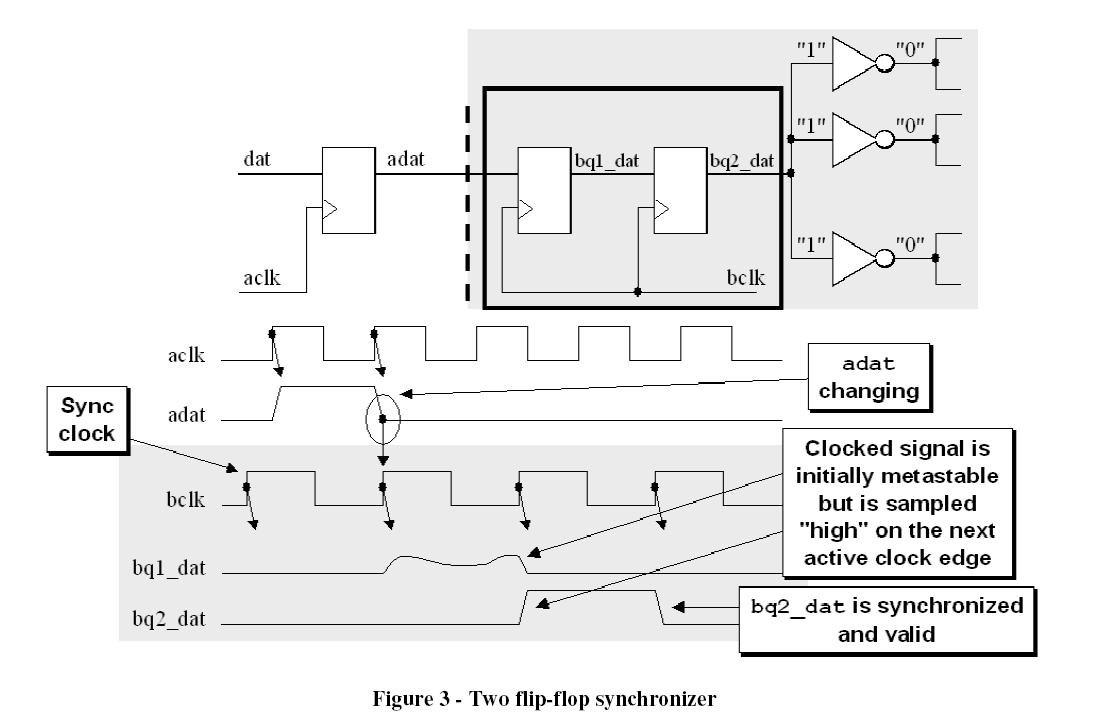

数字设计师使用最简单和最常见的同步器是双触发器同步器,如图3所示。

第一个触发器将异步输入信号采样到新的时钟域,并等待一个完整的时钟周期,以允许任何在第一阶段输出信号上的亚稳态衰减,然后第一阶段信号被相同的时钟采样到第二阶段触发器,预期的目标是,第二阶段信号现在是稳定且有效的信号,已同步并准备好在新的时钟域内分发。

3.3 MTBF - 故障前平均时间

对于大多数同步应用,计算任何穿过CDC边界的信号的故障前平均时间(MTBF)是很重要的。

在这里,故障意味着传递到同步触发器的信号,在第一阶段同步器触发器上变为亚稳态,并在下一个时钟周期后继续是亚稳态,当它被采样到第二阶段同步器触发器时。由于信号在经过一个时钟周期后没有稳定到已知值,信号在被采样并传递到接收时钟域时可能仍然是亚稳态,从而导致相应逻辑中的潜在故障。

当计算MTBF数字时,较大的数字优于较小的数字。较大的MTBF数字表示潜在故障之间的时间较长,而较小的MTBF数字表示亚稳态可能频繁发生,类似地在设计中引起故障。

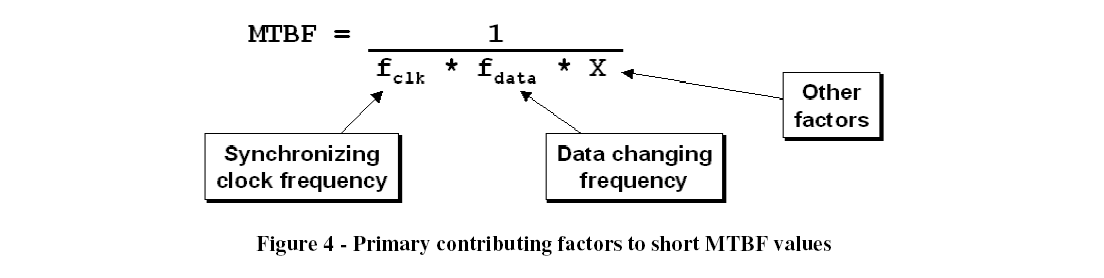

Dally和Poulton[9]给出了一个非常好的方程式和非常彻底的分析,可以执行计算同步器电路的MTBF。不重复方程式和分析,应该指出,直接影响同步器电路MTBF的两个最重要因素是:

-

采样时钟频率(信号被采样进入接收时钟域的速度有多快);

-

数据变化频率(跨CDC边界的数据变化速度有多快)。

从上述部分方程式可以看出,在更高速度的设计中,或者当采样数据变化更频繁时,故障发生的频率更高(MTBF更短)。

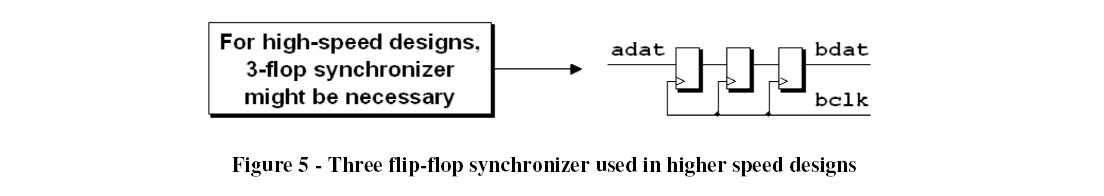

3.4 三触发器同步器

对于一些非常高速度的设计,双触发器同步器的MTBF太短,增加了第三个触发器以增加MTBF到一个令人满意的时间段。当然,令人满意是由设计的架构师决定的。

3.5 从发送时钟域同步信号

**关于CDC设计的一个常见问题是:**在将信号传递到接收时钟域之前,是否有必要对来自发送时钟域的信号进行寄存?

这个问题中隐含的假设是,既然CDC信号将被同步到接收时钟域,因此它们在发送时钟域中不需要同步。这种理论是错误的,通常应该要求在发送时钟域中对信号进行寄存。

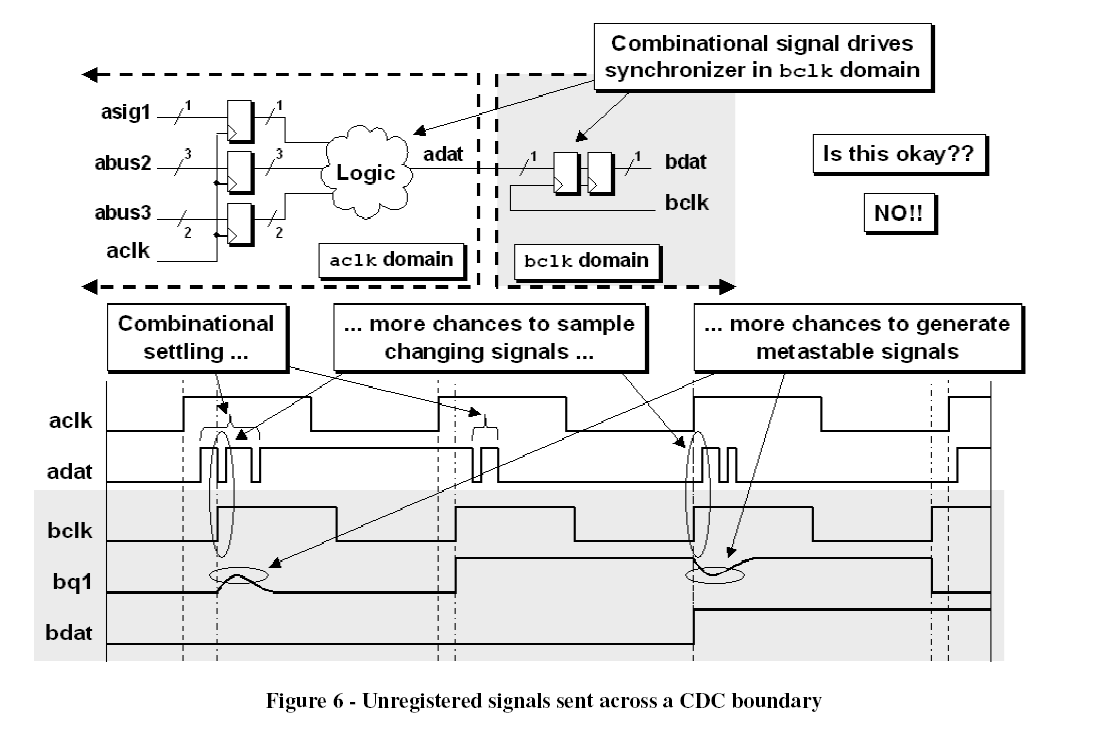

考虑一个示例,其中发送时钟域中的信号在被传递到接收时钟域之前没有进行寄存,如图6所示。

在这个示例中,来自发送时钟域的组合逻辑输出可能在CDC边界处经历组合逻辑稳定过程。

这种组合逻辑稳定实际上增加了数据变化频率,可能会产生短时间的数据振荡,从而增加了在变化时被采样的边缘数量,相应地增加了采样变化数据并产生亚稳态信号的可能性。

3.6 同步信号到接收时钟域

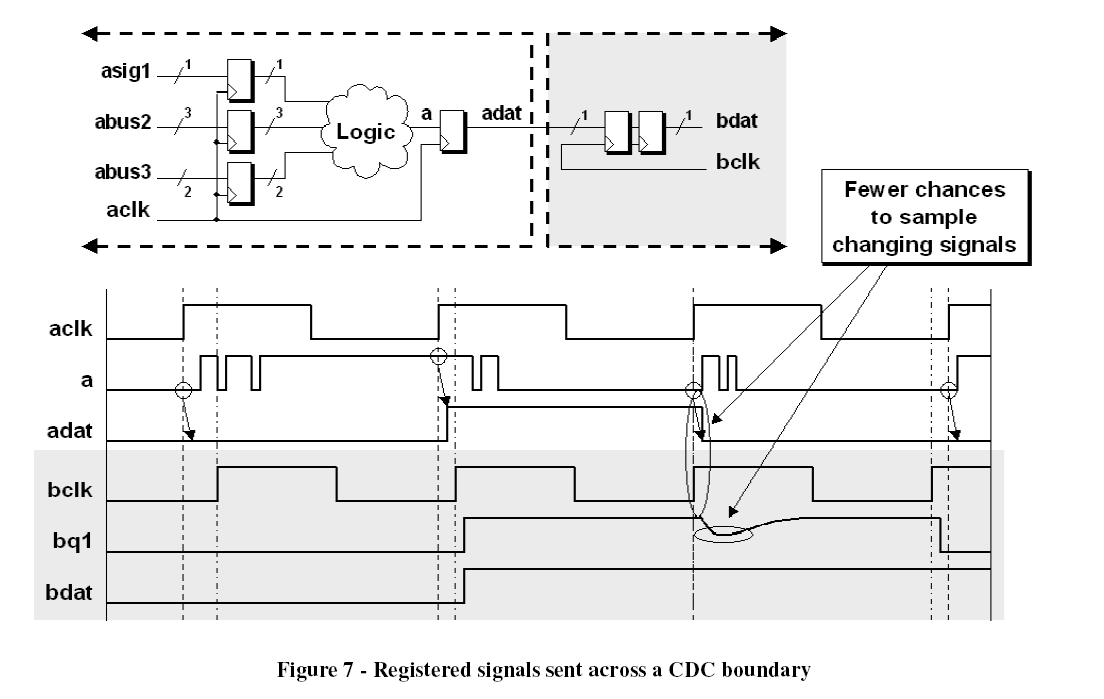

应该在发送时钟域中同步信号,然后再将其传递到CDC边界。

从发送时钟域同步信号可以减少在接收时钟域中可能采样的边缘数量,有效地降低了MTBF方程中的数据变化频率,从而增加了计算出的故障时间(见第3.3节,了解数据变化频率对MTBF的影响)。

在图7中,aclk逻辑在传递到bclk域之前在adat触发器上稳定并设置。adat触发器过滤了触发器输入上的组合逻辑稳定(a),并向bclk逻辑传递了一个干净的信号。

4.0 将快速信号同步到慢速时钟域

如第3.1节所讨论的,如果允许在时钟域之间传递的CDC信号被跳过,则在考虑信号宽度或同步技术时,它们在时钟域之间传递时的重要性就显现出来了。

与同步器相关联的一个问题是,来自发送时钟域的信号可能在被采样之前改变两次值,或者可能太接近慢速时钟域的采样边沿。每当信号从一个时钟域发送到另一个时钟域时,都必须考虑这种可能性,并且必须确定是否遗漏信号对于所讨论的设计来说是否是一个问题。

当不允许遗漏采样时,有两个通用的解决问题的方法:

- 开环解决方案,确保信号被捕捉而无需确认。

- 闭环解决方案,需要确认接收到跨越CDC边界的信号。

本节讨论了这两种解决方案。

4.1 在时钟域之间可靠传递信号的要求

同步较慢的控制信号到较快的时钟域通常不是问题,如果较快的时钟域的频率至少是较慢时钟域的1.5倍,因为较快的时钟信号将至少一次或多次采样较慢的CDC信号。

设计者可能会利用这一事实,通过使用简单的双触发器同步器在时钟域之间传递单个CDC信号。

认识到在较快的时钟域中采样较慢信号比在较慢的时钟域中采样较快信号潜在的问题要少,这有助于简化设计。

4.1.1 “三边沿”要求

Mark Litterick[4]指出,当通过双触发器同步器在时钟域之间传递一个CDC信号时,CDC信号必须比接收域时钟周期的宽度长1.5倍。

Litterick将此要求描述为输入数据值必须在三个目标时钟边沿上保持稳定。

对于源时钟和目的时钟频率异常长的情况,这一要求可能可以安全地放宽到接收时钟域周期时间的1/4倍或更短,但“三边沿”准则是最安全的初始设计条件。相比于在仿真期间动态测量CDC信号的部分宽度,使用SystemVerilog断言来证明这一点更为容易和可靠。

“三边沿”要求实际上适用于开放环和闭环解决方案,但实现闭环解决方案自动确保至少三个边沿被检测到所有CDC信号。

4.2 问题-传递一个快速CDC脉冲

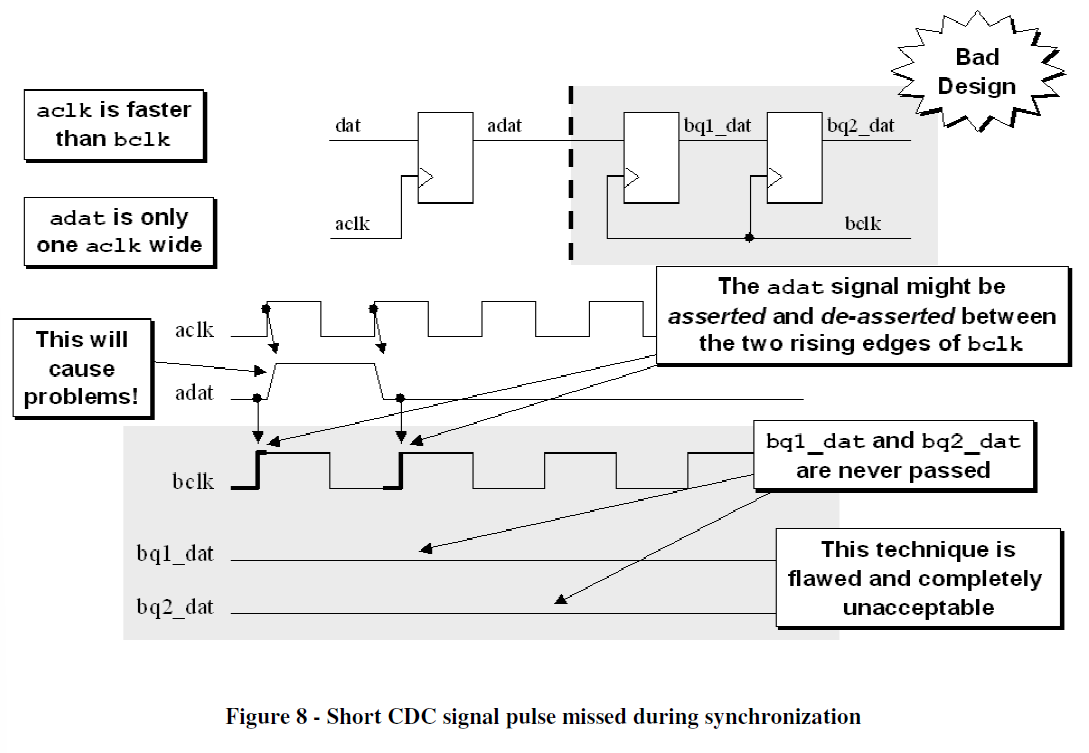

考虑一个严重的问题情况,即发送时钟域的频率高于接收时钟域,且一个CDC脉冲在发送时钟域中只持续一个周期。

如果CDC信号仅在一个快速时钟周期内被激活,那么这个信号可能在慢速时钟的两个上升沿之间变化,从而没有被慢速时钟域捕获,如图8所示。

4.3 问题-采样一个不够长的长CDC脉冲-但是依然不够长

考虑一个有些违反直觉的情况,即发送时钟域向接收时钟域发送一个脉冲,这个脉冲宽度略宽于接收时钟的周期。

在大多数情况下,信号将被采样并通过,但存在一个小但真实的可能性,即CDC脉冲变化得太接近接收时钟域的两个上升时钟边沿,从而违反了第一个时钟边沿的建立时间,并违反了第二个时钟边沿的保持时间,没有形成预期的脉冲。

这种可能的故障情况如图9所示。

这篇关于翻译_Clock Domain Crossing Design的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!