本文主要是介绍vivado PKGPIN_NIBBLE,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

PKGPIN_NIBBLE是PKGPIN_BYTEGROUP的一部分。参见PKGPIN_BYTEGROUP,

第122页了解该对象的描述。

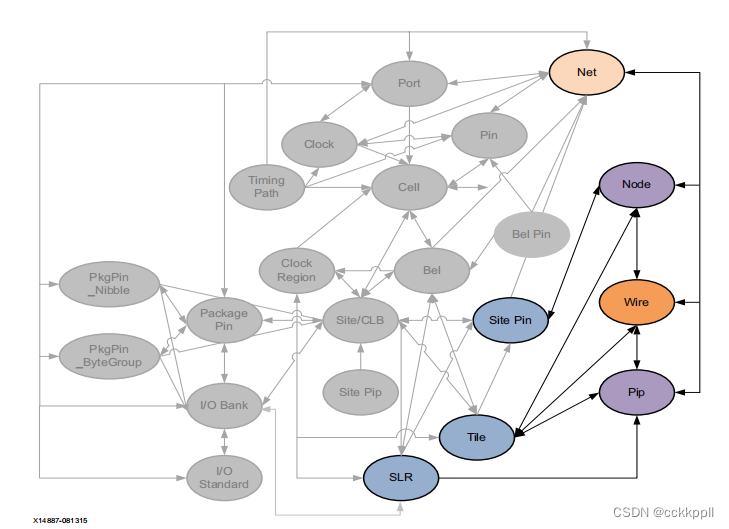

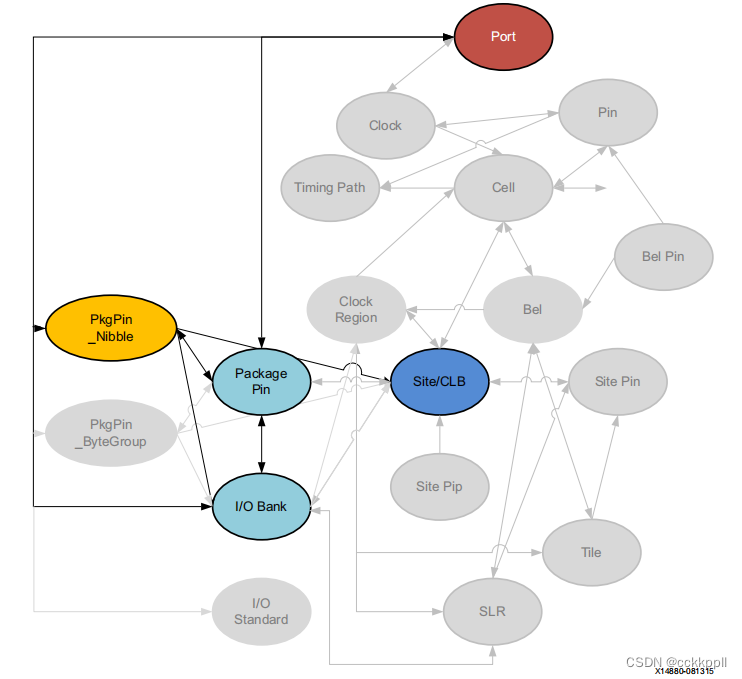

相关对象

PKGPIN_BYTEGROUP和PKGPIN_NIBBLE与IO_BANK、PACKAGE_PIN和

PORT,如前所述。此外,每个PKGPIN_NIBBLE都与

Xilinx设备。您可以使用Tcl查询关联对象的PKGPIN_NIBBLE

命令如下:

get_pkgpin_nibbles-of[get_iobanks 45]

您还可以获得分配给特定pkgpin_nibbles的package_pin对象的列表:

get_package_pins-共[get_pkgpin_nibbles BANK45_BYTE2_L]

属性

pkgpin_nibble对象上的属性如下所示,其中包含示例值:

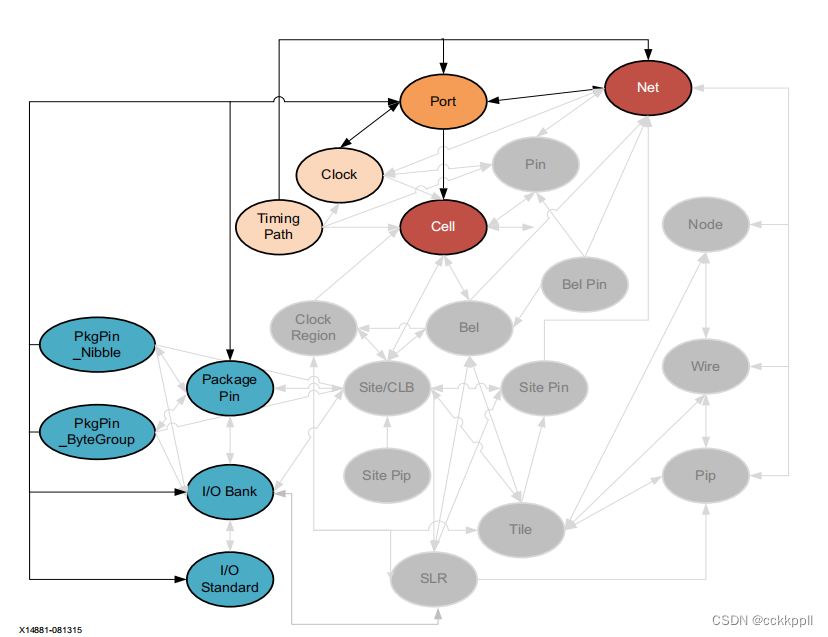

端口是一种特殊类型的分层引脚,在

分层设计的顶层,或分层单元中的内部连接点,或

块模块,用于将内部逻辑连接到分层单元上的引脚。端口可以是

标量,包含单个连接,或者可以是对多个信号进行分组的总线端口

在一起

相关对象

设计顶层的端口通过

设备包的PACKAGE_PIN,到裸片上的IO_BANK,分配

IOSTANDARDs。

端口还可以将时钟定义从系统或板带到设计中,并且应该

使用set_input_delay或

set_output_delay约束。请参阅Vivado Design Suite用户指南:使用

限制条件(UG903)[参考文献19],了解有关这些限制条件的更多信息。

您可以查询分配给特定package_pins、IO_banks、IO_Standards、sites的端口,

使用Tcl命令的小区、网络、时钟、timing_path或drc_conflications,如下所示:

get_ports-of[get_clocks]

在设计内部,端口通过网络连接到单元,以构建层次结构

网表。您可以查询与端口相关联的对象,如net、timing_path、site、,

io_bank、io_standard、package_pin、pkgpin_bytegroup、pkgpin _nibble,使用以下内容

命令形式:

get_package_pins-of[all_inputs]

属性

在端口对象上找到的属性如下,其中包含示例值:

这篇关于vivado PKGPIN_NIBBLE的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[vivado][IP核]FFT](https://img-blog.csdn.net/20180705090837930?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[vivado][IP核]DDS](https://img-blog.csdn.net/20180705083319195?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[vivado]translate_off\on](/front/images/it_default.gif)

![[vivado]例子中的glbl文件](/front/images/it_default.jpg)

![[ip核][vivado]aurora](https://img-blog.csdn.net/20180626151312133?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[ip核][vivado]Block Menory Gennerator 学习](https://img-blog.csdn.net/20180624220549393?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[ip核][vivado]FIFO 学习](https://img-blog.csdn.net/2018062400334231?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)