本文主要是介绍硬件开发笔记(十七):RK3568底板电路串口、485、usb原理图详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

若该文为原创文章,转载请注明原文出处

本文章博客地址:https://hpzwl.blog.csdn.net/article/details/139589308

红胖子网络科技博文大全:开发技术集合(包含Qt实用技术、树莓派、三维、OpenCV、OpenGL、ffmpeg、OSG、单片机、软硬结合等等)持续更新中…

硬件相关开发

上一篇:《硬件开发笔记(十六):RK3568底板电路mipi摄像头接口原理图分析、mipi摄像头详解》

下一篇:敬请期待…

前言

原理图有一些常用电路。

本篇就将集中常用电路分析完,如uart口,涉及usart串口、rs485、usb口。

串口

串行接口简称串口,也称串行通信接口或串行通讯接口(通常指COM接口),是采用串行通信方式的扩展接口。串行接口(Serial Interface)是指数据一位一位地顺序传送。其特点是通信线路简单,只要一对传输线就可以实现双向通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传送速度较慢。

UART和USART都是串行通信中的重要接口,UART主要用于异步通信,而USART则支持同步和异步通信,具有更高的灵活性和性能。在实际应用中,应根据具体的需求和场景选择合适的接口进行通信。

UART(Universal Asynchronous Receiver/Transmitter)

定义

UART,即通用异步收发传输器,通常被用作计算机或其他设备之间传输数据的接口。它主要完成数据的串行化和并行化转换,使得数据能够在不同的设备之间有效地传输。

工作原理

UART将要传输的数据在串行通信与并行通信之间加以转换。作为把并行输入信号转成串行输出信号的芯片,UART通常被集成于其他通讯接口的连接上。它不是像SPI和I2C这样的通信协议,而是微控制器中独立的物理电路或独立的IC。

特点

UART的一个显著优点是它只使用三根线就可以在设备之间传输数据,包括发送线(TX)、接收线(RX)和地线(GND)。这种简单的连接方式使得UART在许多应用中成为首选的通信方式。

USART(Universal Synchronous/Asynchronous Receiver/Transmitter):

定义

USART,即通用同步/异步串行接收/发送器,是一个全双工通用同步/异步串行收发模块,也是一个高度灵活的串行通信设备。USART在UART的基础上增加了同步通信的功能,使其具有更广泛的应用场景。

工作原理

USART收发模块一般分为三大部分:时钟发生器、数据发送器和接收器。控制寄存器为所有的模块共享。时钟发生器由同步逻辑电路(在同步从模式下由外部时钟输入驱动)和波特率发生器组成。发送器部分由一个单独的写入缓冲器、一个串行移位寄存器、校验位发生器和用于处理不同帧结构的控制逻辑电路构成。接收器是USART模块最复杂的部分,包括时钟和数据接收单元、校验位校验器、控制逻辑、移位寄存器和两级接收缓冲器等。

特点

USART的主要特点包括全双工操作、支持同步和异步通信、独立的高精度波特率发生器、支持多种数据位和停止位配置、硬件支持的奇偶校验位发生和检验、数据溢出检测、帧错误检测等。此外,USART还支持多机通信模式和倍速异步通信模式,使得其在各种复杂的通信环境中都能表现出色。

底板接口电路

默认调试串口

这个使用的常规max232类型的芯片,进行ttl与串口232的电平转换:

- TTL是一种电平,即高电平为2.4V至5V,低电平为0V至0.4V。

- RS232电平分为正负两个极性,其电压范围为±3V至±25V,其中大于0V表示逻辑“0”,小于0V表示逻辑“1”,

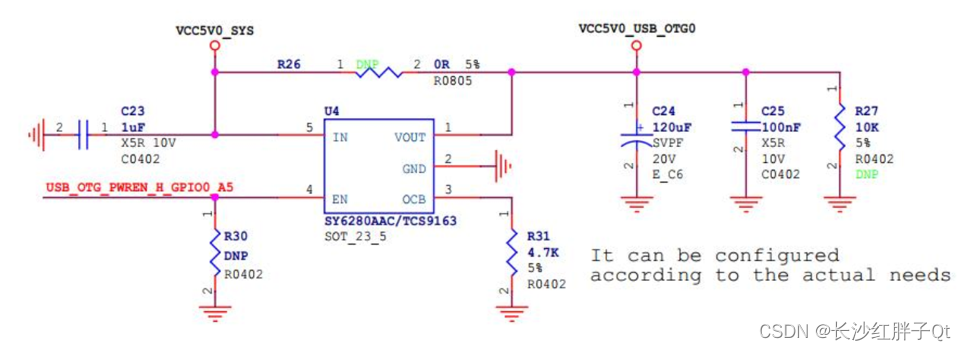

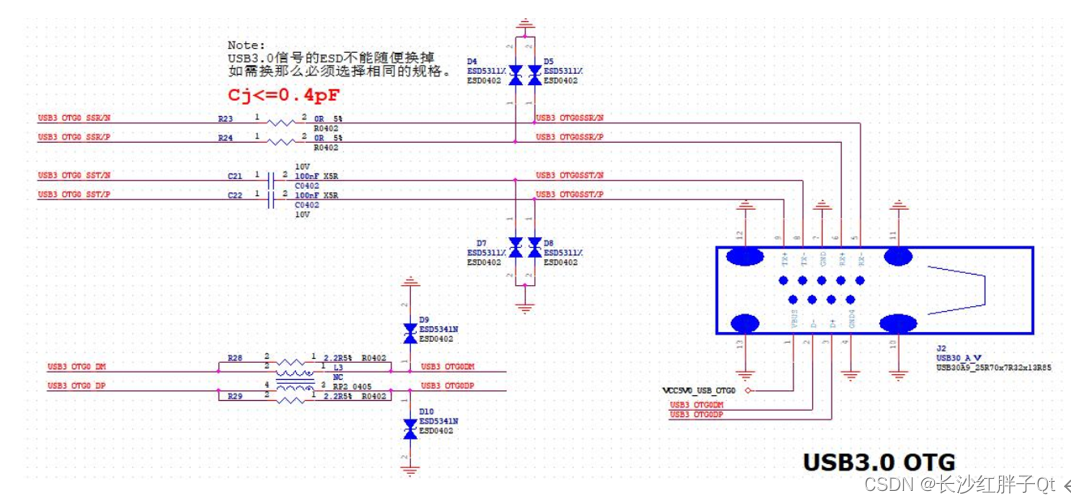

USB3.0 x 2

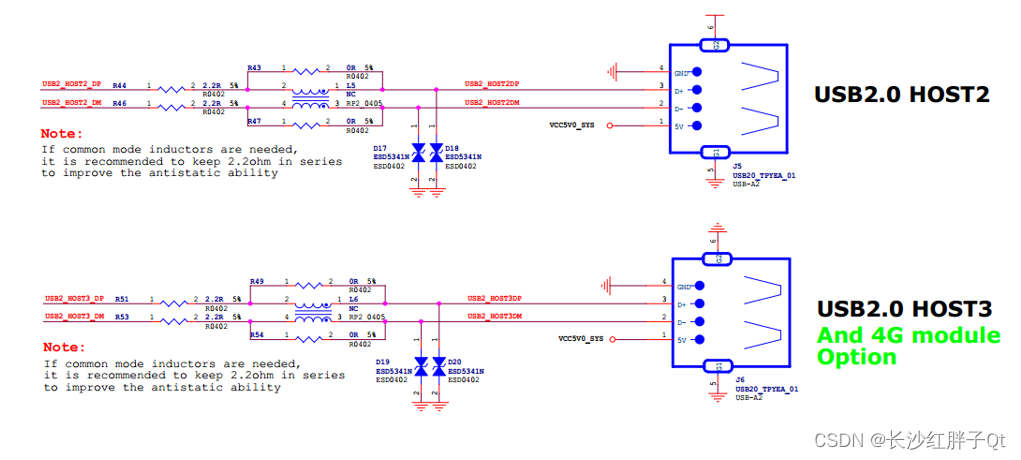

USB2.0 x 2

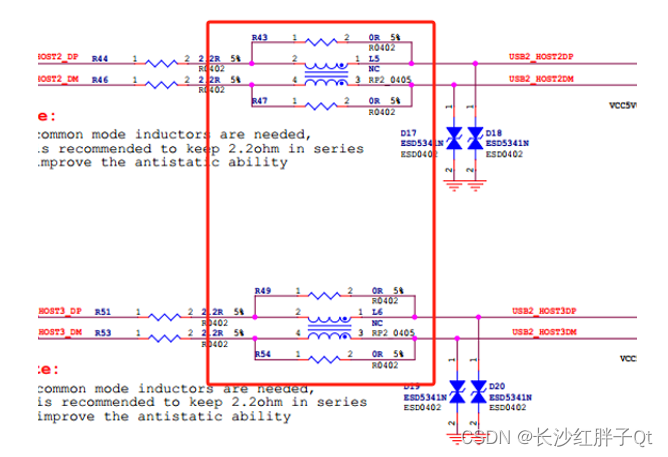

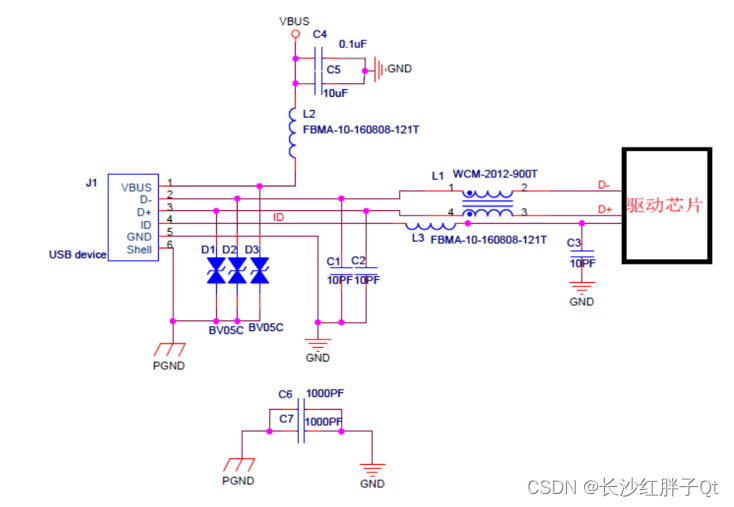

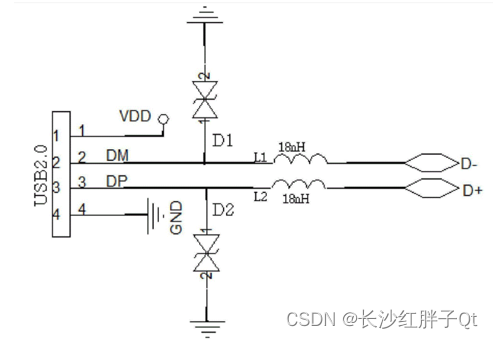

如下图,使用了是USB共模电感电路进行滤波:

USB共模电感电路是一种用于滤除电源信号中的共模噪声的电路(电磁干扰的一种,与电磁兼容性相关)。共模噪声是指同时出现在电源的正极和负极的噪声信号,而差模噪声则仅出现在其中一极的噪声信号。

USB共模电感电路通常由一个共模电感器件和相应的连接电路组成。共模电感器件主要作用是提供一个高阻抗路径,以阻挡共模噪声进入USB设备或从USB设备传播出去。在USB设备的端口两个数据线(D+和D-)上分别加入了一个共模电感器件,从而实现了对共模噪声的滤除。

USB共模电感电路的原理是利用共模电感器件的高阻抗特性,使共模噪声信号无法通过这个电感器件流入或流出USB设备。这样可以有效地减少共模噪声对USB设备的干扰.

需要注意的是,USB共模电感电路只能滤除共模噪声,而无法滤除差模噪声,差模噪声是指只在一个数据线上出现的噪声信号。如果需要同时滤除共模噪声和差模噪声,通常还需要添加其他滤波元件,如差樘电感器件和滤波电容等总而言之,USB共模电,感电路是一种用于滤除电源信号中的共模噪声的电路,通过添加共模电,感器件和相应的连接电路,可以有效地减少共模噪声对USB设备的干扰。

下图随便找的两个示例:

注意:可能是设计习惯或者都可以的状态,这个电路发现有多种形式。

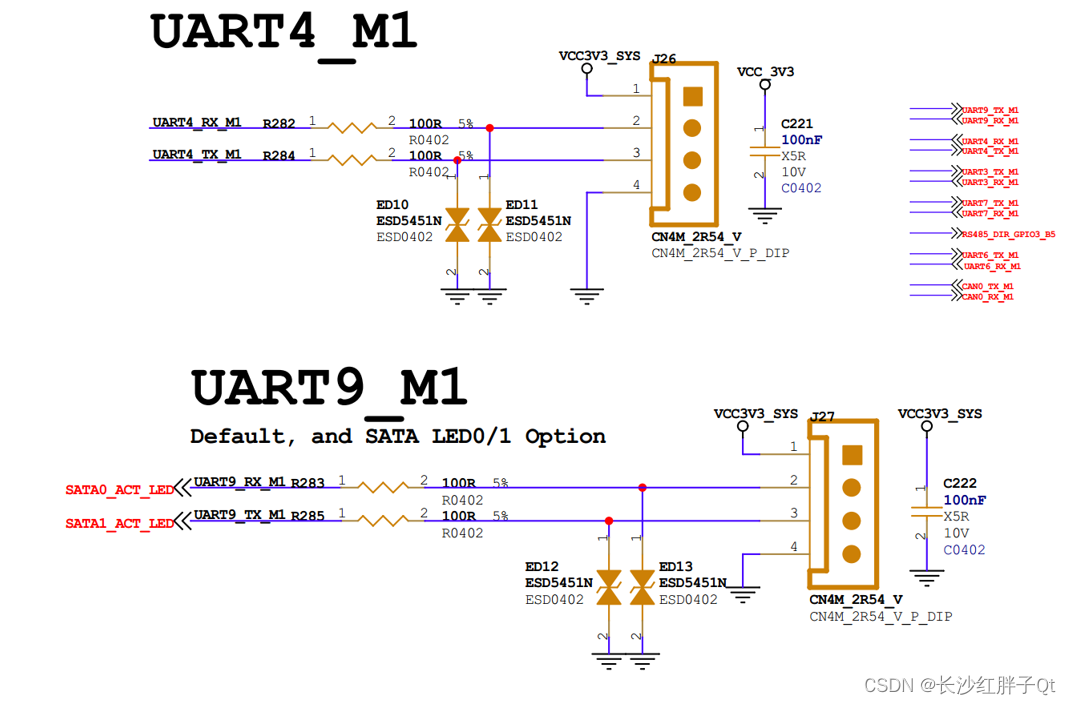

UART x 2

RS485 x 1

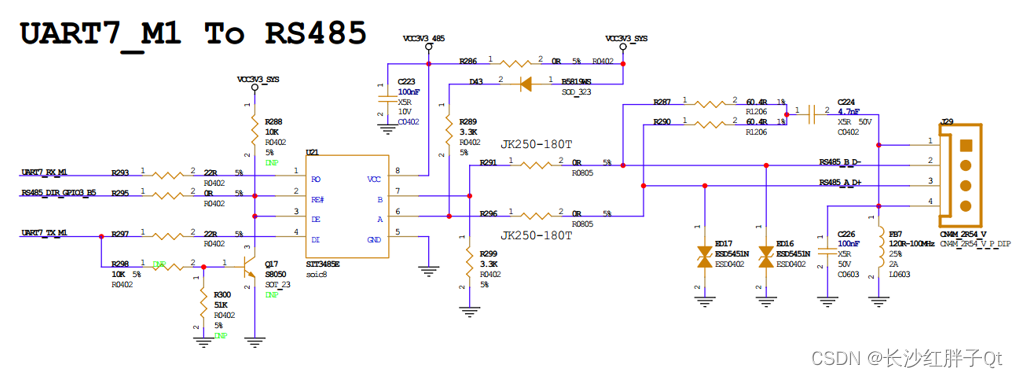

使用了SIT3485E进行串口与485的电平以及逻辑转换,此图没有实现硬件上下拉,是软件控制,这部分可以进行一些调整。

SIT3485E集成芯片

SIT3485E是一款3.0V~5.5V宽电源供电、总线端口ESD水平达到15KVHBM以上、总线耐压范围达到±15V、半双工、低功耗,功能完全满足TIA/EIA-485标准要求的RS-485收发器。

SIT3485E 包括一个驱动器和一个接收器,两者均可独立使能与关闭。当两者均禁用时,驱动器与接收器均输出高阻态。SIT3485E具有1/8负载,允许256个SIT3485E收发器并接在同一通信总线上。可实现高达12Mbps的无差错数据传输。

SIT3485E 工作电压范围为 3.0~5.5 V,具备失效安全(fail-safe)、限流保护、过压保护等功 能。

在使用RS485收发器SIT3485ESA进行485通信时,常用的方式是使用软件控制方向。在空闲状态下,MCU控制485_EN为低电平,使SIT3485ESA处于接收状态;在准备发送数据之前,MCU会拉高485_EN,SIT3485ESA就会处于发送状态,发送完毕之后,485_EN重新处于低电平,SIT3485ESA也再次处于接收状态。

总结

串口、485为常用串行通讯接口,单片机也好,复杂的系统也罢都是离不开这几项的,然后还有USB,本篇完。

上一篇:《硬件开发笔记(十六):RK3568底板电路mipi摄像头接口原理图分析、mipi摄像头详解》

下一篇:敬请期待…

若该文为原创文章,转载请注明原文出处

本文章博客地址:https://hpzwl.blog.csdn.net/article/details/139589308

这篇关于硬件开发笔记(十七):RK3568底板电路串口、485、usb原理图详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!