本文主要是介绍数电实验中设计数字钟所用到的代码详细版(Verilog语言来实现),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、模6计数器的代码:

- 二、模10计数器的代码

- 三、模60计数器的代码

- 四、模24计数器的代码

- 五、显示控制电路模块代码

- 六、1khz和250khz时钟输出实现的代码

- 七、数字钟的实现代码

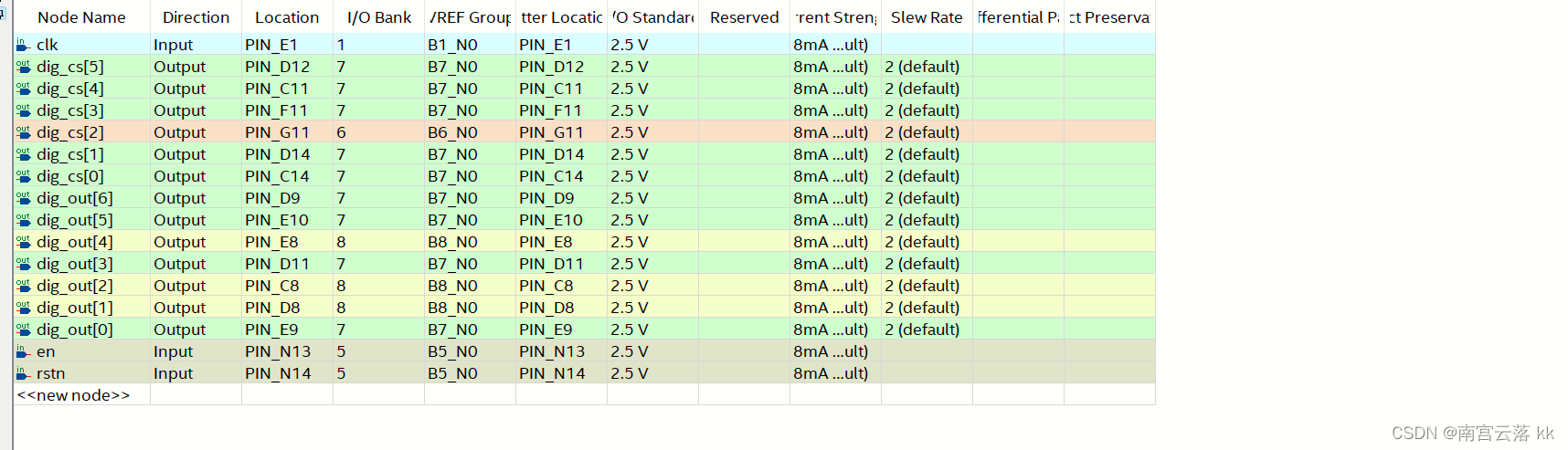

- 八、引脚设置:

- 总结

前言

提示:这里可以添加本文要记录的大概内容:

这里主要展现实现数字钟的重要步骤的代码,有需求者自取。我们利用的是quartus II软件来实现。

一、模6计数器的代码:

module counter6(

input clk,rstn,ce,

output reg[3:0]counter6,

output tc6);assign tc6=(counter6==4'd5);

always @(posedge clk)

beginif(!rstn)counter6 = 4'd0;else if(~ce)counter6<=counter6;else if(counter6>=4'd5)counter6<=4'd0;elsecounter6<=counter6+1'b1;

end

endmodule

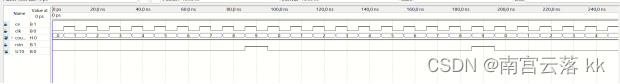

仿真:

二、模10计数器的代码

module counter10(

input clk,rstn,ce,

output reg[3:0]counter10,

output tc10);assign tc10=(counter10==4'd9);

always @(posedge clk)

beginif(!rstn)counter10 = 4'd0;else if(~ce)counter10<=counter10;else if(counter10>=4'd9)counter10<=4'd0;elsecounter10<=counter10+1'b1;

end

endmodule

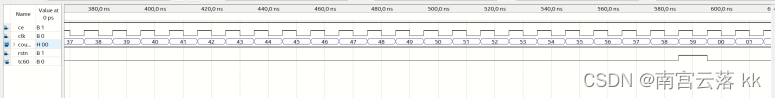

仿真:

三、模60计数器的代码

这里需要调用上面模6和模10模块,故而应该将他们放到同一个工程下。

module counter60(

input clk,rstn,ce,

output [7:0]counter60,

output tc60);

wire tc10,tc6;

wire ce1;

counter6 u1(

.clk(clk),

.rstn(rstn),

.ce(ce1),

.counter6(counter60[7:4]),

.tc6(tc6));counter10 u2(

.clk(clk),

.rstn(rstn),

.ce(ce),

.counter10(counter60[3:0]),

.tc10(tc10));assign ce1=(counter60[3:0]==4'h9)&ce;//29的时候能保持

assign tc60=(tc10&tc6);

endmodule 仿真:

四、模24计数器的代码

这里也需要调用模10和模6的模块,应该将他们放到同一个工程下面

module counter60(

input clk,rstn,ce,

output [7:0]counter60,

output tc60);

wire tc10,tc6;

wire ce1;

counter6 u1(

.clk(clk),

.rstn(rstn),

.ce(ce1),

.counter6(counter60[7:4]),

.tc6(tc6));counter10 u2(

.clk(clk),

.rstn(rstn),

.ce(ce),

.counter10(counter60[3:0]),

.tc10(tc10));assign ce1=(counter60[3:0]==4'h9)&ce;//29的时候能保持

assign tc60=(tc10&tc6);

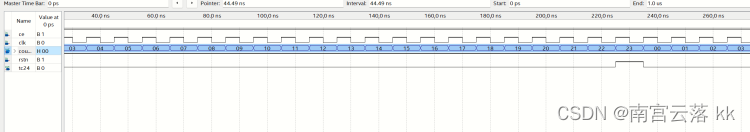

endmodule 仿真:

五、显示控制电路模块代码

module segdis(

input clk,rstn,

input [3:0]dig6,dig5,dig4,dig3,dig2,dig1,

output reg[6:0]dig_out,

output reg[5:0]dig_cs);

always@(posedge clk)

begin

if(!rstn)dig_cs <= 6'b111110;

else dig_cs <= {dig_cs[4:0],dig_cs[5]};

end

reg [3:0]dig_num;

always@(*)begin

case(dig_cs)

6'b111110:dig_num<=dig1;

6'b111101:dig_num<=dig2;

6'b111011:dig_num<=dig3;

6'b110111:dig_num<=dig4;

6'b101111:dig_num<=dig5;

6'b011111:dig_num<=dig6;

default: dig_num<=dig6;

endcase

end

always@(*)begin

case(dig_num)

4'd0:dig_out=7'b111_1110;

4'd1:dig_out=7'b011_0000;

4'd2:dig_out=7'b110_1101;

4'd3:dig_out=7'b111_1001;

4'd4:dig_out=7'b011_0011;

4'd5:dig_out=7'b101_1011;

4'd6:dig_out=7'b001_1111;

4'd7:dig_out=7'b111_0000;

4'd8:dig_out=7'b111_1111;

4'd9:dig_out=7'b111_1011;

default:dig_out=7'b111_1011;

endcase

end

//1 clk dig_cs

// mux dig6-dig1==>dig

//显示译码

endmodule

六、1khz和250khz时钟输出实现的代码

- 1khz:

module clock_div_1hz(

input clk,rstn,

output reg clk1hz);

reg [25:0] cnt1hz;always@(posedge clk)begin

if(~rstn)begin cnt1hz <=26'd0;clk1hz <=1'b1;end

else if(cnt1hz>=26'd24999999)begin cnt1hz <=26'd0;clk1hz <= ~clk1hz;end

else begincnt1hz <=cnt1hz +1'b1;clk1hz <=clk1hz;end

end

endmodule

- 250khz:

module clock_div_1hz(

input clk,rstn,

output reg clk1hz);

reg [25:0] cnt1hz;always@(posedge clk)begin

if(~rstn)begin cnt1hz <=26'd0;clk1hz <=1'b1;end

else if(cnt1hz>=26'd24999999)begin cnt1hz <=26'd0;clk1hz <= ~clk1hz;end

else begincnt1hz <=cnt1hz +1'b1;clk1hz <=clk1hz;end

end

endmodule

七、数字钟的实现代码

这里需要调用前面的模24,模60,显示模块,1KHZ,250KHZ模块一块实现

module top(

input clk,rstn,en,

output [6:0]dig_out,

output [5:0]dig_cs);wire clk1;

wire clk2;

wire [7:0]counter24;

wire [7:0]counter60m;

wire [7:0]counter60s;

wire en1;

wire en2;

wire tc60s;

wire tc60m;

clock_div_250k u1(

.clk(clk),.rstn(rstn),.clk250khz(clk1));counter24 u3(

.clk(clk2),

.rstn(rstn),

.ce(en2),

.counter24(counter24));clock_div_1hz u4(

.clk(clk),

.rstn(rstn),

.clk1hz(clk2));

counter60 u5(.clk(clk2),

.rstn(rstn),

.ce(en1),

.counter60(counter60m),

.tc60(tc60m));

counter60 u6(.clk(clk2),

.rstn(rstn),

.ce(en),

.counter60(counter60s),

.tc60(tc60s));

segdis u2(

.clk(clk1),.rstn(rstn),.dig6(counter24[7:4]),.dig5(counter24[3:0]),.dig4(counter60m[7:4]),.dig3(counter60m[3:0]),

.dig2(counter60s[7:4]),.dig1(counter60s[3:0]),.dig_out(dig_out),.dig_cs(dig_cs));

assign en1=tc60s&en;

assign en2=tc60s&tc60m&en;endmodule

八、引脚设置:

总结

本文主要展现了实现数字钟模块的几步重要代码,有需要者自取。

这篇关于数电实验中设计数字钟所用到的代码详细版(Verilog语言来实现)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!