数字钟专题

数电实验中设计数字钟所用到的代码详细版(Verilog语言来实现)

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、模6计数器的代码:二、模10计数器的代码三、模60计数器的代码四、模24计数器的代码五、显示控制电路模块代码六、1khz和250khz时钟输出实现的代码七、数字钟的实现代码八、引脚设置:总结 前言 提示:这里可以添加本文要记录的大概内容: 这里主要展现实现数字钟的重要步骤的代码,有需求

【FPGA】高云FPGA之数字钟实验->HC595驱动数码管

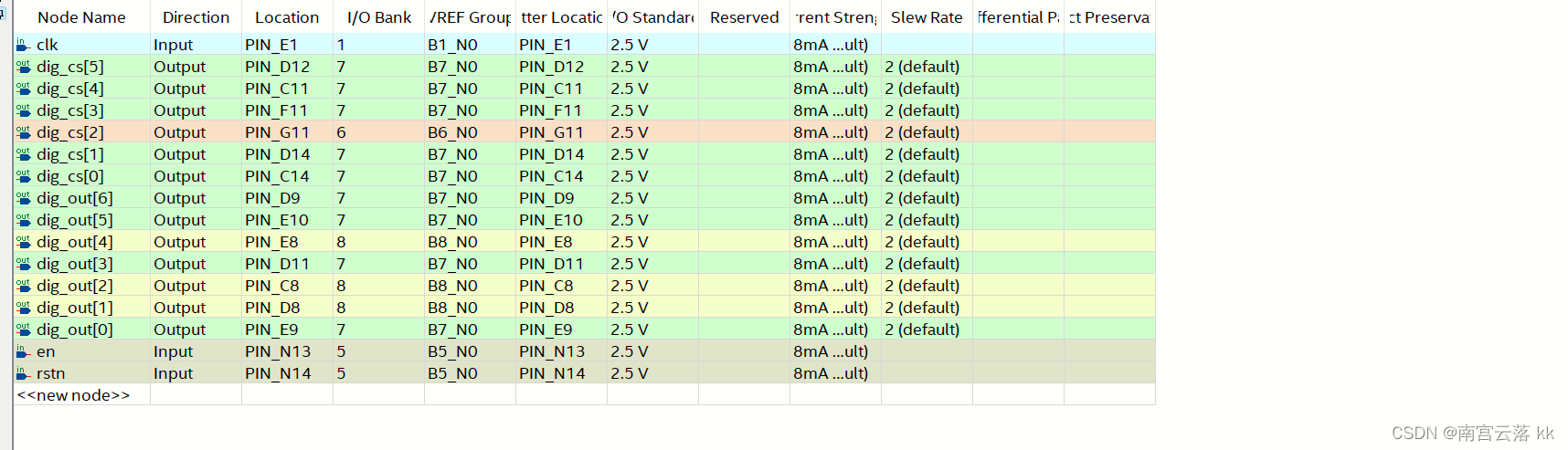

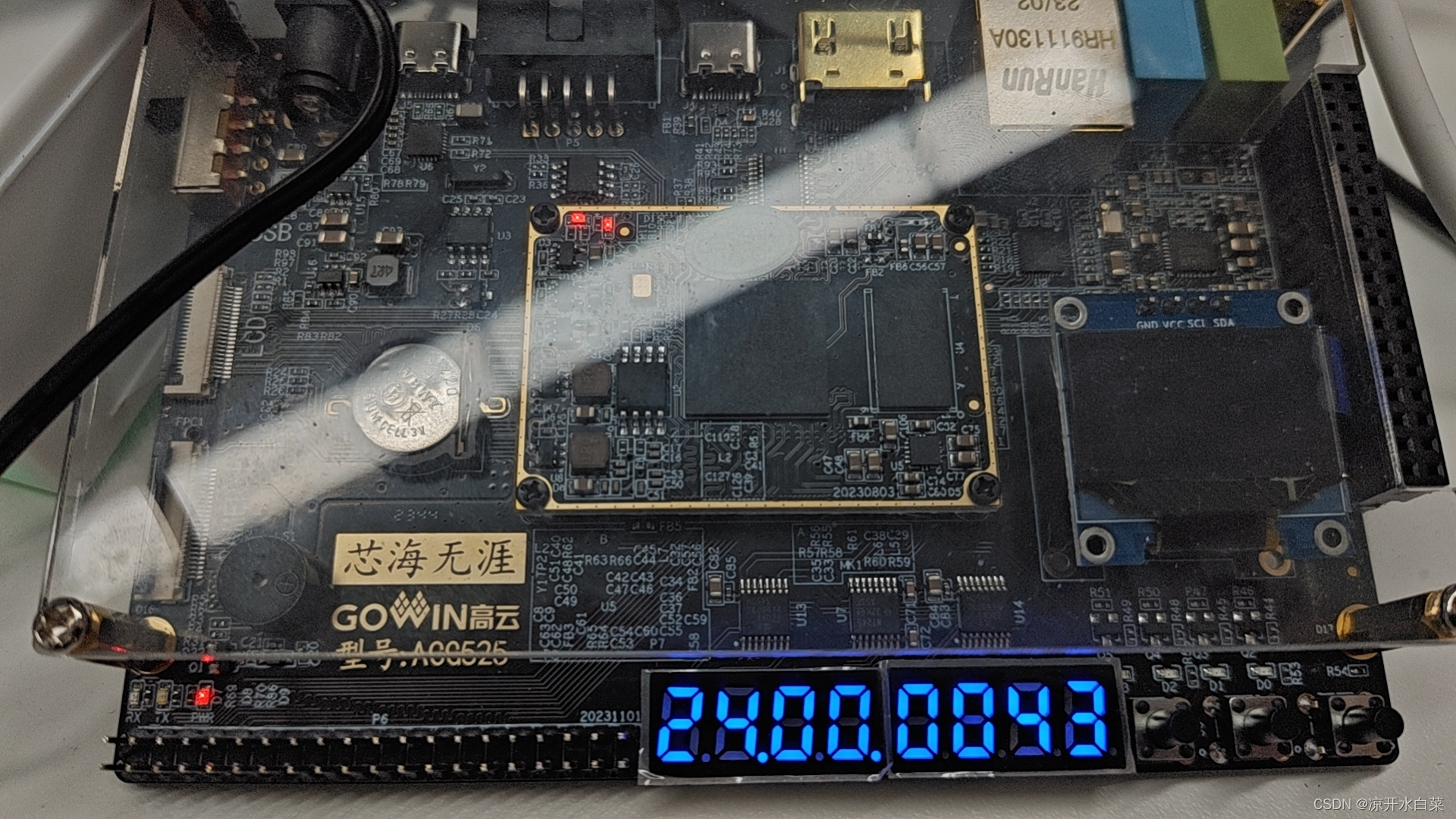

高云FPGA之IP核的使用 1、设计定义2、设计输入2.1 数码管译码显示2.2 74HC595驱动2.3 主模块设计 3、分析和综合4、功能仿真6.1 hex8模块仿真6.2 HC595模块 5、布局布线6、时序仿真7、IO分配以及配置文件(bit流文件)的生成8、配置(烧录)FPGA9、在线调试 1、设计定义 通过74HC595芯片点亮8位数码管,通过计时器实现数码管计时显

FPGA Verilog语言实现数字钟

FPGA第一次练手 仅有基本的计时功能,其他的功能正在赶来 程序如下: module column_scan_module ( CLK, RSTn, Column_Scan_Sig,Row_Scan_Sig ); input CLK; input RSTn; output [5:0]Column_Scan_Sig; output [7:0]Row_Scan_Si

11.7加减计数器,可置位~,数字钟分秒,串转并,串累加转并,24位串并128,流水乘法器,一些乘法器

信号发生器 方波,就是一段时间内都输出相同的信号 锯齿波就是递增 三角波就是先增后减 加减计数器 当mode为1则加,Mode为0则减;只要为0就输出zero 这样会出问题,因为要求是十进制,但是这里并没有考虑到9之后怎么办,所以就会使number输出超过9,应该额外要添加十进制的边缘判断,即mode为1,要加的时候也要判断一下是不是要继续加,而不是直接加

【电路设计】基于8086四位密码锁仿真控制系统-8086双机串行口通信-8086双机通信数据互发仿真-基于8086洗衣机仿真系统设计-8086数码管计算器设计-8086数字钟计时器秒表24小时仿真

基于8086四位密码锁仿真控制系统设计-微机原理1206 密码锁在初始化之后在代码中设置了一个初始密码。当输入密码时,系统会自动判断密码的位数,当密码达到4位的时候自动与初始密码相比对。一旦密码输入正确,则执行开锁程序,即点亮绿色LED灯。如果密码输入错误,则执行闭锁程序,即点亮红色LED灯。 IOY0 EQU 0200H ;8255片选端口始地址M