本文主要是介绍先进工艺的DPT技术,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

“2.5GHz频率 hierarchy DVFS低功耗A72培训”

2.5GHz 12nm 景芯A72 upf DVFS 后端实战训练营!随到随学!

课程采用hierarchy/partition flow,先完成单核A72实战,然后完成A72 TOP实战!训练营简介:

-

Instance:315万

-

Gate count:2600万

-

Frequency: 2.5GHz

-

Power domain:7个,hierarchy UPF设计

-

EDA工具有VCS/Fusion Compiler/VCLP

-

EDA工具有innovus/Starrc/PT/Voltus/formality/LEC/Calibre

-

EDA工具有Redhawk-sc全网首发python版

-

授课形式:视频+文档+上机实践,真实项目flow,一对一答疑!

-

ICer加班太多,项目采用视频模式,随到随学!

景芯A72训练营您将掌握以下知识:

-

掌握hierarchy UPF文件编写,掌握Flatten UPF文件编写、UPF验证。本项目采用hierarchy UPF方式划分了7个power domain、voltage domain。

-

掌握power switch cell,包括SWITCH TRICKLE、SWITCH HAMMER。掌握低功耗cell的用法,选择合适的isolation cell、level shifter等低功耗cell。

-

掌握Power gating,Clock gating设计技术。

-

掌握Multi-VT设计技术,本项目时钟树都是ULVT,动态功耗小,skew小。

-

掌握DVFS技术,ss0p9 2.5GHz、ss0p72 2.0GHz,,其中sram不支持ss0p63。要做ss0p63的话,给sram vddm单独一个0p7v的电源即可。

-

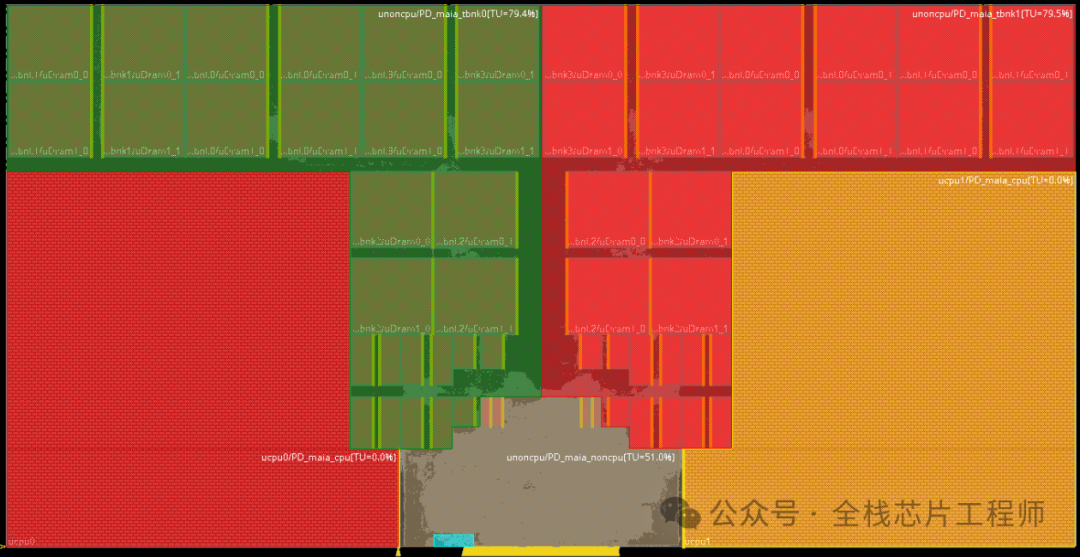

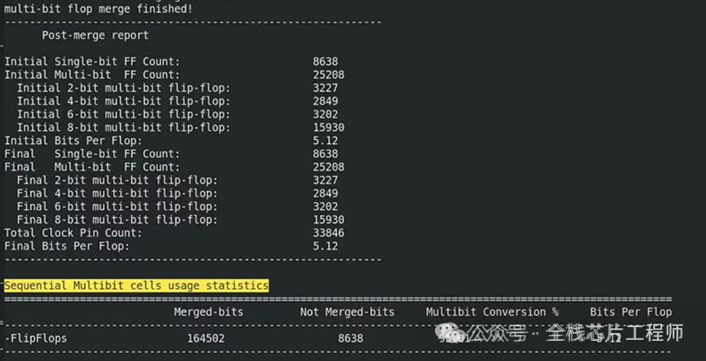

掌握multibit cell的用法,本项目CPU里面的mb高达95%,选择合适的multibit cell得到超高的CPU利用率。INNOVUS里面一般不做mb的merge和split。所以前后一样的,一般综合做multibit的merge split。

-

根据TOP Floorplan DEF进行CPU子系统的partition以及pin assignment。

-

Top的Power stripe的规划及其push down。

-

SpecifyBlackBox,将CPU core镜像partition。

-

手动manual cut the BlackBox的方法,掌握复杂的floorplan设计方法经验。

-

VerifyPowerDomain,检查低功耗划分以及UPF的正确性。

-

Pin assignment,根据timing的需求进行合理的pin脚排布,并解决congestion问题。

-

掌握Timing budget。

-

掌握利用Mixplace实战CPU的自动floorplan,掌握AI的floorplan方法学。

-

掌握Fusion compiler DCG,利用fusion compiler来完成DCG综合,进一步优化timing与congestion。

-

掌握hierarchy ICG的设计方法学,实战关键ICG的设置与否对timing的重大影响。

-

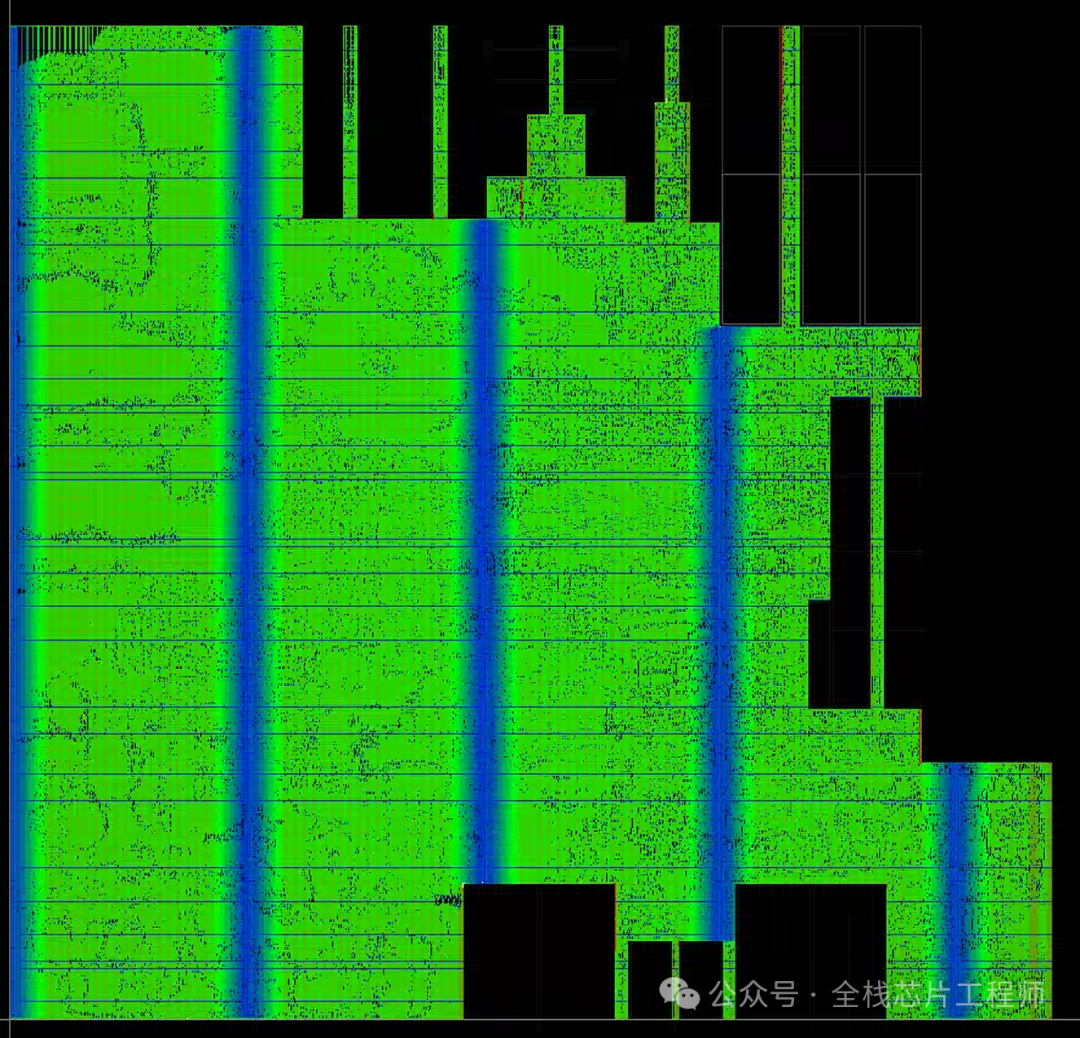

掌握Stapling技术,实战power switch cell的布局和特殊走线的方法学,掌握CPU子系统的powerplan规划及实现,保证CPU子系统和顶层PG的alignment。

-

掌握CPU子系统和TOP的时序接口优化。掌握TOP isolation cell的placement以及isolation cell input电学特性检查。

-

掌握TOP和CPU子系统的clock tree Balance优化处理,common clock path处理。时钟树结构trace和时钟树评价。

-

CPU子系统的DRC/LVS检查

-

TOP系统的DRC/LVS检查

-

Hierarchy & Flatten LVS检查原理及实现方法

-

静态时序分析&IR-Drop

-

DMSA flow

-

根据Foundry的SOD(signoff doc)的Timing signoff标准建立PT环境。

-

Star RC寄生抽取及相关项检查

-

Timing exception分析,包括set_false_path、set_multicyle_path解析。

-

PT timing signoff的Hierarchical和Flatten Timing检查

-

PT和PR timing的差异分析、Dummy insertion和with dummy的Timing分析

-

IR-Drop分析

训练营部分文档:

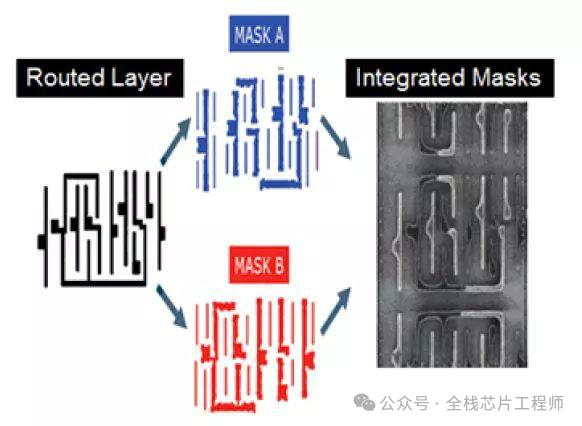

DPT技术,即Double Patterning Technology。这是在20nm以下制程中出现的一种新技术。大家知道,随着芯片工艺尺寸不断减小,每层金属(metal)的间距也变得越来越小,传统的光刻技术已经无法保证设计要求的精确性。为了解决这个问题,我们在刻同一层metal的时候, 用两套掩膜板(mask)加以区别,如下图所示:

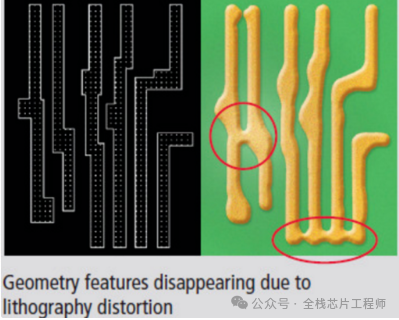

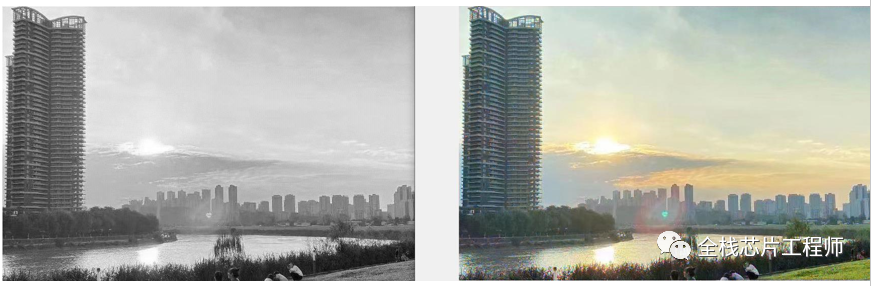

double pattern就是先进工艺下底层金属/poly加工制造的一种技术,先进工艺下DUV光刻机光的波长已经无法直接刻出很小的尺寸(宽度或者间距),会形成如下图所示金属短接的问题。

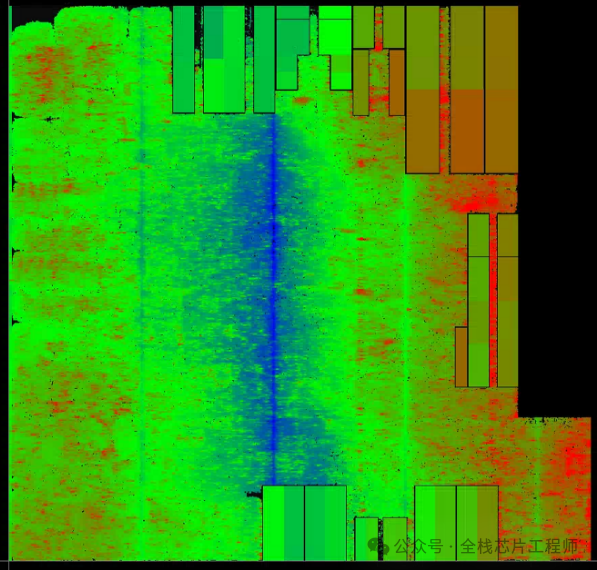

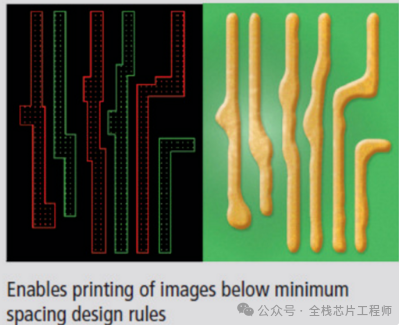

所以可以用两层甚至更多层mask来制造一层金属,如下图所示,所以可以看到版图中有红色和绿色(但看一种颜色,它们的间距光刻是可以加工的)。

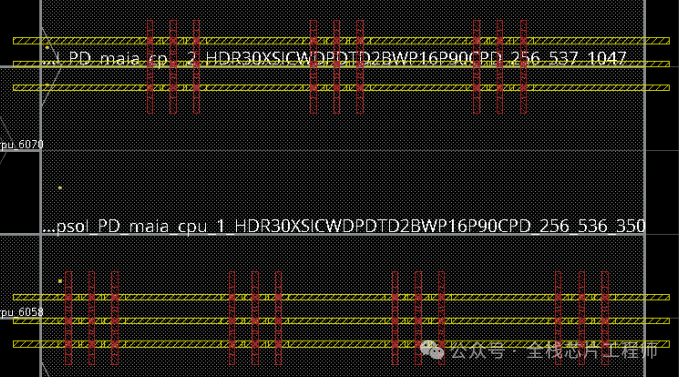

那我们如何给这一 metal 层上的 routing 分配 mask 呢?这要根据 lef 里面SAMEMASK rule 的定义,

–SPACING… SAMEMASK

–SPACING… ENDOFLINE … SAMEMASK …

–SPACINGTABLEPARALLELRUNLENGTH SAMEMASK …

–EOLEXTENSIONSPACING… SAMEMASK …

举个简单的spacing rule例子,如果两条相邻的wire之间的距离小于我们 这里的定义,那说明这两条wire需要分配到不同的掩膜板。

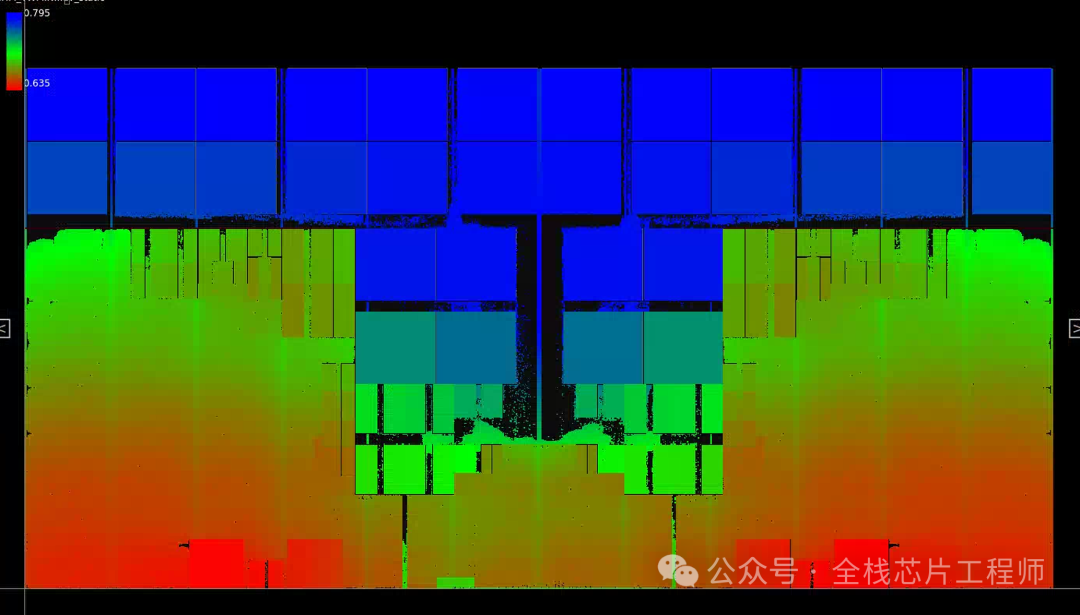

景芯训练营同学问,在M3增加电源的strip后,需要将其连接到M10上,不能通过via连接吗,而是选择stapling?stapling的作用是什么?

答:这里和doublepattern有关,越是先进工艺要求越严格。当然12nm是可以不需要stapling。stapling和viapillar差不多,可以理解为在doublepaterrn下,不可以使用宽metal,那这时,我们的power怎么接?总不能只接一个via吧。invs提供一stapling这种画一小段一小段metal的方法给我们。

以上就是今天分享的内容,如果您和小编一样渴求进步,想掌握芯片设计全流程,欢迎加入小编知识星球,疯狂成长,一起进步!早日成为芯片大佬!

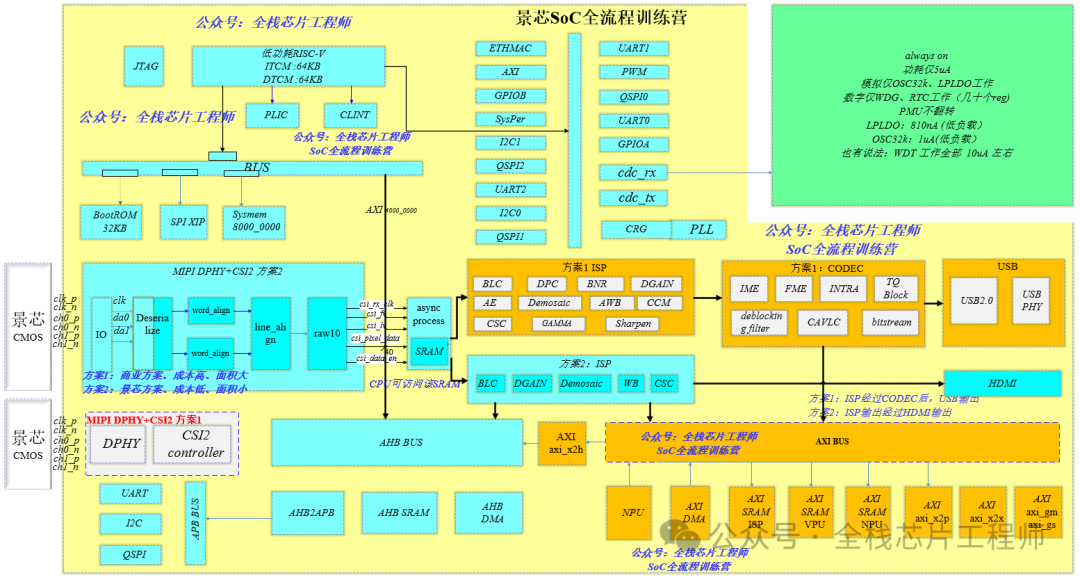

景芯SoC v3.0芯片全流程培训

景芯SoC v3.0重磅升级!手把手教您搭建SoC,从入门到进阶,带您掌握熟悉架构、算法、设计、验证、DFT、后端全流程低功耗!直播视频不定期升级!让您快速超越同龄人!报名微信:13541390811

景芯全流程课程如下:

-

景芯SoC设计 直播视频+文档+实战+一对一辅导(价格不到同行1/6)

-

景芯SoC验证 直播视频+文档+实战+一对一辅导(价格不到同行1/6)

-

景芯SoC中端 直播视频+文档+实战+一对一辅导(价格不到同行1/6)

-

景芯SoC后前 直播视频+文档+实战+一对一辅导(价格不到同行1/6)

进阶课程:

-

12nm 2.5GHz A72 低功耗DVFS实战培训(价格不到同行1/2)

-

DDR4/3项目实战培训(价格不到同行1/2)

芯片Design Service设计服务介绍:

-

提供SoC、MCU、ISP、CIS等芯片设计、验证、DFT设计服务

-

提供DDR/PCIE/MIPI/CAN/USB/ETH/QSPI/UART/I2C等IP设计

-

提供5nm、7nm、12nm、28nm、40nm、55nm、65nm、90nm等后端设计

-

提供高校、企业定制化芯片设计服务、设计培训业务

另外,小编知识星球分享芯片设计、验证、DFT、后端全流程知识以及大量技术文档,欢迎大家加入讨论学习,共同进步!

景芯SoC v3.0芯片全流程实战训练营的宗旨:

手把手教您掌握SoC算法、设计、验证、DFT、后端全流程低功耗!

景芯SoCv3.0,是一款用于【芯片全流程实战培训】的低功耗多媒体SoC!

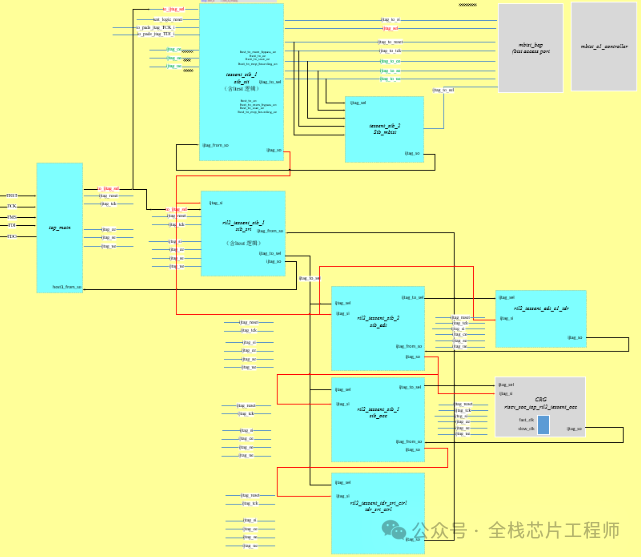

景芯SoC系统分为三个层次的功耗管理,并集成低功耗RISC-V处理器,集成ITCM SRAM、DTCM SRAM,集成MIPI、ISP、USB、QSPI、UART、I2C、GPIO等IP,采用SMIC40工艺流片。

(一)SoC设计课程,您将学会

-

高速接口的Verilog设计实现

-

从图像算法到RTL设计实现

-

MIPI、ISP的Verilog实现与仿真

-

Lint、CDC检查及UVM验证

-

后仿真

仅设计一门课程内容就抵得上其他培训机构的5-6门课程,价格仅其1/6

(二)SoC验证课程,您将学会

-

SoC子系统的UVM环境搭建

-

SoC子系统的UVC环境搭建

-

SoC子系统的VIP环境搭建

-

SoC子系统的DMA SRAM UVM联合验证

-

SoC子系统的UART UVM验证

-

SoC子系统的I2C UVM验证

-

SoC子系统的QSPI UVM验证

-

SoC子系统的C驱动验证(该部分放在设计课程部分)

仅验证一门课程内容就抵得上其他培训机构的3-4门课程,价格仅其1/6

(三)SoC中端课程,您将学会

-

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程,价格仅其1/6

(四)SoC后端课程,您将学会

-

低功耗设计

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程,价格仅其1/6

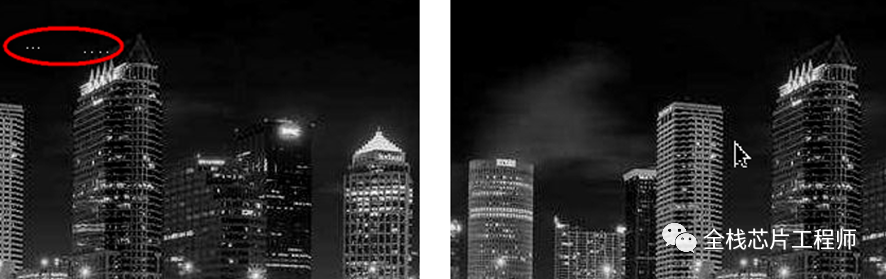

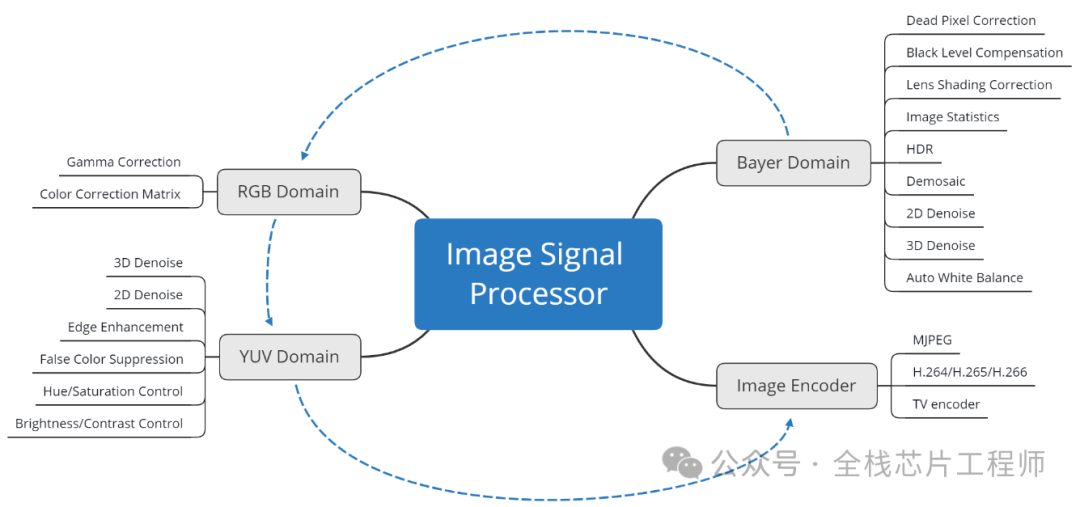

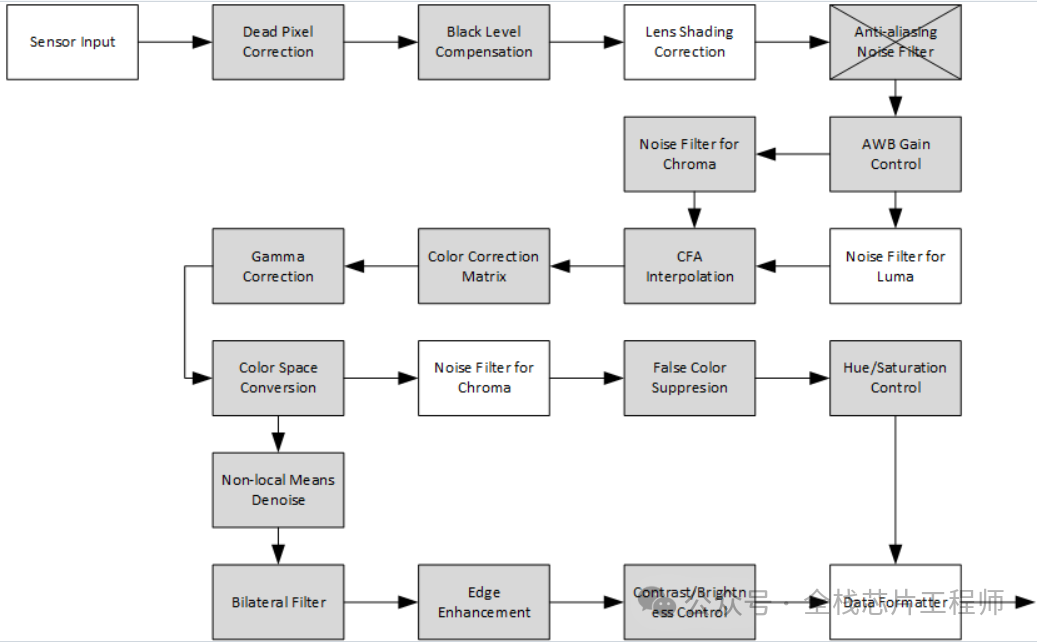

ISP图像处理

-

dpc - 坏点校正

-

blc - 黑电平校正

-

bnr - 拜耳降噪

-

dgain - 数字增益

-

-

demosaic - 去马赛克

-

wb - 白平衡增益

-

ccm - 色彩校正矩阵

-

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

-

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

-

ee - 边缘增强

-

stat_ae - 自动曝光统计

-

stat_awb - 自动白平衡统计

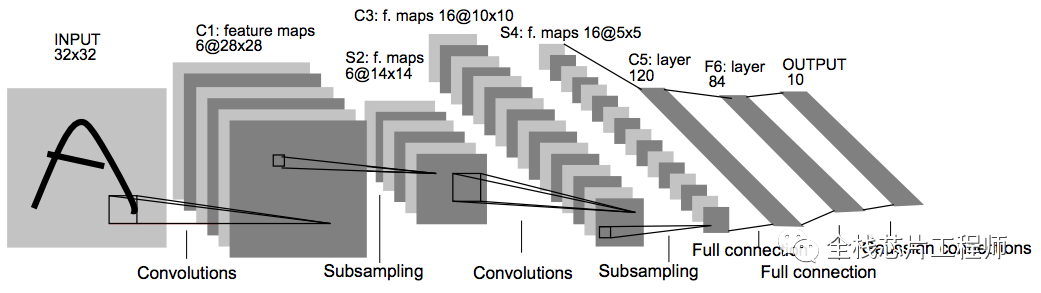

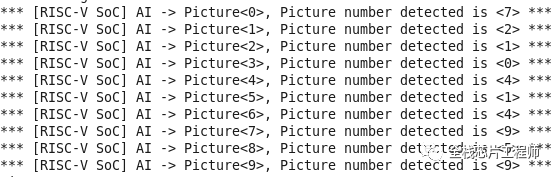

CNN图像识别

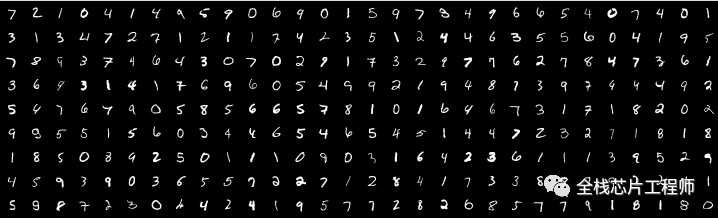

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

景芯SoC 3.0 ISP:

景芯SoC V3.0 DFT方案:

以上就是今天分享的内容,如果您和小编一样渴求进步,想掌握芯片设计全流程,欢迎加入小编知识星球,疯狂成长,一起进步!早日成为芯片大佬!

这篇关于先进工艺的DPT技术的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!