本文主要是介绍Marin说PCB之Max parallel知多少?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

今天是个阳光明媚,万里乌云的好日子。小编我一如既往地到家打开电脑准备看腾讯视频的五十公里桃花坞的第四季,在看到汪苏泷汪台说650电台要解散的时候小编我差点也哭了。650电台之于桃花坞就像乐队的鼓手一样,都是一个团队的灵感啊,而且650电台已经成立四年了,现在说解散就解散是有点太可惜了。

好了,咱们不能感慨太多了,不然就有黑粉说你老是说这些废话,不能直接进入每期文章的主题吗?更有一些性质恶劣的粉丝说你写这些玩意没有人看,狗都不看的,还坚持写这个干嘛呢?

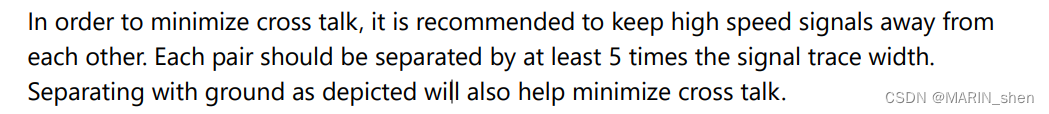

但是小编我就是一个杠精,黑子们不喜欢这个我就继续写,每个人的创作风格不同,不能因为别人一句话就改变了自己的原则了,用董宇辉老师之前就说的话就是一个人强大就是可以做到不以物喜,不以己悲,保持好的心态。当我正在认真看视频时候,手机微信提醒有消息了,我打开一看原来是之前一个老伙计来自某大厂的著名PCB设计攻城狮师陈总,他说有个板子上面的信号速率很高,他们公司的硬件要求他把高速线上平行走线的长度规则加上,他说自己很多年没有搞这个了都忘记了,问我还知道怎么设置不?你还别说我也是忘记的差不多了,我立马打开百度那是一顿哐哐搜索啊,但是都没有关于这个的在allegro中把高速线上平行走线的长度规则加上这个解释和操作。其实我们在做板子的时候经常会遇到有些芯片手册会提供这组BUS信号的间距要求,如下所示:

是不是我们按照这个手册上重要信号线间距要求来做就一定是万事大吉了呢?结果是否定的,我们不仅仅要考虑这个间距的问题,还要考虑同层布线的平行走线的长度耦合问题。因为大家都知道相同间距下,相邻层间耦合带来影响比同层间耦合更严重,所以说大家往往是只考虑了相邻上下层面的串扰问题,忽略了同层走线的平行走线长度过长带来的串扰问题,虽然说相邻层间耦合带来影响比同层间耦合更严重,但是也不是说同层的走线耦合问题就不用看了。

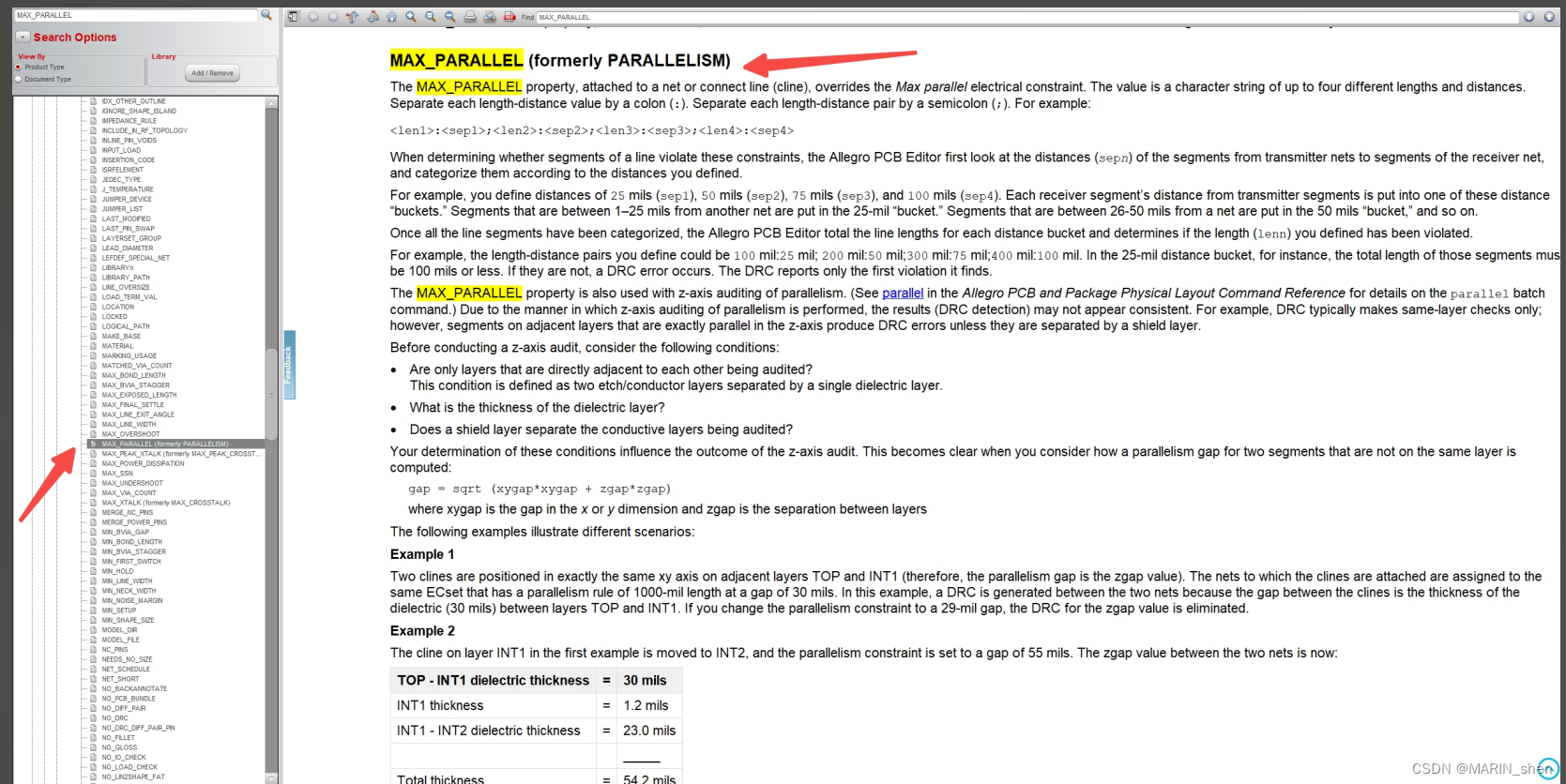

正当我感慨度娘也不是啥都可以查到的时候,我突然想起来之前的乌克兰仿真同事的一句话,你要是对软件中哪个命令不熟悉就打开这个软件的Help命令,这个上面会有详细的解释的,我灵机一动果然按照这个想法成功地找到了这个在allegro中把高速线上平行走线的长度规则设置的解释和操作了,接下来小编我就给大家分享一下这个操作命令了。

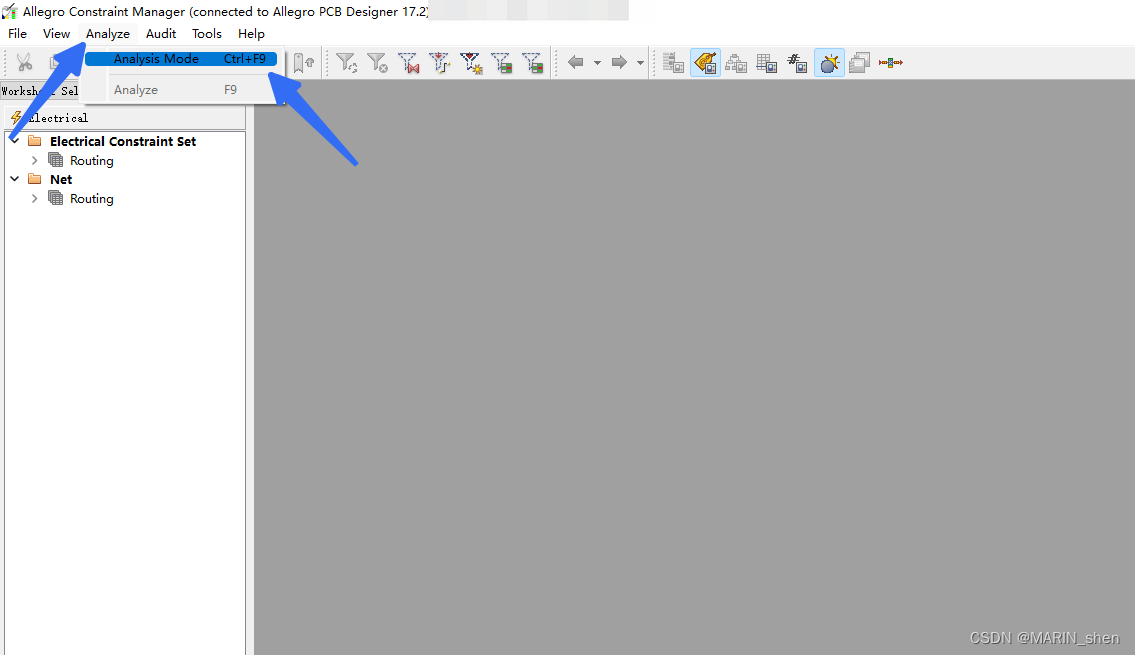

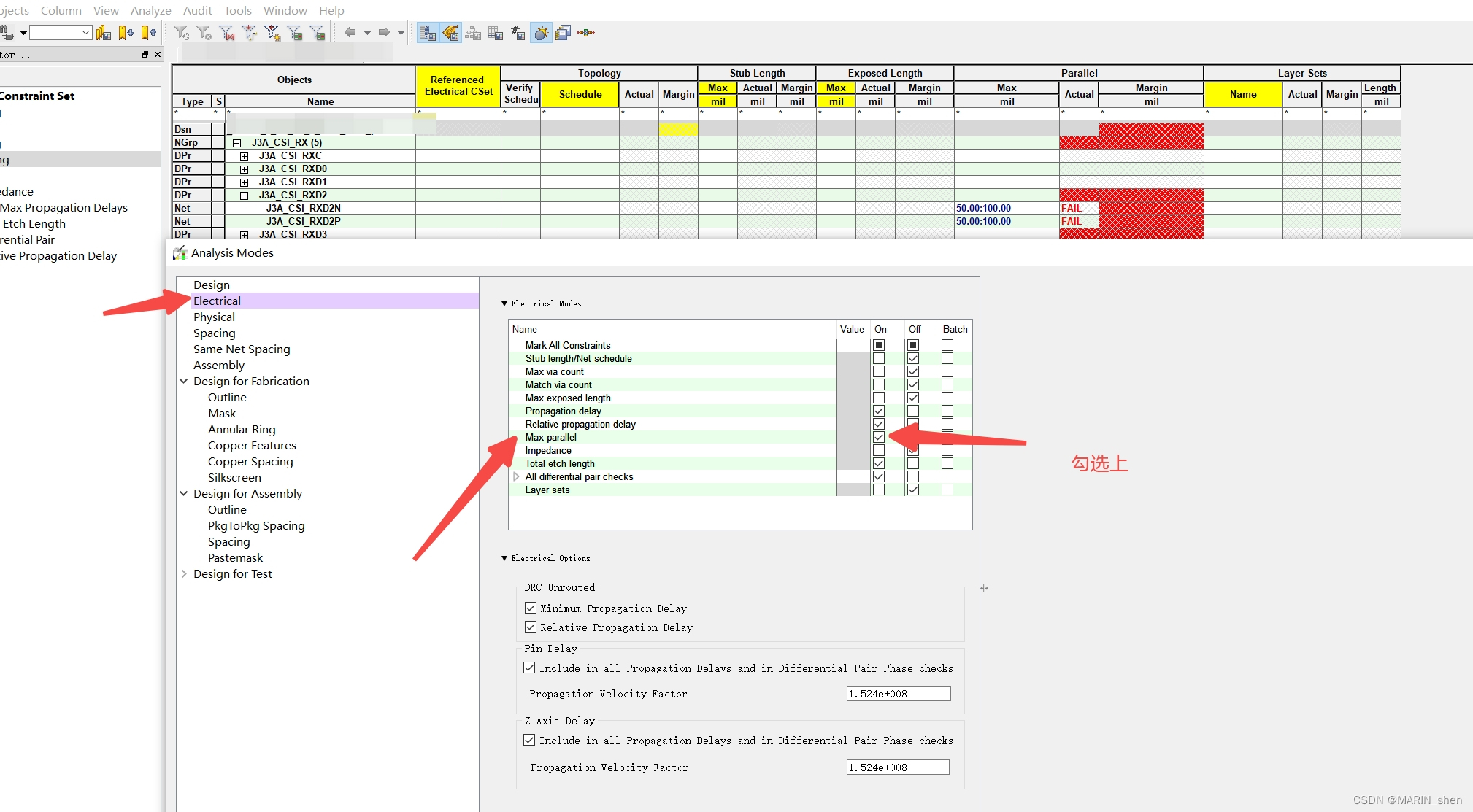

1,首先打开规则管理器界面,操作如下所示:

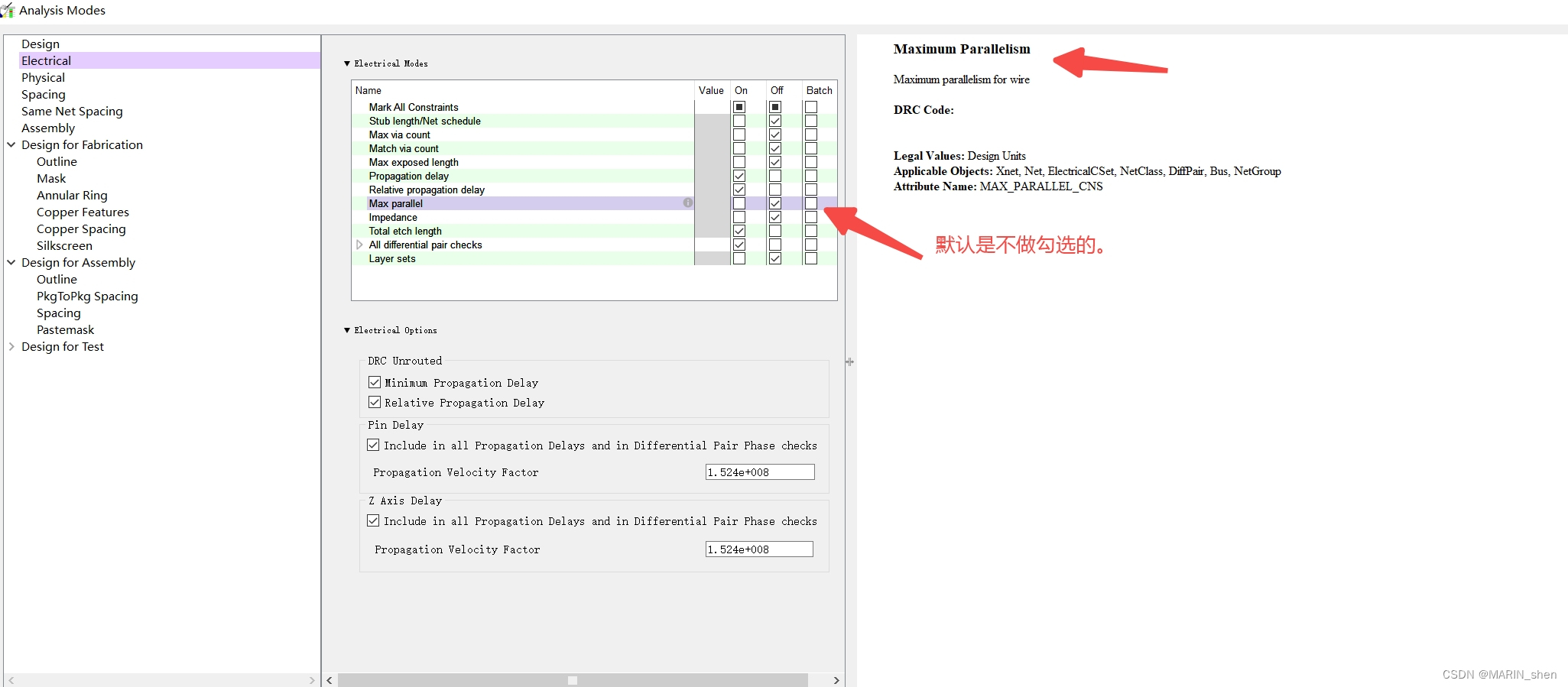

在上面的界面中把max parallel这个记得勾选上。

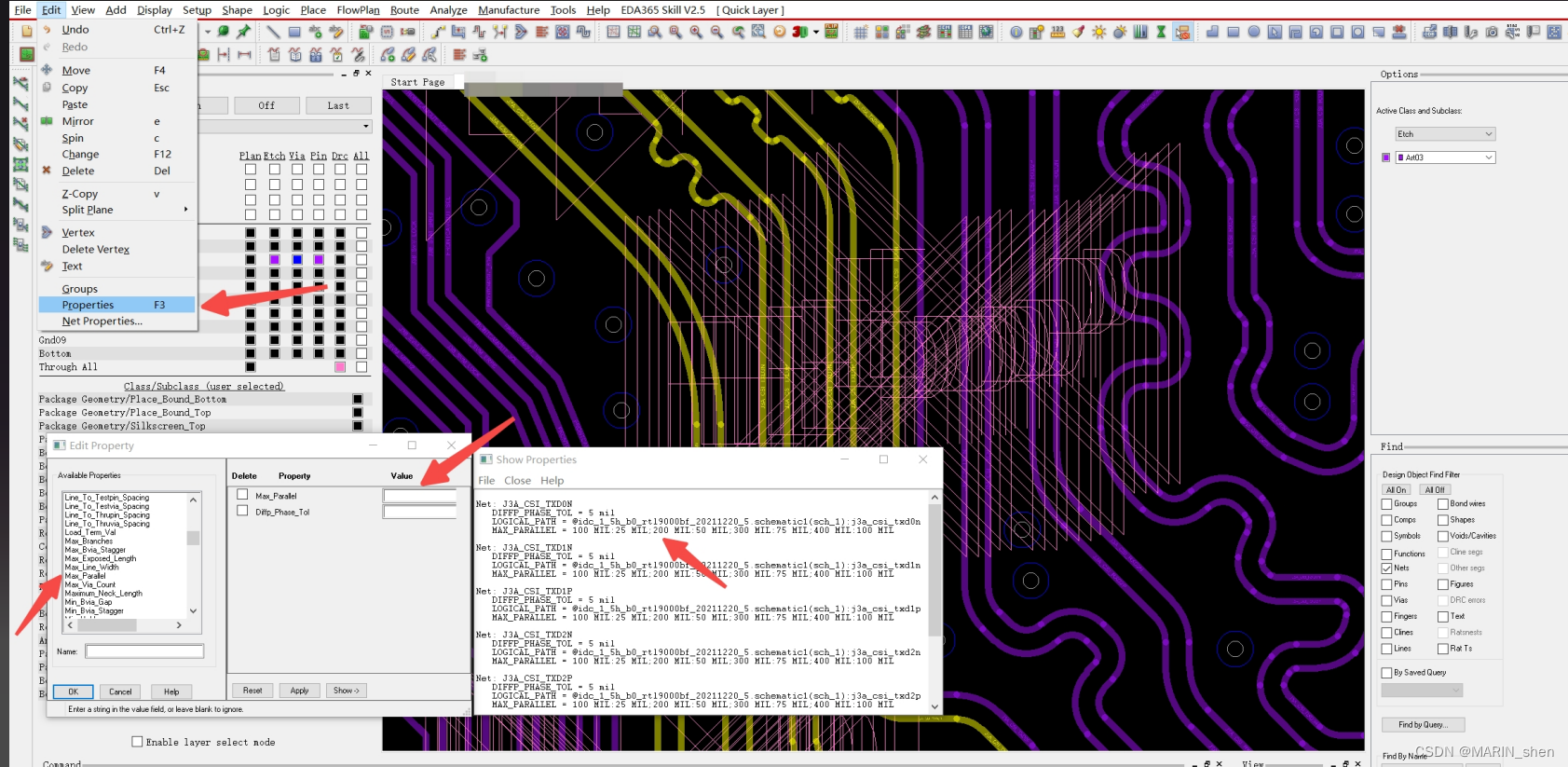

2,在PCB界面中,首先选择Edit---properties(快捷键F3) ,在右边的find栏中勾上NET,接着鼠标左键框选中你所需要设置的网络, 在弹出的属性对话栏中找到---max parallel(平行走线的最大长度)这个设置,按照仿真同事提供的数据把对应的数值填上即可。

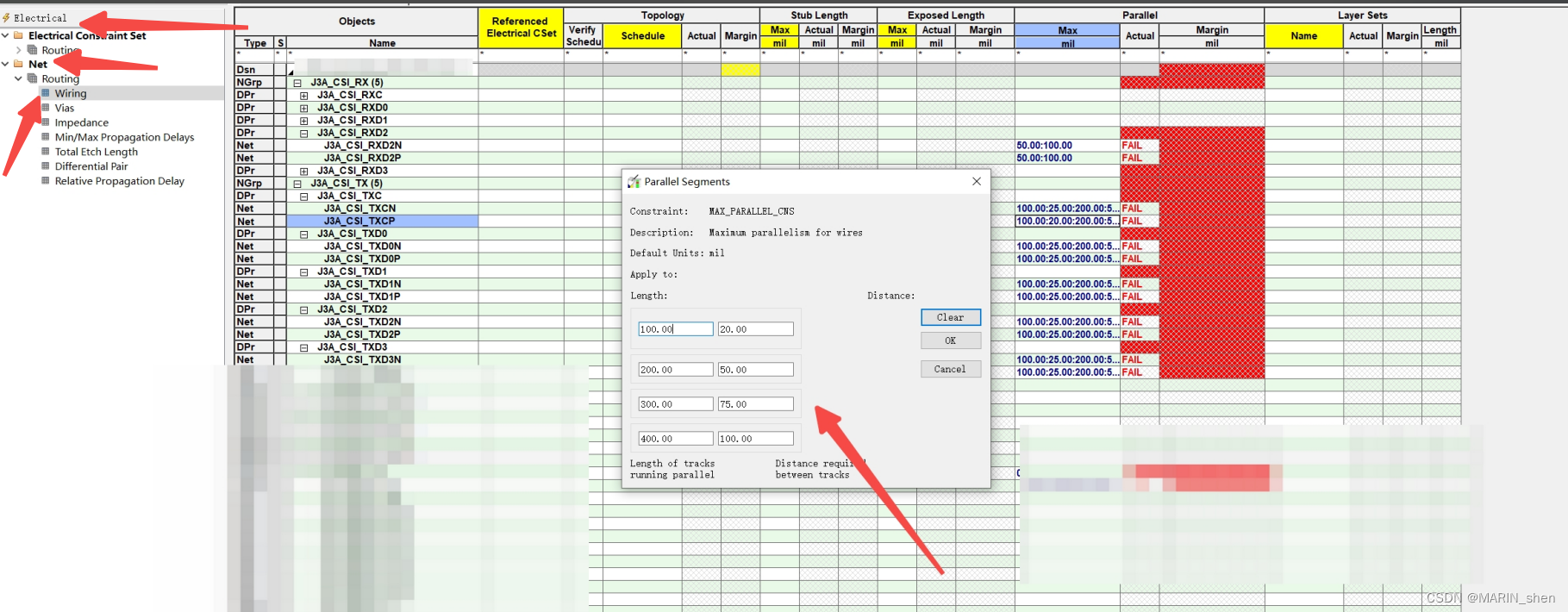

3,或者你也可以在规则管理器中也可以去设置这个属性的,如下所示:

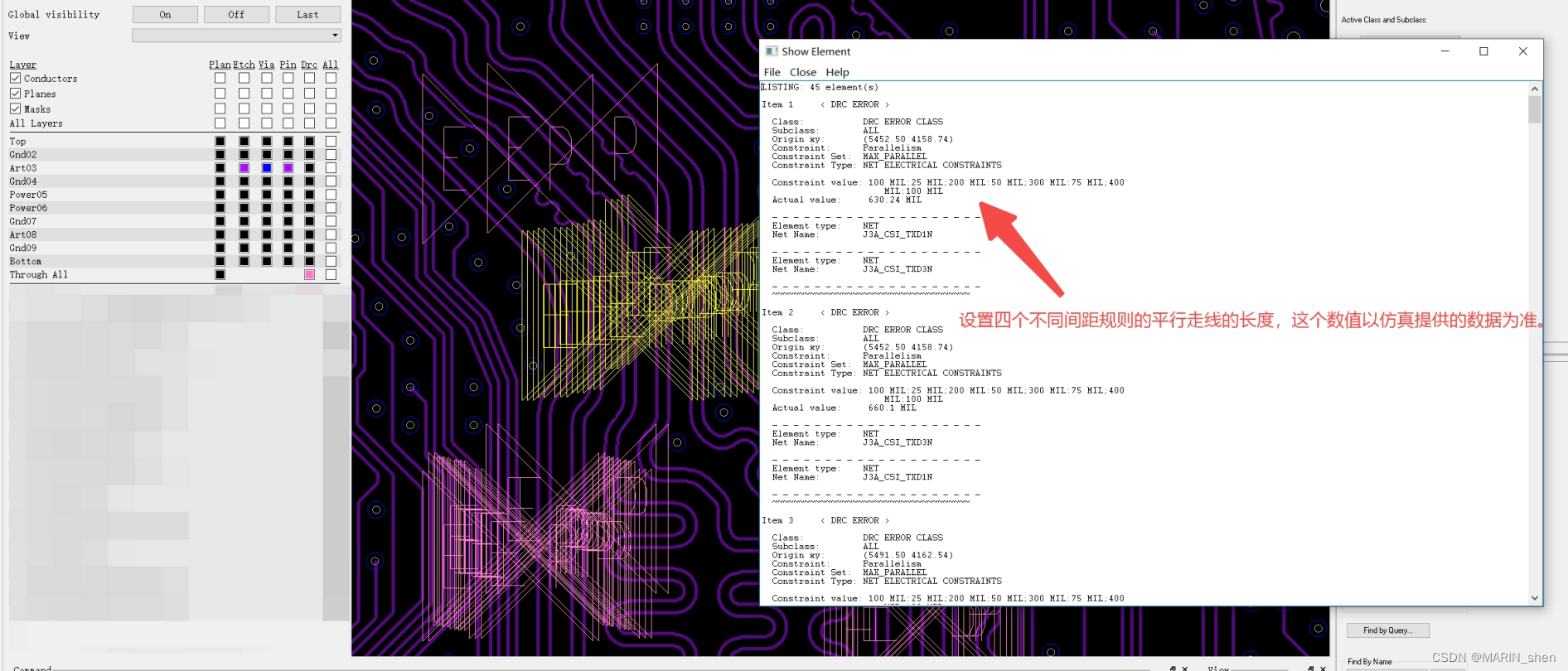

4,以上两种方式设置完成后就可以打开DRC报错去看下单板上高速线平行走线的规则是否满足这要求了,记得要把DRC的ALL打开,不然你就看不到这个报错了。

5,关于这个max parallel平行走线的最大长度)这个设置中数值是什么意思,我再这边给大家说下,例如上面的网络就是设置了max parallel=(100mil:25mil;200:50mil;300mil:75mil;400mil:100mil)意思就是说这个线段被分为四个部分了,第一段走线需要两个行满足间距在25MIL以内,走线长度小于100mil,超过这个设置就会有EP的DRC报错了。当然也有Z方向设置的一些问题,关于这个解释若是帖子们感兴趣的话可以打开规则管理器中的Help文件去搜索一下这个,会有详细的解释的。

大家也都知道走线上的串扰是不可能完全消除的,只能去想办法降低它。通常我们降低单板上信号间的串扰的做法有如下几种设计:

1,使用平面作为返回路径。

2,增加信号路径之间的间距。(一些芯片手册对重要信号的要求,例如3W,5W,5H,7H等)

3,使走线的耦合长度尽量短。(这个就是我们本期主要讲的内容了)

4,在带状线层布线。

5,减少信号走线的阻抗。

6,使用介电常数较低的叠层(这个造成设计的成本也是会增加的,我们在一些降本的方案中谨慎使用)

7,在封装和连接器中不采用公共返回引脚。

8,当两条信号线之间的高度隔离度很重要的时候,可以把它们布线在具有不返回平面的不同层面上。

9,防护布线对于微带线的作用不是很大,对于带状线而言,最好的做法就是在两端和沿线上都使用有短路过孔的防护布线。(走线包GND,包地线上加GND孔)

以上就是本期的所有内容了,我们下期文章不见不散。

这篇关于Marin说PCB之Max parallel知多少?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[LeetCode] 695. Max Area of Island](/front/images/it_default.jpg)