本文主要是介绍飞腾+FPGA多U多串全国产工控主机,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

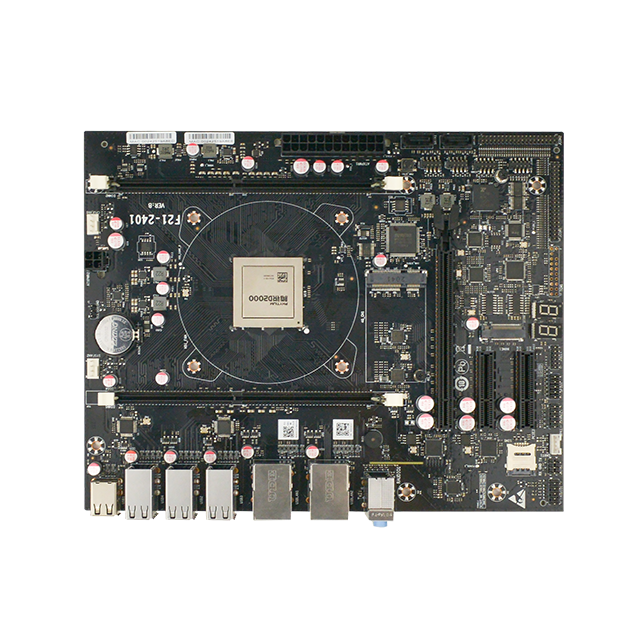

飞腾多U多串工控主机基于国产化飞腾高性能8核D2000处理器平台的国产自主可控解决方案,搭载国产化固件,支持UOS、银河麒麟等国产操作系统,满足金融系统安全运算需求,实现从硬件、操作系统到应用的完全国产、自主、可控,是国产金融信息安全中控机明星解决方案。

产品规格

| 系统配置 |

| 处理器 | 飞腾D2000八核标准版,2.3GHz |

| BIOS | 昆仑固件 |

| 芯片组 | N/A |

| 内存 | 2 x DDR4 UDIMM Slot,最大支持 32G |

| 存 储 |

| SATA | 2 x SATA3.0 |

| M.2 | 1 x M.2 2242/2280 NVME SSD |

| 以太网 |

| 芯片 | 2 x CTC21101C |

| 端口 | 2 x Gbe RJ45 |

| 扩展插槽 |

| PCIe | 1 x PCI-E x16 SLOT 2 x PCI-E x4 SLOT |

| MINI-PCIe | 1 x mini-PCIe SLOT(支持 4G、WiFI/BT) |

| 面板IO |

| USB 2.0 | 14 x USB 2.0 |

| USB3.0 | 4 x USB3.0 |

| 网络 | 2 x Gbe RJ45 |

| Audio | 1 x Line_in, 1 x Line_out, 1 x Mic_in |

| COM | 10 x RS232 |

| 光驱位 | 1 x ODD光驱位 |

| 电源 | 1 x AC 电源接口 |

| 显示 | 外接显卡扩展:1 x VGA(1920*1080@60Hz)1 x HDM(1920*1080@60Hz)1 x DV I (1920*1080@60Hz) |

| 重启按钮 | 1 x 重启开关按键 |

| 电源按钮 | 1 x 电源开关按键 |

| 指示灯 | 1 x POWER,1 x HDD |

| 环 境 |

| 工作温度 | 0℃~40℃ |

| 储存温度 | -20℃~75℃ |

| 电 源 |

| 电源类型 | ATX 300W电源 |

| 输入电压 | AC 100~220V@50-60Hz |

| 物理特性 |

| 产品尺寸 | 270mm(L)* 300mm(W)* 147mm(H) |

这篇关于飞腾+FPGA多U多串全国产工控主机的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!