alu专题

【计算机组成原理】2.2.1_4 算数逻辑单元ALU

2.2.1_4 算数逻辑单元ALU 00:00 各位同学大家好,在这个视频中我们会学习什么是算术逻辑单元ALU。首先我们会介绍ALU在计算机内部的一个作用,以及它需要支持哪些功能。紧接着我们会介绍ALU具体的实现原理,当然这个部分简要了解即可,考试不太可能考它的实现原理。最后我们会教大家怎么看懂ALU的图示。在考研真题当中有可能会给大家一个电路图作为题目的信息,在电路图当中可能会包含ALU这个

【计算机组成原理】二、数据的表示和运算:3.算术逻辑单元ALU(逻辑运算、加法器)

4.运算器ALU 文章目录 4.运算器ALU4.1逻辑运算非(NOT)与(AND)或(OR)异或(XOR)同或(XNOR) 4.2加法器4.2.1一位全加器4.2.2串行加法器4.2.3并行加法器 4.3ALU功能与结构 运算器由 算术逻辑单元ALU和若干 通用寄存器(用于暂存操作数和中间结果),如 累加器ACC, 乘商寄存器MQ, 操作数寄存器X, 变址寄存器IX

[处理器芯片]-5 超标量CPU实现之ALU

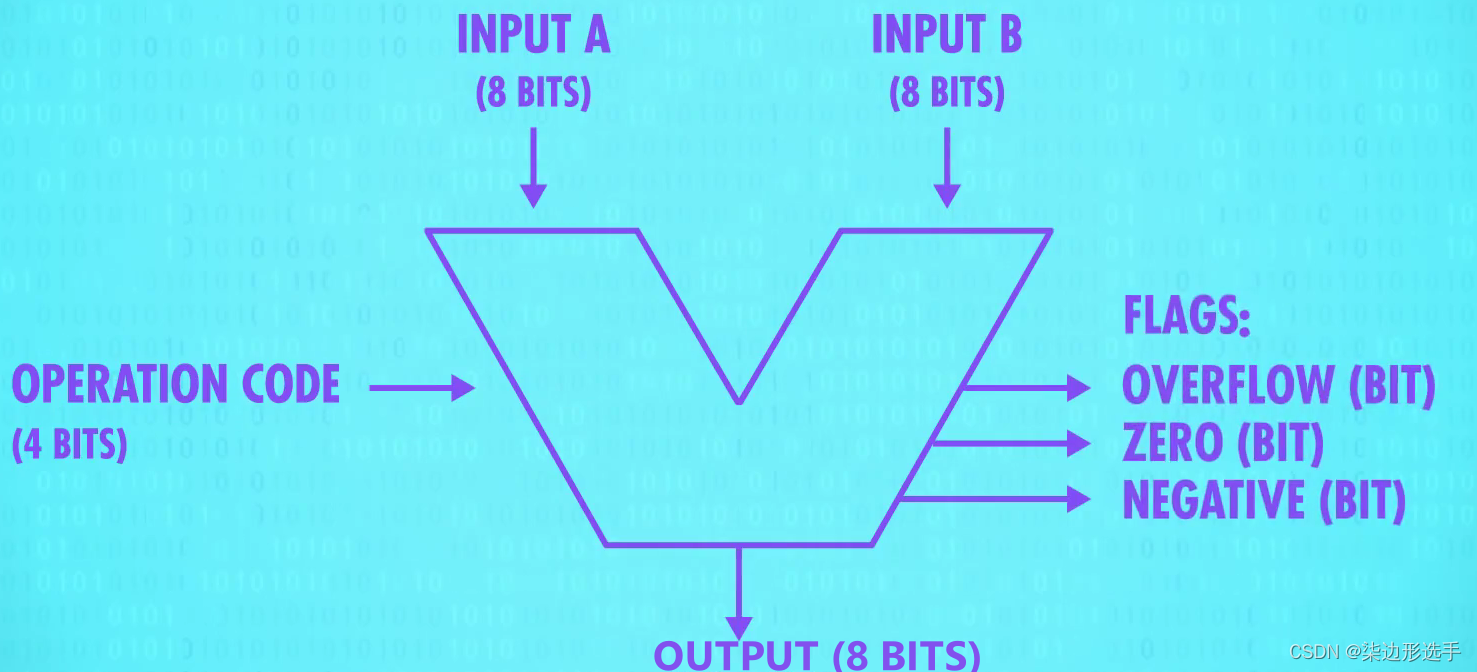

ALU(Arithmetic Logic Unit,算术逻辑单元),是CPU执行单元中最主要的组成部分。 1 主要功能 算术运算:执行加法、减法、乘法和除法等算术运算。 逻辑运算:执行与、或、非、异或等逻辑运算。 移位运算:执行逻辑左移、逻辑右移、算术右移等移位运算。 比较运算:执行大小比较等比较运算。 超标量CPU中的加法器、减法器、乘法器、除法器和移位器在硬件实现中,依赖于组合逻辑

14 - ALU 和半自动加法机

1. ALU A、B 输入 OP=0 加法,OP=1 减法 O 输出,CO 进位输出 2. 半自动加法机 利用 8 位计数器 8CT 改造的 3 位计数器 3CT: 3. 实验工程 【14 - ALU和半自动加法机】

CPU--- ALU算数逻辑运算单元

算术逻辑单元 (Arithmetic Logic Unit, ALU)是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate" 和"Or Gate"构成的算术逻辑单元,主要功能是进行二进制的算术运算,如加减乘(不包括整数除法)。基本上,在所有现代CPU体系结构中,二进制都以二补数的形式来表示。 定义 计算机中执行各种算术和逻辑运算操作的部件 。

CVE-2021-3490:ebpf verifier 寄存器32位范围更新错误导致越界读写【ALU Sanitation 绕过】

文章目录 前言漏洞分析构造 vuln reg 漏洞利用ALU SanitationLinux v5.11.8 – 5.11.16 版本Linux v5.11.8 之前的版本Linux v5.11.16 之后的版本 exp 及效果演示漏洞修复参考 前言 影响版本:Linux 5.7-rc1 ~ Linux 5.13-rc4 编译选项:CONFIG_BPF_SYSCALL,conf

CPU中的算术逻辑单元(ALU)

ALU有2个单元,1个算术单元和1个逻辑单元 算数单元 1 bit加法 半加器 由一个异或门(XOR)和与门(AND)两个逻辑门构成,异或门表示无进位加法(sum),而与门表示进位(carry) 。 全加器 由于存在进位关系,所以从右往左除了第一列不存在进位的加法,之后每一列都存在进位的加法,即从右往左除了第一列只需要处理两个bit,之后的每一列都需要处理三个bi

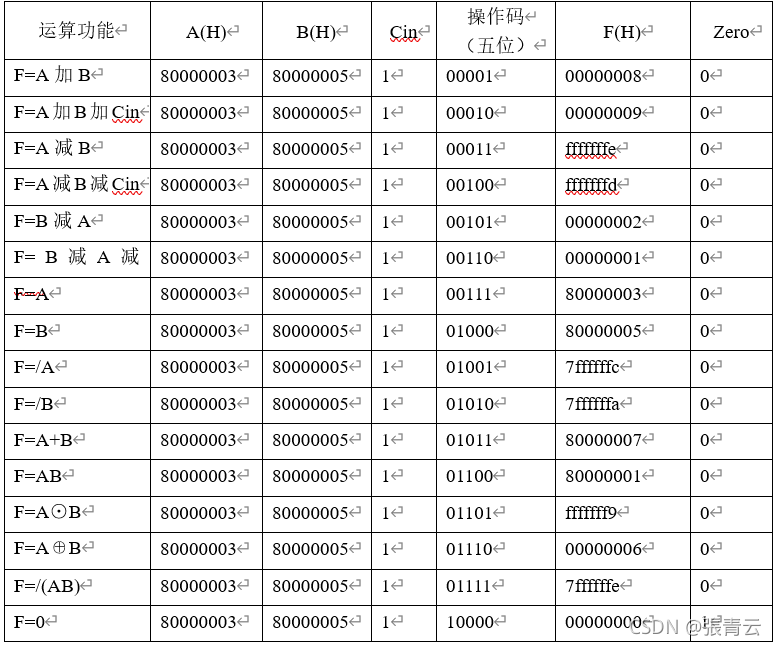

设计并实现一个ALU算数逻辑单元(哈工大计组实验一)

目录 目标设计编码模块接口设计 Verilog代码实现仿真测试仿真代码仿真波形图 目标 使用Verilog硬件编程语言完成一个简单的、具有执行16 种算术逻辑运算操作的电路,要求的16 种操作如下表所示: 设计 编码 对ALU的16种运算的编码如下: 模块接口设计 信号说明如下: • 定义四个输入信号A、B、Cin、Card。其中,A、B 为32 位运算数,Car

计算机组成原理alu功能实现代码_?北京科技大学|871计算机综合一考试大纲

学院简介 1973年,北京钢铁学院成立计算机教研室,1975年设立计算机应用专业,1986年成立计算机系,下设计算机软件工程教研室、计算机应用教研室和计算中心。经过四十余年的建设,2011年计算机与通信工程学院成立,秉承 “厚德博学,求实创新”的优良传统,学院抢抓机遇,加强建设,深化改革,内涵发展,在学科建设、科学研究水平和教育教学质量上实现了跨越式发展与大力提升。 学院设有计算机科学与技术

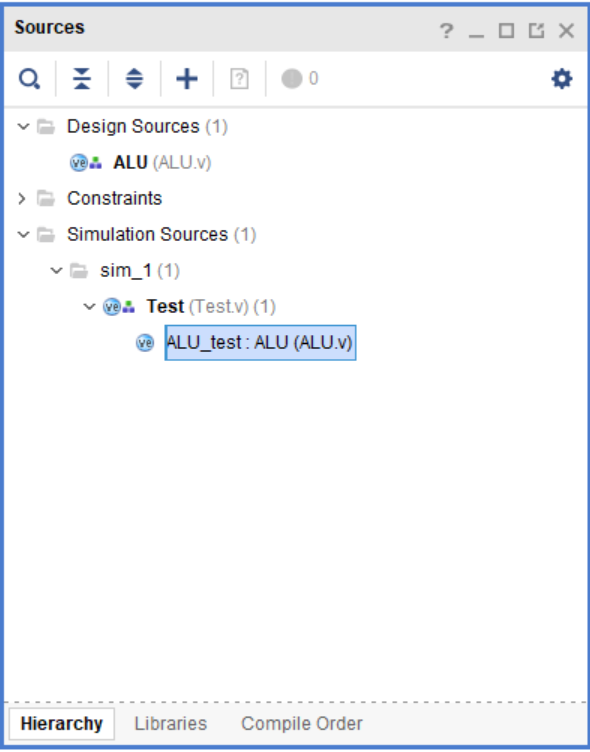

【计算机组成原理实验】ALU设计

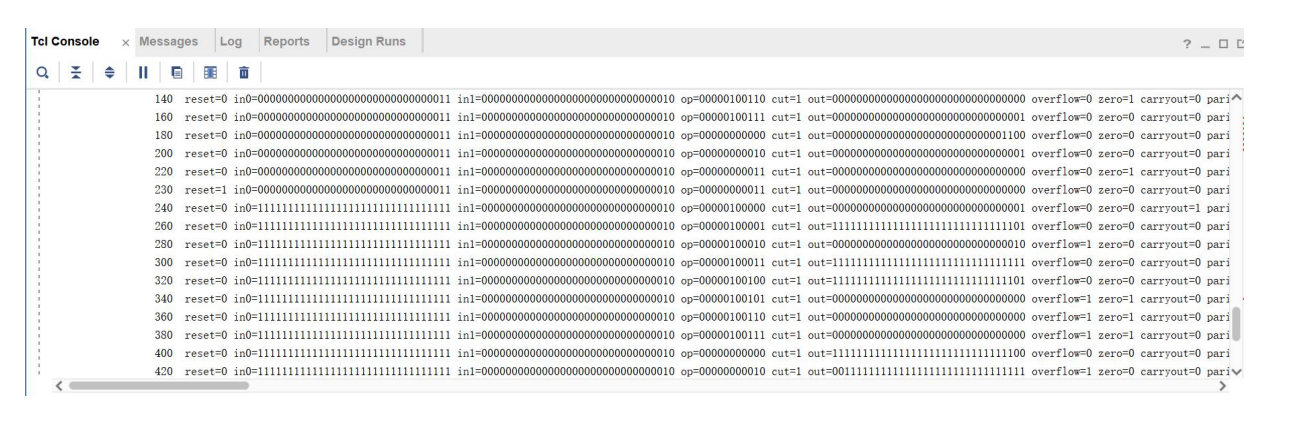

实验内容 设计并实现一个 ALU。 实验环境 ASUS VivoBook + Windows10 + Vivado2019.2,语言为 Verilog HDL。 实验要求 1. 支持至少 8 种运算 2. 输出 5 个标志符号 3. 支持左右移位操作 4. 可支持至少两种舍入操作 实验过程 1. 顶层设计 输入 输出 2. 运算操作 3

【计算机组成原理实验】ALU设计

实验内容 设计并实现一个 ALU。 实验环境 ASUS VivoBook + Windows10 + Vivado2019.2,语言为 Verilog HDL。 实验要求 1. 支持至少 8 种运算 2. 输出 5 个标志符号 3. 支持左右移位操作 4. 可支持至少两种舍入操作 实验过程 1. 顶层设计 输入 输出 2. 运算操作 3

alu电路 计算机组成原理实验,计算机组成原理-实验三-多功能ALU设计实验

实验要求: 本实验要求设计一个具有8种运算功能的32位ALU,并能够产生运算结果的表示:结果为零标志ZF(Zero Flag)、进借位标志位CF()溢出标志OF(Overflow Flag)、符号位标志SF(Sign Flag)和奇偶标志PF(Parity Flag),标志位值解释见代码。ALU通过4根控制线ALU_OP[3:0]来选择其8种功能,功能见表所示,多余的8位用于后继运算的拓展备用。

![[处理器芯片]-5 超标量CPU实现之ALU](/front/images/it_default.jpg)