64b66b专题

基于GTX的64B66B编码IP生成(高速收发器二十)

点击进入高速收发器系列文章导航界面 1、配置GTX IP 相关参数 前文讲解了64B66B编码解码原理,以及GTX IP实现64B66B编解码的相关信号组成,本文生成64B66B编码的GTX IP。 首先如下图所示,需要对GTX共享逻辑进行设置,为了便于扩展,与8B10B编码一致,将共享逻辑放在IP外部的示例工程中。 图1 设置“GT Selection”界面

GTX的64B66B编码(高速收发器十九)

点击进入高速收发器系列文章导航界面 前文讲解了8B10B的原理,8B10B的开销比较大,每传输10位数据,就需要发送2位无效数据。为了减小8B10B编码的开销,同时保留编码方案的优点,提出了64B66B编码。 64B66B编码与8B10B编码方式有本质区别,8B10B编码可以从码表中获取一个数据编码结果,而64B66B在发送前需要通过白噪声对数据加扰,在接收数据时也要先对数据解

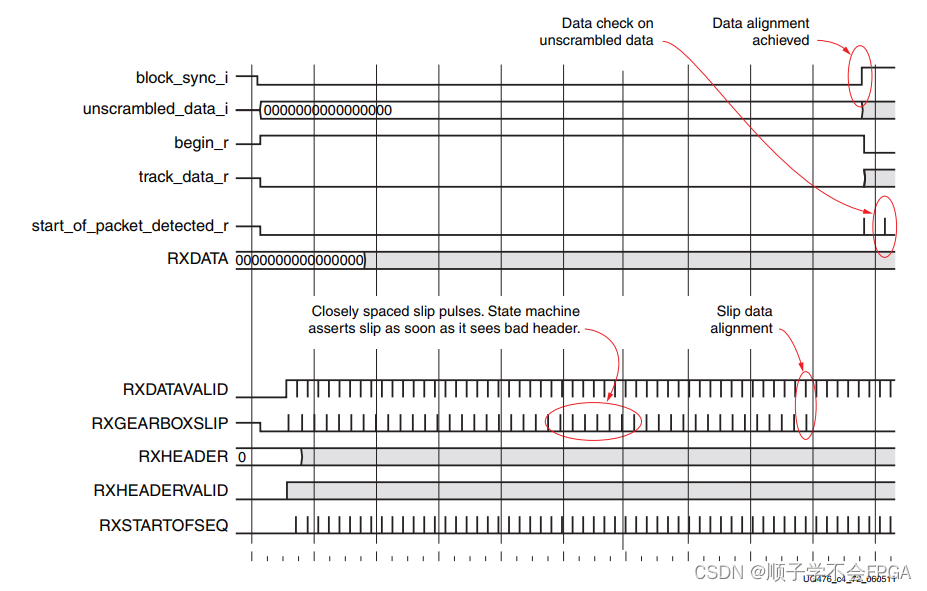

GT收发器64B66B设计(1)IP核配置和example design

文章目录 前言一、IP核配置1.1、编码方式1.2、字节对齐和逗号码 二、example design 前言 在前面我们基于GT收发器进行了PHY层设计,其中采用的编码方式为8B10B,为进一步提高传输效率,从本文开始,将采用基于GT高速收发器采用64B66B编码方式进行设计。 一、IP核配置 1.1、编码方式 前面的配置与8B10B一致,可以看前面的文章介绍。 第三页有

与aurora 64B66B 发送端 AXI4-Stream接口 相连的FIFO设置

目录 1 背景1.1 关于Aurora 64b66b IP核1.2 关于FIFO的读操作模式1.3 遇到的问题 2 与Aurora 64b66b IP核AXI4-S发送接口相连的FIFO的设计 1 背景 1.1 关于Aurora 64b66b IP核 在【PG074】1 简略学习Aurora 64B/66B IP核中2.3.3 Streaming接口章节学习了Aurora 64