本文主要是介绍GT收发器64B66B设计(1)IP核配置和example design,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 前言

- 一、IP核配置

- 1.1、编码方式

- 1.2、字节对齐和逗号码

- 二、example design

前言

在前面我们基于GT收发器进行了PHY层设计,其中采用的编码方式为8B10B,为进一步提高传输效率,从本文开始,将采用基于GT高速收发器采用64B66B编码方式进行设计。

一、IP核配置

1.1、编码方式

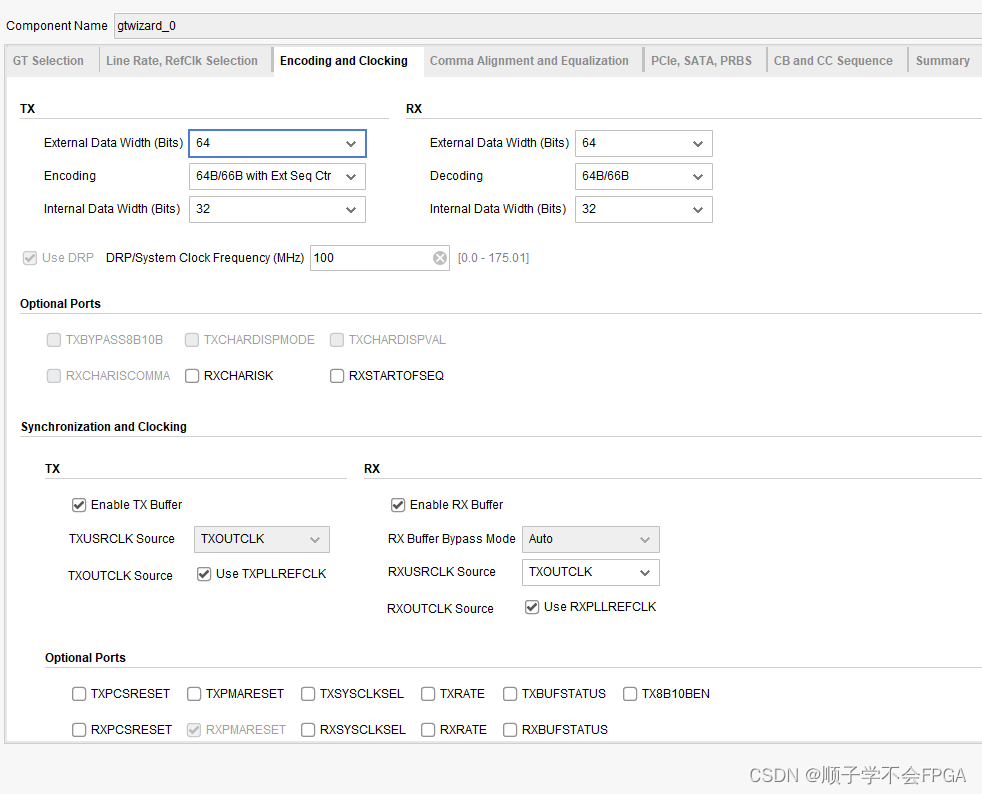

前面的配置与8B10B一致,可以看前面的文章介绍。

第三页有所不同:

数据位宽我们选择64bit,当然32bit也可以。TX端在进行编码选择的时候,64B66B有俩种方式,分别为:

Ext Seq Ctr:数据流经过64B/66B的齿轮箱和混淆器。这里提到了外部序列计数器(External Sequence Counter),这可能是指序列计数器是在设计中实现的,而不是在收发器内部。

Int Seq Ctr:这里提到了GTX收发器,数据流同样经过64B/66B的齿轮箱和混淆器,但序列计数器是在收发器内部实现的。

这里需要先了解Gearbox,也就是齿轮箱是干嘛的,对于64B66B编码而言,数据输入是54bit,输出是2bit,所以这之间存在着2bit的带宽差,Gearbox 就是用来解决这种差异的,实现方式是:将66bit数据拿出来2bit先存入Gearbox,然后输出64bit,当发送32次后,用户这边暂停发送一帧,让Gearbox当中的64bit数据发送,这样就将输入输出带宽差异消除。而这里的计数器就是用来计数发了多少次数据了的。这个计数器可以是在GT内部实现,也可以在用户逻辑里实现,GTH以后就没有内部计数器了,为了减小电路复杂度,这里为了通用我们也选择外部计数器。

文档描述部分:

1.2、字节对齐和逗号码

在64B66B编码当中,我们需要自己去进行字节对齐,所以这里的都没办法选择。

二、example design

在示例工程里我们可以看到比8B10B工程多了三模块,分别是:块同步模块,该模块就是实现字节对齐的功能;和64B66B编码相关的加扰模块以及解扰模块。

这些模块可以直接被我们拿来使用,

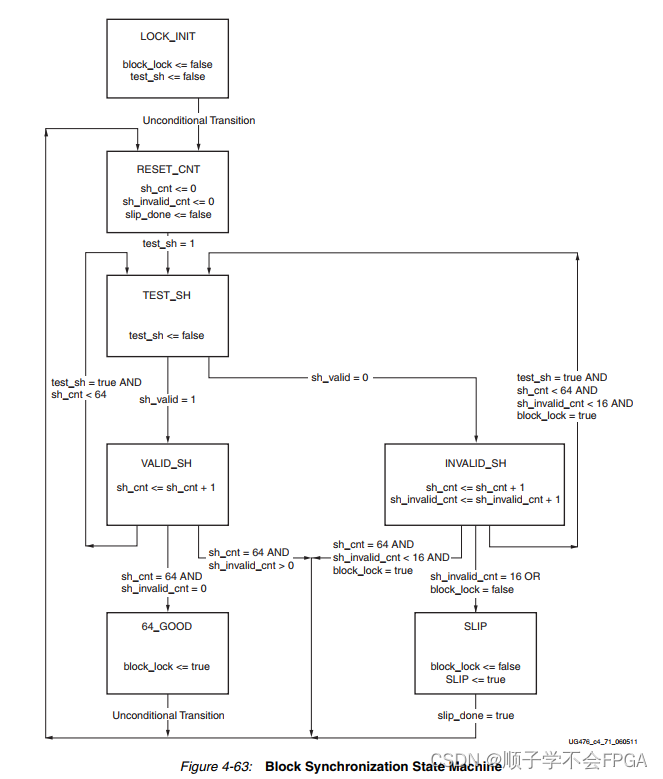

我们重点关注块锁定模块:

参考xilinx文章ug476

状态机通过跟踪有效和无效的同步头来工作。在复位时,块锁定被取消,状态为LOCK_INIT。下一个状态是RESET_CNT,其中所有计数器都被归零。同步头在TEST_SH状态中进行分析。如果头部有效,则在VALID_SH状态中递增sh_cnt,否则在INVALID_SH状态中递增sh_count和sh_invalid_count。对于图中显示的块同步状态机,sh_cnt_max和sh_invalid_cnt_max都是常量,分别设置为64和16。从VALID_SH状态开始,如果sh_cnt小于sh_cnt_max且test_sh为高电平,则下一个状态是TEST_SH。如果sh_cnt等于sh_cnt_max且sh_invalid_cnt等于0,则下一个状态是GOOD_64,并且从那里开始断言block_lock。然后进程再次重复,并将计数器清零。为了实现块锁定,状态机必须连续接收sh_cnt_max个有效同步头,而不会收到无效同步头。但是,当块锁定达到sh_invalid_cnt_max-1时,可以在sh_cnt_max个有效同步头内接收到无效同步头。因此,一旦锁定,要破坏锁定就更加困难。

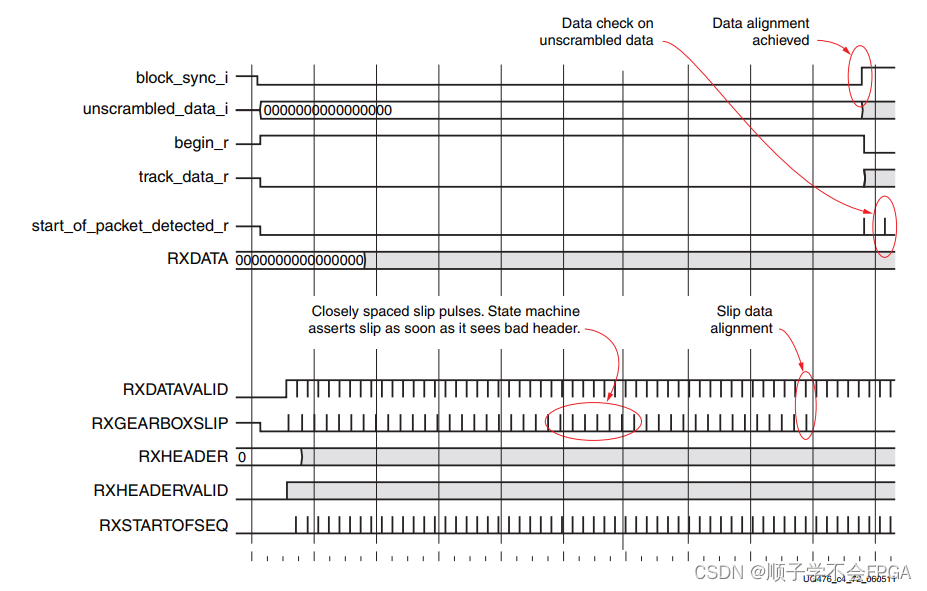

下图显示了由于在实现数据对齐之前多次收到无效同步头而导致的块同步状态机多次断言RXGEARBOXSLIP的波形。发出RXGEARBOXSLIP后,状态机在检查有效同步头之前等待32个RXUSRCLK2周期。

这篇关于GT收发器64B66B设计(1)IP核配置和example design的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!