违例专题

电路设计(15)——篮球赛24秒违例倒计时报警器的proteus仿真

1.设计要求 设计、制作一个篮球赛24秒违例倒计时报警器。要求: (1)具有倒计时功能。可完整实现从“24”秒开始依序倒计时并显示倒计时过程,显示时间间隔为1秒。 (2)具有消隐功能。当“24”秒倒计时至终点的瞬间,显示器字幕立刻自行消隐,消隐时间必须大于5秒。 (3)具有复位功能。无论显示器是显示倒计时的时间或消隐状态下,只要按

出现时序违例怎么解决-VIVADO

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 在工程应用中,经常会使用不同频率的时钟。 在不同条件下,出现时序违例。 在出现时序违例时,导致编译时间过长。 一、出现时序违例? 时序分析的测试程序: `timescale 1ns/1psmodule test_top_1 (input pri_clock, // 50M主时钟input sec_clk,i

时序违例在FPGA开发流程的分析及解决,结合实际工程

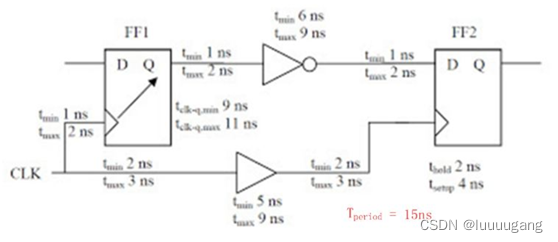

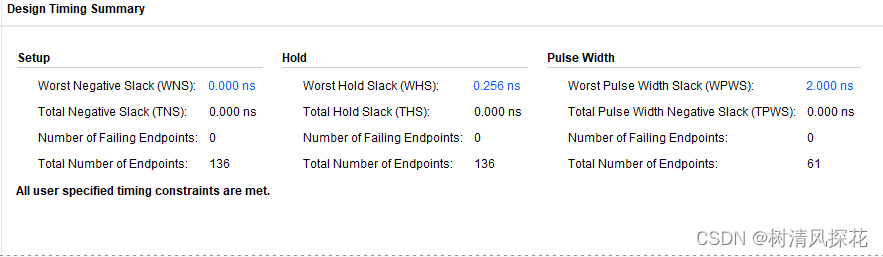

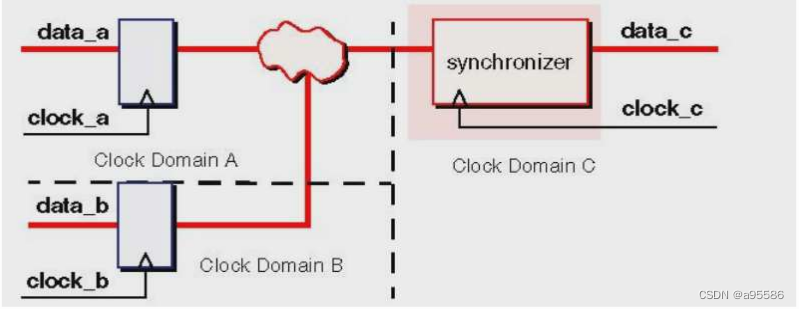

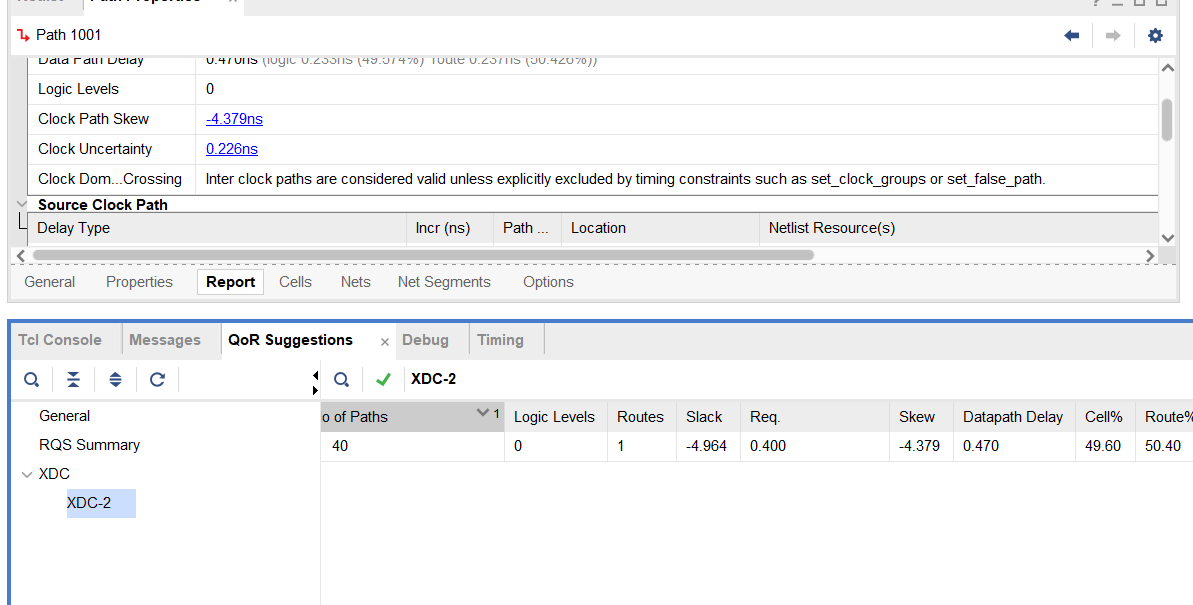

一.概述 时序违例的解决可以分为几个阶段,布局前,布线前,布线后。我们从这几个阶段对时序违例进行分析以及提出解决方法。(参考ug1292和ug949)。时序违例包括建立时间违例和保持时间为例,主要关注建立时间违例,保持时间违例是由于组合逻辑太短和时钟偏移造成的,可以通过布线时绕线以及BUFG解决。但是布线时过多的绕线会影响布线时对拥塞的解决程度。可以通过在布线前插入LUT(布局后使用phys_o