本文主要是介绍时序违例修复,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

建立时间违例修复

1.Tclk角度

2.Tcomb角度

1)流水线

2)重定时

3)关键信号后移

4)操作数平衡

5)树型加法器

6)消除优先级

3.Tnet角度

逻辑复制

4.Tco角度

5.Tskew角度

保持时间违例修复

1.Tcomb角度

2.Tskew角度

3.Tco角度

实例分析

建立时间与工艺、温度、电压、时钟周期有关。

保持时间与时钟周期无关。

建立保持时间是芯片本身的特性,它们的存在是触发器内部的特性,在屏蔽毛刺方面起到了一定作用。

建立时间违例修复

Tsu≤Tclk+Tskew-Tco-Tcomb-Tnet

1.Tclk角度

增大Tclk:降低时钟频率。很多产品等级是根据频率来分的,品质好的芯片频率高,价格贵。

2.Tcomb角度

减小Tcomb:

- 组合逻辑设计角度:流水线;重定时;关键信号后移;操作数平衡;树型加法器;消除优先级

- 物理版图角度:更换速度更快的标准单元(HVT-High Voltage Threshold;SVT-Standard Voltage Threshold);更换驱动能力更强的标准单元(X2,X4);更换阻值更低的金属以减少标准单元电路的负载和金属线网的延迟

1)流水线

流水线(pipeline):插入寄存器,将组合逻辑分解,使得分解后的延迟基本一致,降低Tcomb。相当于先插入寄存器,再重定时。面积换速度;提高最大时钟频率;保证吞吐量不变的情况下改善设计的时序性能。

PPA:性能 Performance、功耗 Power、面积 Area

流水线越深:追求性能,更高的主频

流水线越浅:追求功耗,小面积低功耗。

越深导致的问题:

1.以面积换速度,消耗更多的寄存器,面积开销大,功耗大。

2.流水线中的反压,流水线冲刷问题。分支预测失败,就会导致预取的指令全部作废,重新取指,造成功耗,造成性能损失。

处理器发展面临的挑战:频率墙、功耗墙、存储器墙、应用墙

2)重定时

寄存器平衡(重定时retiming):在不改变电路功能的情况下,将大块组合逻辑分解成小块组合逻辑,分布到寄存器之间,通过改变寄存器的位置来优化关键路径,减少组合逻辑最大延迟,从而改进最高时钟频率。寄存器重定时与流水线的区别是,重定时不增加寄存器个数,通过改变寄存器的位置来优化关键路径。而流水线是增加了寄存器个数。

3)关键信号后移

关键信号后移:关键输入应该在逻辑的最后一级提供,其中关键输入为芯片、Slice、或者LUT提供的延时最大的输入,比如在if...else if...链中,将关键信号放在第一级。

4)操作数平衡

操作数平衡 (加法树、乘法树):将串行逻辑并行优化处理,积之和变为和之积。例如Z=A* B *C * D ,利用括号进行操作树平衡Z=(A * B)*(C * D)。变成树状乘法器,树状加法器。

5)树型加法器

6)消除优先级

消除优先级:(又叫 代码结构平坦化技术)本身不需要优先级的地方,case代替if...else,使得顺序执行的语句变成并行执行。

3.Tnet角度

减小Tnet:提高工作电压;减小信号延迟;逻辑复制。

逻辑复制

逻辑复制:当信号扇出很大的时候,该信号到达各个目的逻辑节点的路径变得很长。通过对寄存器进行赋值来降低扇出。复制几个相同的寄存器来分担原来一个寄存器驱动模块的任务。逻辑复制的另一种方法,是在DC软件的约束文件中,设置max_fanout属性,一般将max_fanout设置为3,当实际设计中该信号的fanout超过了3,综合器就会就行自动优化。扇出过大会导致net delay线延迟过大,不利于时序收敛。

4.Tco角度

减小Tco:使用反应更快的D触发器

5.Tskew角度

增加Tskew:在时钟路径上插入buffer

保持时间违例修复

Th≤Tco+Tcomb-Tskew

保持时间与工艺、温度、电压有关。

1.Tcomb角度

增大Tcomb:插入buffer作缓冲器延时。

2.Tskew角度

减小skew: 做时钟树平衡,减小时钟延迟。

3.Tco角度

增大Tco:提高温度,降低电压。

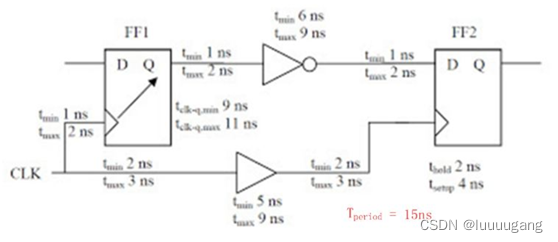

实例分析

Tsu= Tcycle + Tskew-T1 要使Tsu最小,则Tskew最小,T1最大。

Tsu(min) = Tcycle + Tskew(min) - T1(max) = Tcycle(=15) + Tskew(min)(=2+5+2-2) - T1(max) (=11+2+9+2) = 15+2+5+2-2-11-2-9-2 = 22- 24 < Tsetup 因此发生了setup violation

这篇关于时序违例修复的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!